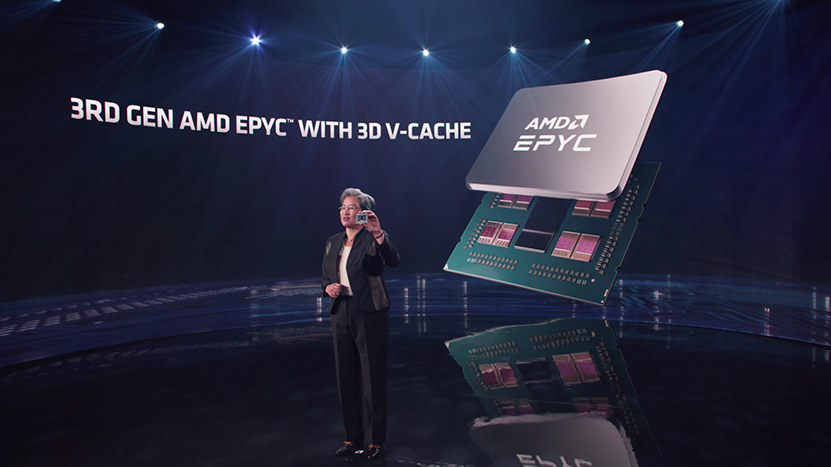

AMD on esitellyt aiemmin tänä vuonna 3D-paketointia V-Cache-välimuistisiruilla Ryzen-sarjan prosessorilla. Yhtiö on varmistanut, että uudet prosessorit tullaan julkaisemaan AM4-alustalle ensi vuoden alussa ja nyt niiden rinnalle esiteltiin Epyc-prosessorit V-Cache-välimuistilla.

AMD Accelerated Data Center Premiere -tapahtumassa esitellyt Milan-X-koodinimeä tottelevat prosessorit tunnetaan virallisesti ”3rd Gen AMD Epyc with AMD 3D V-Cache” -nimellä, eli AMD ei laske niitä uudeksi Epyc-sukupolveksi. Prosessoreissa on nykyisten 3. sukupolven Epycien tapaan maksimissaan 64 ydintä ja SMT-teknologian avulla ne voivat ajaa samanaikaisesti 128 säiettä. Välimuistin määrä on kuitenkin 3D V-Cachen myötä jotain ihan muuta ja siinä missä nykyisessä huippumallissa on 256 Mt L3-välimuistia, on tulevassa lippulaivassa sitä peräti 768 Mt; kunkin CCD-sirun päälle on lisätty 64 Mt:n välimuistisiru. Milan-X-prosessorit ovat suoraan yhteensopivia nykyisten SP3-alustojen kanssa, kunhan emolevylle on asennettu sitä tukeva BIOS.

Kolminkertaiseksi kasvanut L3-välimuisti kasvattaa AMD:n mukaan tiettyjen kuormien suorituskykyä jopa 50 %. Suurimmat parannukset löytyvät esimerkiksi numeerisesta virtausdynamiikasta (CFD, computational fluid dynamics), elementtimenetelmäanalytiikassa (FEA, finite element analysis), rakenneanalyyseissä ja elektronisessa suunnittelun automatisoinnissa. Käytännön esimerkkinä annettiin Synopsysin VCS-sovellus, jossa V-Cachella varustettu 3. sukupolven Epyc verifioi RTL-laitteistokuvauksia 66 % nopeammin, kuin V-Cacheton.

Epyc-prosessorit 3D V-Cache -välimuistilla tulevat saataville yhtiön partnereilta ensi vuoden ensimmäisellä neljänneksellä, mutta esimerkiksi Microsoft tarjoilee Azure-instansseja uusilla Epyceillä testikäyttöön jo nyt.

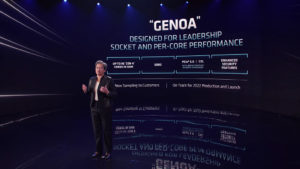

AMD:n toimitusjohtaja Lisa Su kertoi samassa yhteydessä myös tietoja yhtiön seuraavan sukupolven Zen 4 -arkkitehtuurista ja siihen perustuvista palvelinprosessoreista. Ne tullaan valmistamaan TSMC:n N5-valmistusprosessilla ja AMD:n viilausten kera sen kerrotaan tarjoavan kaksinkertaista tiheyttä, kaksinkertaista energiatehokkuutta ja 1,25-kertaista suorituskykyä nykyisten Epycien N7-prosessiin verrattuna.

Yhtiöllä on valmisteilla kaksi eri koodinimillä varustettua uuden arkkitehtuurin palvelinprosessoria. Genoa sisältää maksimissaan 96 Zen 4 -ydintä ja se tukee DDR5-muisteja sekä PCI Express 5.0- ja CXL-väyliä. Prosessoreiden näyte-erät ovat jo yhtiön asikkaiden käsissä ja ne tullaan julkaisemaan myyntiin ensi vuoden aikana.

Perinteisten Zen 4 -ytimien rinnalle tulee myös tiheys- ja energiatehokkuusoptimoidut Zen 4c -ytimet, jotka on suunniteltu ennen kaikkea pilvikäyttöön, jossa suuret määrät säikeitä ovat ensiarvoisen tärkeitä. Bergamo-koodinimellisissä prosessoreissa tulee olemaan maksimissaan 128 Zen 4c -ydintä ja ne tulevat olemaan alustayhteensopivia Genoa-prosessoreiden kanssa, tukien myös samoja väylä- ja muististandardeja. Bergamo-prosessorit saapuvat markkinoille näillä näkymin vuoden 2023 ensimmäisellä puoliskolla.

Lähde: AMD

Pelikäytössä arvioivat 15%, eiköhän niitä benchejä alkuvuodesta nähdä, viimeistään kun ne julkaistaan myyntiin

AMD Gives Details on EPYC Zen4: Genoa and Bergamo, up to 96 and 128 Cores

http://www.anandtech.com

Serveripuolelle hyviä uutisia. Katsellaan miten Intelin osasto ei pysty samaan.

Lisa Su:han ilmoitti tuolla videolla että ovat saanneet Metan joukkoihinsa. Se on kuitenkin kaikki pois Inteliltä jatkossa. Niin ja toivottavasti saadaan aikanaan Bergamoa myös sinne porin konttorille.

Itse oletan lippulaivamalleja. Se ratkaisee onko hintaa 20% vai 50% lisää normi Zeniin verrattuna.

Mahtaakohan TRX40 saada 3D-kakkuset ripperinsä kanssa, kun epyccejä valuu tontille?

Tämän hetkinen oletus on että seuraava TR eli Chagall tulee tavallisilla Zen3-siruilla

Sepä se, ja se on vähän valitettavaa. Saattaa olla että 3960X jä vielä toviksi käyttöön. Chagall ei ATM ole järkevä päivitys itselle.

Onko tästä jotain vuotoja tai faktaa? Pelikäytössä 5600X on kuitenkin edelleen erittäin suosittu ja pätevä prossu, joten olisi harmi mikäli siitä ei nähdä kakutettua versiota.

Itsellä ei ole kiirettä, parin vuoden päästä voi ostella "6800X" prossun käytettynä parilla satkulla, kunhan silloin sattuu saamaan näyttiksiä järkevillä hinnoilla, uutena tai käytettynä. Pelkällä prossun vaihdolla ei tee mitään pelikäytössä, jos näyttis on se mikä laahaa menoa.

Eiköhän AMD osaa homman laskea mitä malleja kannattaa tuoda.

Tuo mikä on teknisesti edukkainta on vähän sellaista yksipuolista laskentaa.

Tuleeko tästä uusi CPU pula päälle GPU pulan lisäksi.

Vai oisko raptoreum kumminki?

Nyt ihmetyttää, että mitä sieniä siellä on oikein syöty; TSMC itse lupaa vain n. 1.7x tiheysparannusta logiikalle välillä N7 => N5 (SRAMille vähemmän) ja kaikki todelliset synteesitulosluvut mitä olen nähnyt näyttää vielä tästäkin selvästi huonompaa tiheysparannusta.

Vai onko AMD aiemmin käyttänyt prosessoripiireillään tuon N7-prosessin kanssa kirjastoja, joista puuttuu tiheimmät komponentit kokonaan, mutta nyt N5n kanssa sen tiheimmät komponentit on käytössä? (tämä selittäisi sitä, miksi esim. se erillinen kakkupiiri on tiheämpi kuin se CPU-piirillä oleva kakku)

Joo näyttää olevan Raptoreum muistinkin väärin jostain mielen syövereistä tuo tuli kun molemmat alkaa R kirjaimella.

Kryptojen louhijoita kiinnostaa nyt Ryzen-suorittimet L3-välimuistin vuoksi – kohta näistäkin on pulaa? – Muropaketti.com

muropaketti.com

Vastaanpa itselleni:

Oma veikkaus on nyt, että tuo tiheyden n. tuplaus pätee Zen 4D:hen (matalakellomalli), ei normaaliin työpöytä-zen4een. Ja logiikan tiheysparannuksewta noin puolet tulee valmistustekniikasta, puolet mm. selvästi pienemmästä kellotaajuustavoitteesta logiikkasynteesille (jolloin voidaan käyttää tiheämpiä, hitaampia komponenttejä) sekä pienemmistä välimuisteista yms.

Muistaakseni sanoivat nimenomaan että kyse on prosessin parannuksista, ei minkään tietyn tuotteen