Intel on julkaissut Architecture Day 2020 -tapahtuman tiimoilta nauhoitetun videon sekä joukon dioja. Architecture Day -tapahtumassa paljastettiin muun muassa yksityiskohtia Tiger Lake -prosessoreista, tulevista Cove-ytimistä sekä Xe-arkkitehtuurista. Käymme tässä uutisartikkeleiden sarjassa läpi mielenkiintoisimmat yksityiskohdat julkistuksista ja ensimmäisessä keskitytään Inteliin itseensä sekä valmistusteknisiin päivityksiin.

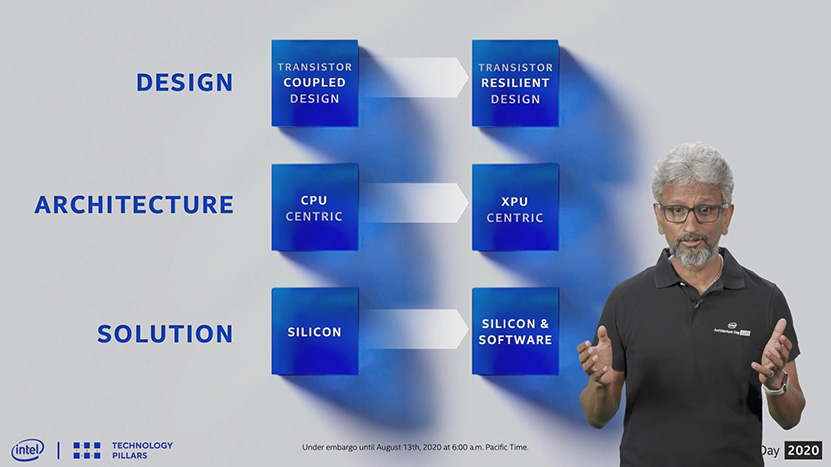

Intelin pääarkkitehti Raja Kodurin isännöimässä videossa käytiin ensimmäisenä läpi muutoksia yhtiön lähestymisessä kehitystyöhön. Aiemmin Intel on suunnitellut sirunsa yhdelle tietylle prosessille äärimmäisen tiukasti, mikä auttaa saamaan prosessista enemmän irti, mutta on samalla erittäin haavoittuva erilaisille ongelmille, kuten 10 ja 7 nanometrin prosessien takkuamisen kanssa on nähty. Jatkossa yhtiö tulee kehittämään arkkitehtuurejaan mahdollisimman prosessiriippumattomina, jotta eri IP:t voidaan siirtää tarpeen mukaan nopealla aikataululla eri prosesseille, tarvittaessa myös kilpailevien puolijohdevalmistajien kuten TSMC:n prosessille.

Toinen muutos koskee siirtymistä vanhasta keskusprosessorikeskeisestä (”CPU”) lähestymistavasta kiihdytinkeskeiseen lähestymiseen (”XPU”), jossa eri tehtäviin hyödynnetään entistä enemmän siihen erikoistunutta rautaa prosessoreiden sisällä. Kolmas ja viimeinen muutos on ongelmien ratkonta pelkkien sirujen sijasta myös ohjelmistopuolella. Tähän liittyy muun muassa yhtiön OneAPI-rajapinta sekä uusi HPC-käyttöön optimoitu Linux-pohjainen mOS-käyttöjärjestelmä.

Intel kertoi myös uutta prosessirintamalta. Aiemmin 10nm+-nimellä tunnettu prosessi on julkistettu nyt virallisesti ja sen nimi on vaihdettu samalla 10nm SuperFin -prosessiksi tai lyhyemmin 10SF:ksi. Uusi nimi juontaa juurensa merkittäviin muutoksiin sekä itse FinFET-transistorien rakenteessa, sen ohentuneissa 30 % pienemmän resistanssin mahdollistavissa metallikerroksissa sekä Super MIM -kondensaattorissa (Metal-Insulator-Metal), jonka kerrotaan mahdollistavan viisinkertaisen kapasitanssin aiempaan nähden. 10SF-prosessin jälkeen vuorossa tulee olemaan entisestään paranneltu 10nm Enhanced SuperFin- eli 10ESF-prosessi.

Paketointiteknologioiden puolella Intelillä on työn alla tällä hetkellä seuraavan sukupolven 3D-paketointiteknologia, jonka on tarkoitus kutistaa sirujen välisten kontaktien koko Foveroksen 25 – 50 mikronista alle 10 mikroniin. Teknologia tulee hyödyntämään sirujen liitännässä uutta Hybrid Bonding -teknologiaa, joka mahdollistaa yleisesti käytettyä lämpöön ja paineeseen perustuvaa liitäntää pienemmät kontaktit, mikä puolestaan tarkoittaa paitsi enemmän kontakteja pinta-alaa kohden, myös yksinkertaisempaa rakennetta sirujen kommunikaatiopintoihin ja pienempää tehohävikkiä.

Lisäksi yhtiö esitteli Co-EMIB-teknologian, mikä yhdistää samaan paketointiin Foveros-3D-paketoinnin ja EMIB-sillat 2,5D-paketointiin. Uusi Omni-Directional Interconnect eli ODI puolestaan vapauttaa 3D-paketoinnissa sirujen koon suhteessa toisiinsa, kun ylempien kerrosten sirut voivat jatkossa ”roikkua” yli alempien sivujen reunojen. Yli menevää reunaa voidaan hyödyntää ODI:lla esimerkiksi ylemmän sirun virransyötössä järeämmin kontaktein, kuin mitä toisen sirun läpäisevät TSV:t mahdollistavat (Through-Silicon-Via)

Lähde: Intel

Mikähän mahtaa olla tämän suunnittelutavan seuraus sitten tulevaisuudessa? Intelkö ei saisikaan prosesseista kaikkea irti? Näkyisikö tämä sitten heikentyneenä suorituskykynä / heikentyneenä energiatehokkuutena?

Mäkin mietin samaa, mutta oma arvaus tästä on seuraavanlainen: Hiukan menetetään potentiaalista suorituskykyä, jota voisi saada valmistusprosessista irti, mutta hyödyt ovat haittoja suuremmat. Juuri valmistusprosessin ja arkkitehtuurin tiukka linkitys on johtanut siihen, että Intel on ollut jumissa vuosikausia Skylake-johdannaisten kanssa, kun työpöytäpuolelle ei ole saatu uudempaa valmistusprosessia.