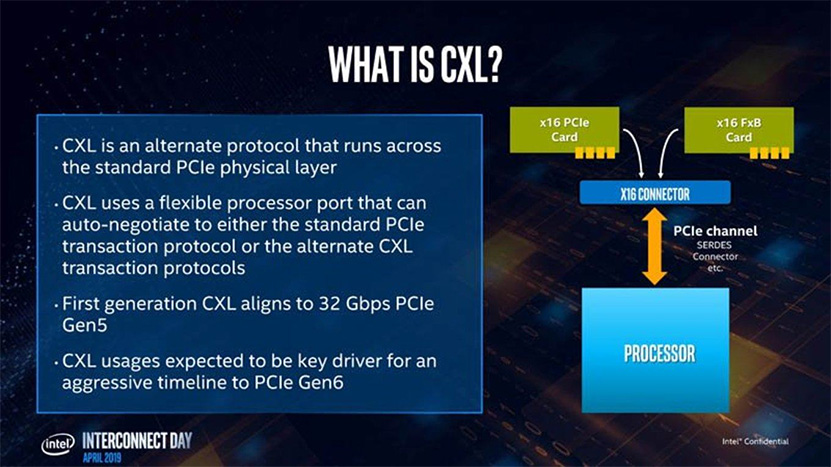

Intel julkisti hiljattain uuden Compute Express Link- eli CXL-väylän, mutta moni yksityiskohta sen toteutuksesta jäi hämärän peittoon. Nyt Intel on kertonunt lisää uudesta väylästä ja sen toteutuksesta Interconnect Day -tapahtumassaan.

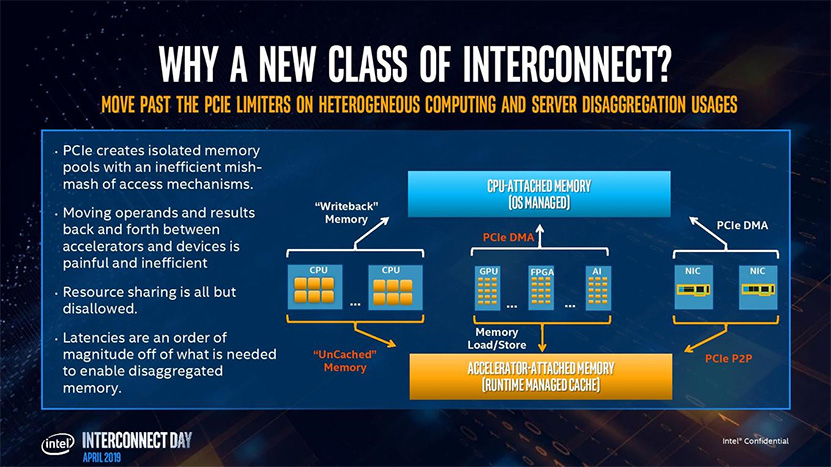

Intelin Compute Express Link pohjautuu PCI Express 5.0 -väylään fyysisesti, mutta yhtiön omilla protokollilla. Eri protokollien käyttö mahdollistaa esimerkiksi matalammat latenssit sekä koherentit yhteiset välimuistikoherentit muistialueet eri laitteiden välille, toisin kuin PCI Express. Lisäksi PCIe:n latenssit ovat selvästi korkeammat, kuin mitä CXL:n protokollien käyttö mahdollistaa.

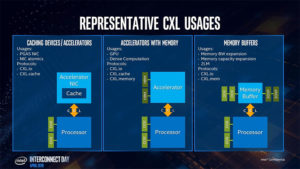

Intelin mukaan CXL-väylää tukeva prosessori tunnistaa automaattisesti PCIe-väylän toisessa päässä olevan laitteen kyvyt ja valitsee sen mukaan joko PCI Express- tai CXL-standardin mukaisen protokollan liikenteelle. CXL-protokolla koostuu puolestaan kolmesta aliprotokollasta, CXL.io:sta, CXL.cachesta ja CXL.memorystä.

CXL.io on vastuussa nimensä mukaisesti erilaisista I/O-mekanismeista sekä laitteiden tunnistamisesta, konfiguroinnista ja vastaavista. CXL.cache-protokollaa käytetään kun väylään liitettty laite käyttää prosessorin päässä olevaa muistialuetta ja CXL.memoryä kun prosessori käyttää väylän toisessa päässä olevan laitteen muistialuetta.

Asiasta kiinnostuneille suosittelemme esimerkiksi Serve The Home -sivuston artikkelia aiheesta.

Sellainen pikkuvirhe, että kyllä PCI Expressissäkin kaikkien väyläään kytkettyjen laitteiden välillä on yhteinen muistavaruus; Ei se väylä voisi toimia, jos ei olisi yhteistä muistiavaruutta, jonka osoitteissa määritellään se, minne data on menossa/mistä se on tulossa.

Ero on vaan siinä, että PCI Express ei ole välimuistikoherentti, CXL on välimuistikoherentti.

Korjataas

Sanos muuten miten tuo vertautuu OpenCAPIin?

Pikavilkaisulla vaikuttaisi hyvin suoralta kilpailijalta, että tekee pääosin ihan saman asian.

Ehkä vähän Intelillä NIH-syndroomaa tässä, ei voi mennä mukaan avoimeen standardiin vaan pitää tehdä oma kilpaileva.

Onlko tuossa se idea että kun PCIE:n protokolan täytyy ottaa huomioon se että väylä voi olla fyysisesti suhtellisen pitkä ja siinä voi olla useampikin fyysinen liitin niin siinä täytyy olla enempi virheen sietorutiineja mutta tuo CXL on tehty fyysisesti lyhempää ja paremmilla liitimillä (prosesorikannan tyylisiä ei PCIE liitimien tyylisiä) varustettua väylää silmälläpitäen niin sen ei tarvi sisältää yhtäpaljon virheensietoa ja siten siitä saadaan tehokaampi?