TSMC pitää parhaillaan 26th Technology Symposium -tapahtumaansa, jossa se muun muassa kertoo omista tulevaisuuden suunnitelmistaan. Tapahtumassa on kerrottu lisätietoa muun muassa lähitulevaisuuden prosesseista sekä katsaus kauemmas tulevaisuuteen.

TSMC:n 5 nanometrin N5-valmistusprosessi on siirtynyt jo massatuotantovaiheeseen ja sen odotetaan saapuvan markkinoille ensimmäisenä Applen järjestelmäpiirien mukana. Huawein oli tarkoitus olla toinen N5-prosessin ensimmäisistä käyttäjistä, mutta TSMC on jo ilmoittanut lopettaneensa tilausten vastaanottamisen yhtiöltä ja toimittavansa viimeiset järjestelmäpiirit sille syyskuussa. Toistaiseksi ei ole tietoa, ovatko nuo viimeisen erän järjestelmäpiirit valmistettu N5:llä vai jollain muulla prosessilla.

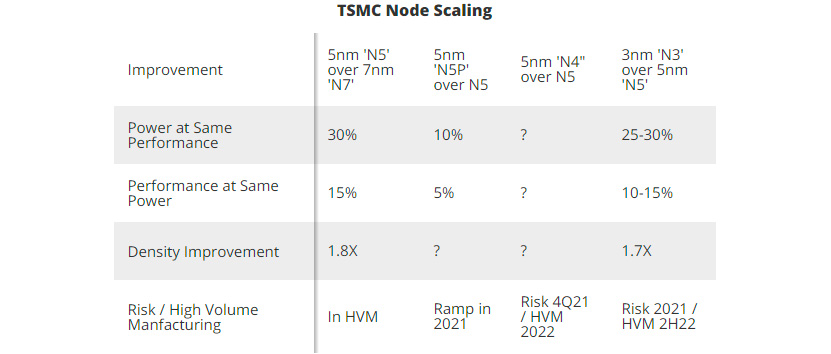

EUV-litografiaa entistä laajemmin hyödyntävän N5-prosessin kerrotaan tarjoavan 15 % parempaa suorituskykyä samalla kulutuksella tai 30 % pienempää tehonkulutusta samalla suorituskyvyllä, kuin N7-prosessi. Lisäksi se nostaa transistoritiheyttä parhaimmillaan 80 %. Prosessin vikatiheyden kerrotaan pienentyvän nopeammin kuin N7-prosessilla.

N5:n lisäksi yhtiöllä on työn alla ainakin kaksi muuta 5 nanometrin prosessia, N5P ja N4. N5P tulee tuotantoon ensi vuonna ja se tulee tarjoamaan 5 % lisää nopeutta ja 10 % parempaa energiatehokkuutta N5:een verrattuna. N4 tulee parantamaan tästä entisestään ja se on suunnattu helpoksi kehitysaskeleeksi N5-prosessista. Prosessin suorituskykylukemista ei kuitenkaan kerrottu vielä tässä vaiheessa mitään. N4 siirtyy riskituotantoon ensi vuoden lopulla ja massatuotantoon 2022.

Seuraava täysin uuden sukupolven prosessi tulee olemaan 3 nanometrin N3. Yhtiön mukaan sen kehitys sujuu suunnitellusti ja prosessin odotetaan tarjoavan parhaimmillaan 15 % lisää suorituskykyä tai 30 % pienempää tehonkulutusta N5-prosessiin verrattuna. Transistoritiheys tulee puolestaan paranemaan parhaimmillaan 70 %. Riskituotanto N3-prosessilla on tarkoitus aloittaa ensi vuoden kuluessa ja massatuotantoon sen on tarkoitus päästä N4:n tavoin vuonna 2022.

Paketointiteknologioiden puolella TSMC esitteli 3DFabric-järjestelmän. 3DFabric yhdistää yhteen pakettiin yhtiön System on Integrated Chips (SoIC)-, Chip on Wafer on Substrate- (CoWoS) ja Integrated Fan-Out -teknologiat (InFO). Se mahdollistaa saman paketointiteknologian avulla sekä sirujen pinoamisen päällekkäin että rinnakkain yhdessä paketissa, mikä helpottaa esimerkiksi HBM-muistien, IO-sirujen ja analogisten sirujen kuten radioyksiköiden paketointia yhteen kokonaisuuteen 3D-pinottujen logiikkasirujen kanssa.

Tom’s Hardwaren mukaan TSMC on kertonut tapahtumassa lisäksi viitteitä siitä, mitä on odotettavissa 3 nanometrin N3-prosessin jälkeen. Raportin mukaan TSMC:llä on kehitystyön alla erilaisia nanosheet- ja nanowire-teknologioita, 2D-transistorit sekä uusien materiaalien kuten hiilinanoputkien hyödyntäminen. TSMC:n kerrotaan löytäneen jo useampia potentiaalisia materiaaleja, jotka voisivat sopia piin korvikkeeksi ja mahdollistaisivat skaalautumisen alle yhden nanometrin kanavaleveyksiin.

Lähde: TSMC, Tom’s Hardware

Hyvin ovat saaneet kehityksen pysymään nopeana eikä kompuroineet kuten tietyt siniset.

‘Better Yield on 5nm than 7nm’: TSMC Update on Defect Rates for N5

http://www.anandtech.com

Kirpaissee Inteliää aika rankasti.

Eikös ne Intelin ongelmat ole tulleet enimmäkseen siitä että eivät 10nm kiviä saa kulkemaan samalla tavalla kuin 14nm?

Ja kun IPC ei ole pahemmin kehittynyt, niin eivät oikein voi julkaista uusia hitaampia prossuja vanhojen tilalle.

Eihän nuo TSMC (12nm ja 7nm) prosessikaan tunnu kauhean kovia kelloja kestävän.

Jep kellot tulee vastaa, mutta jos virta kulutus pienenee ja saadaan ipc korkeammalle käyttämällä enemmän piirejä, niin toimii sekin.

Kerta 5nm on noin hyvässä iskussa, on täysin mahdollista, että ensi vuonna nähdään jo Hopperit ja AMD:iltakin jokin uusi näyttis sukupolvi.