AMD on tuonut tänä keväänä myyntiin ensimmäiset 3D V-Cache -välimuistilla varustetut prosessorit. Yhtiö on esitellyt pinottavaa välimuistiarkkitehtuuriaan useissa dioissa, mutta nyt toteutusta on päästy katselemaan myös lähemmin käytännössä.

3D V-Cachen ensiesiintymisestä ehti vierähtää liki vuosi, ennen kuin prosessorit vihdoin saapuivat markkinoille. Myös itse prosessoreiden ja pinottavan välimuistisirun toteutus on ehtinyt muuttumaan matkan varrella melkoisesti.

Kun toimitusjohtaja Lisa Su esitteli prototyyppiprosessoria 3D V-Cachella ensimmäistä kertaa, oli välimuistisiru selvästi erotettavissa prosessorista ja täytepiistä. AMD:n diojen mukaan asiassa ei ollut mitään erikoista, sillä rakenne vastasi diojen kuvausta, vaikka niissäkin oli esiintynyt ainakin kahdenlaisia pii”shimmejä” välimuistisirun ympärille. Poikkeuksen tähän tekee yksi tietty ISSCC:ssä esitetty dia, jossa myös välimuistisirun päällä on kerros piitä tukemassa rakennetta.

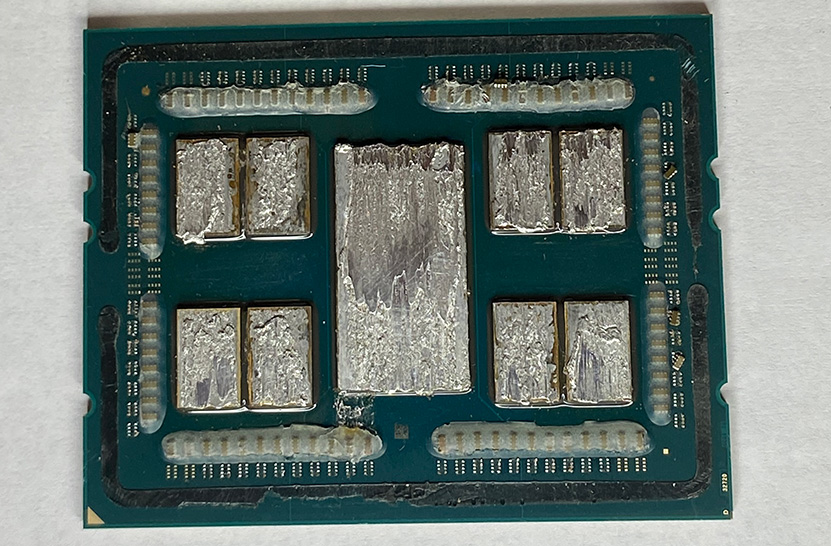

Puolijohteiden paketointiteknologioiden parissa työskentelevä Tom Wassick on saanut käsiinsä Epyc 7473X -prosessorin, eli Milan-X-koodinimellisen Epycin 3D V-Cache -välimuistilla. Wassick korkkasi prosessorin nopeasti ja selvitti mikä lopullisten prosessoreiden todellinen rakenne on. Korkkauksen jäljiltä oli selvää, että ISSCC:n dian kuvaus pitää paikkansa, aiemmat AMD:n diat eivät; välimuistisirun päällä on vielä yksi piikerros tukemassa rakennetta. Wassick aikoo jatkaa prosessorin paloittelua selvittääkseen tarkemmin sirun rakenteen ”kannen” alla. Kuten kuvista näkee, paketoinnin rakenteen selvittämisen jälkeen Wassickin Milan X -prosessorista on enää turha odottaa soivaa peliä.

Lähde: Tom’s Hardware, Tom Wassick @ Twitter

Eli alempia tasoja on ohennettu lisää?

Mutta kyllähän tuollaisen hampurilaismallin luulisi olevan tukevampi eikä lämpötilavaihtelu pääse niin pahasti irrottelemaan osia toisistaan.

5900X3D olis kyllä kiinnostanut jossain määrin. Mutta tuo 5800X3D ei kyllä nappaa koska 8 core ei vaan riitä vaan pitää olla se 12 vähintään:)