Uutisoimme viime viikolla Intelin tulevasta Ponte Vecchio -GPU:ta koskevasta vuodosta. Nyt Intel on esitellyt XeHPC:ksi kutsutun arkkitehtuurin virallisesti ja paljastanut samalla tarkempia tietoja Project Aurora -supertietokonenoodeista. Samalla pitäisi miettiä uusi suomennos GPU:lle, sillä grafiikka- tai laskentapiiristä puhuminen ei toimi radikaalisti nykytarjonnasta poikkeavan toteutuksen kuvaamiseen.

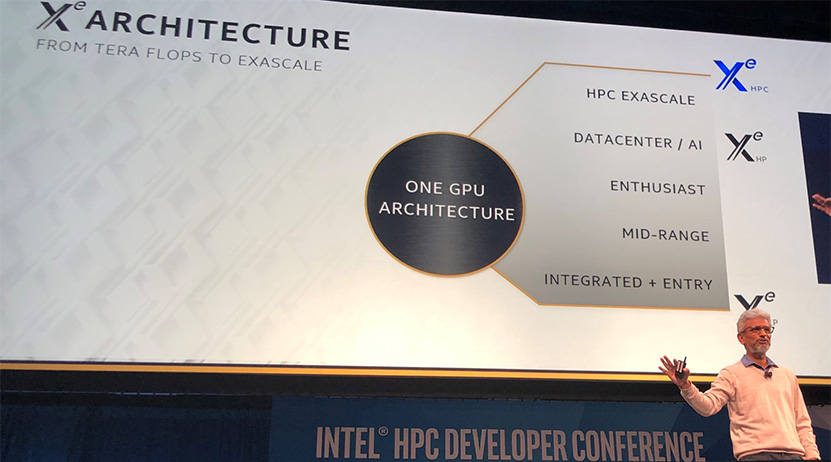

Intelillä nykyään työskentelevän grafiikkaguru Raja Kodurin mukaan Intel suunnitteli alun perin tuovansa Xe-arkkitehtuurista markkinoille kaksi mikroarkkitehtuurivarianttia, XeLP:n ja XeHP:n, mutta päätti lopulta lisätä joukkoon vielä kolmmanen eli XeHPC:n, koska vain siten yhtiö voi kattaa koko skaalan integroiduista grafiikkaohjaimista aina eksaluokan HPC-laskentaan asti. XeLP:n kerrotaan skaalautuvan järkevästi 5 – 20 wattiin ja periaatteessa se kykenisi skaalautumaan 50 wattiin asti, mutta suorituskyky suhteessa tehonkulutukseen laskisi merkittävästi, joten yli 20 watin kulutus on pyhitetty XeHP:lle ja XeHPC:lle. XeHPC on optimoitu enemmän laskentakäyttöön ja HP grafiikan piirtämiseen.

XeHP:n ja XeHPC:n käytännön toteutusten eroista ei ole kuitenkaan kerrottu mitään ja Intelin esittely koskee vain XeHPC-arkkitehtuuria. Käytämme tässä uutisartikkelissa jatkossa nimeä Xe kuvaamaan XeHPC:ta helppouden nimissä. Valitettavasti Kodurin esitystä ei ole saatavilla videona ja tiedot ovat joiltain osin hieman epäselviä tiettyjen yksityiskohtien toteutuksen osalta.

Xe-arkkitehtuuri tukee vaihtelevan levyisiä vektorilaskuja ja se kykenee toimimaan sekä SIMD (Single Instruction, Multiple Data), SIMT (Single Instruction, Multiple Threads) että SIMD+SIMT-tiloissa tarpeen mukaan. Arkkitehtuuri kykenee skaalautumaan Kodurin mukaan tuhansiin Execution Unit -yksiköihin asti, mutta yhden sirun yksiköiden määrä jäi vielä arvoitukseksi. Mukana on myös matriisilaskuihin erikoistuneita yksiköitä, jotka tukevat INT8-, BFloat16- ja FP16-tarkkuuksia. Yhden EU:n FP64-suorituskyvyn kerrotaan peräti nelikymmenkertaistuneen.

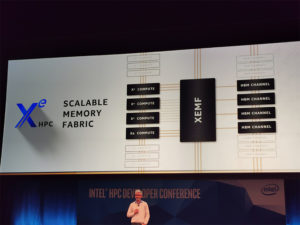

Laskentayksiköiden ja HBM-muistikanavien välistä löytyy XEMF- eli Xe Memory Fabric -muistiohjain, joka tukee täysin koherenttia muistia myös muiden grafiikkapiirien ja prosessoreiden kanssa. Vuodossa mainittu ”erittäin korkea välimuisti”, jossa korkeuden merkitys jäi epäselväksi, on nimeltään Rambo-välimuisti. Rambo on Kodurin mukaan erittäin suurikokoinen ja sen kerrotaan mahdollistavan korkean suorituskyvyn myös erittäin suurilla matriiseilla. Välimuistikoherentti Rambo on sekä Compute-sirujen että prosessorin käytettävissä.

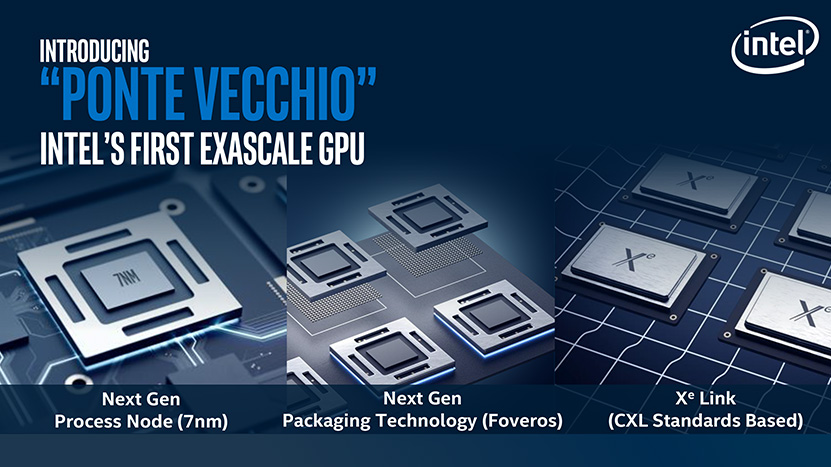

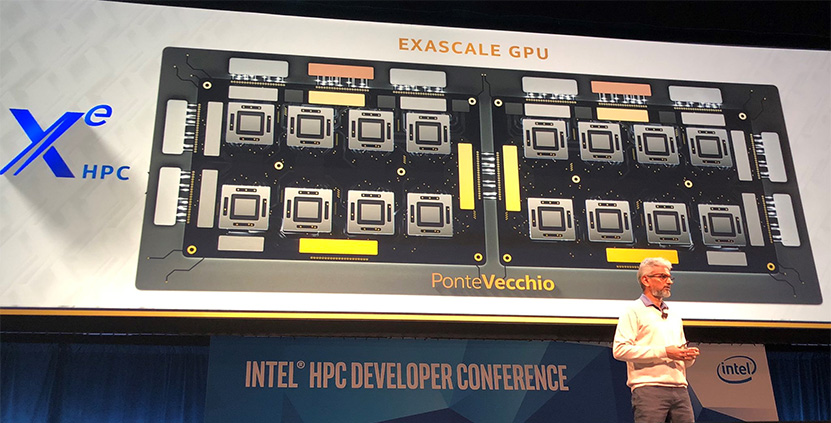

Intel tulee hyödyntämään Xe:n kanssa 7 nanometrin valmistustekniikkaa ja Foveros-paketointia sekä EMIB-siltoja. Intelin kaavioiden mukaan yhdessä Xe-noodissa olisi kahdeksan Compute-sirua neljä Rambo-sirua, jotka hyödyntävät Foveros-paketointia. HBM-muistit puolestaan on yhdistetty tähän kokonaisuuteen EMIB-silloilla. HBM-muistikanavien tarkka lukumäärä on osittain arvailujen varassa, mutta ilmeisesti niitä olisi yhteensä neljä per noodi. Ponte Vecchio -GPU rakentuu puolestaan kahdesta tällaisesta Xe-noodista.

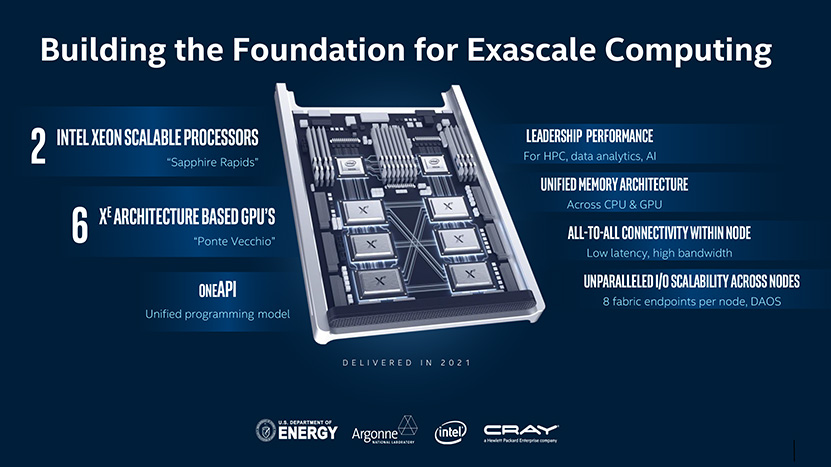

Project Aurora -supertietokonenoodeissa on kaksi Sapphire Rapids -arkkitehtuuriin perustuvaa Xeon Scalable -prosessoria ja kuusi Ponte Vecchio -GPU:ta, jotka keskustelevat keskenään Xe Link -sirun välityksellä. Xe Link hyödyntää CXL- eli Compute Express Link -väyliä ja se mahdollistaa yhteisen muistin kaikkien kuuden grafiikkayksiköiden välille. Koko Project Aurora -noodin muistiavaruus on jaettu yhteiseksi jokaisen GPU:n ja prosessorin kesken ja koodia sille kirjoitetaan yhteisellä OneAPI-rajapinnalla. Project Aurora -noodit tulevat saatavilla vuoden 2021 aikana. Sen avulla Intel aikoo saavuttaa parhaimmillaan yli 500-kertaisen suorituskyvyn tämän päivän vastaaviin noodeihin nähden.

Lähteet: Intel Graphics @ Twitter, AnandTech

Arkkitehtuuri on kyllä niin kaukana perus-PC:stä, että vähän vaikea hahmottaa, että miten kovaa rautaa tämä on omassa kategoriassaan.

Ettei olisi kiuas?

Nyt kyllä tiedä miten tuo fp64 laskenta EU:ta kohden voi 40 kertaistua, kun nykyisissä se on neljäsosa fp32 laskentatehosta. Maksimi fp64:nen kuiten on puolet fp32 laskentatehosta, eikä tuota erotusta saa edes kelloilla paikattua. Vertailevat taas jotain omenoita appelsiineihin.

Ei 1:2 mikään maksimi ole, se riippuu ihan piirin rakenteesta ja mitä mitkäkin yksiköt osaavat tehdä (esimerkiksi NVIDIA on käyttänyt dedikoituja FP64-yksiköitä)

Noissa ei välttämättä ole paljon muuta samaa kuin nimi. Tuon EU:n sisällähän on voitu vetää vaikka mitä uusiksi. Tai sitten vain uudelleen järjestellä osa, ja muokata osaa ja lisätä eriliasia yksiköitä suhteessa muihin. Näistä julkaistuista tiedoista ei ihan mahdottomia voi päätellä.

Niin noh yleensähän sille fp32:llekkin on käyttöä. Eli jos kerran laittaa fp64 yksiköitä, niin sama laittaa sellaisia yksiköitä jotka pystyy maksimimäärään tarkkuuksiaan eli 1xfp64, 2xfp32, 4xfp16. Keplerissä oli muistaakseni erilliset fp64 yksiköt suhteessa 1:3, selittivät sitä tuolloin tilan säästöllä. En kyllä kuollaksenikaan muista pystykö nuo fp64 yksiköt noissa ajamaan 2xfp32 laskuja, mutta compute modea se kuiten piti vaihtaa että ne sai käyttöön.

Eivät pystyneet eikä niitä voinut käyttää samanaikaisesti FP32-yksiköiden kanssa ulkomuistista. Pointti kuitenkin pysyy, eli 1:2 ei ole mikään maksimi millekään vaan kaikki riippuu piirin rakenteesta

Äkkiä tulee mieleen että Aurora on suora kilpailija DGX:lle NVIDIA DGX Station

Toisaalta XEMF kuulostaa aivan HBCC:ltä ja kortti itse kuin 3DFX V5 6000 steroideilla. Vielä jos OpenAPI on käytännössä joku HSA speksin mukainen viritelmä niin uutuusarvo julkistuksilla lähenee nollaa.