Cadence saattaa olla isolle yleisölle verrattain tuntematon nimi. Parhaiten se tunnetaan kenties Tensilica-sarjan DSP-siruistaan (Digital Signal Processor), mutta yhtiö on vahvasti mukana myös muistipuolella.

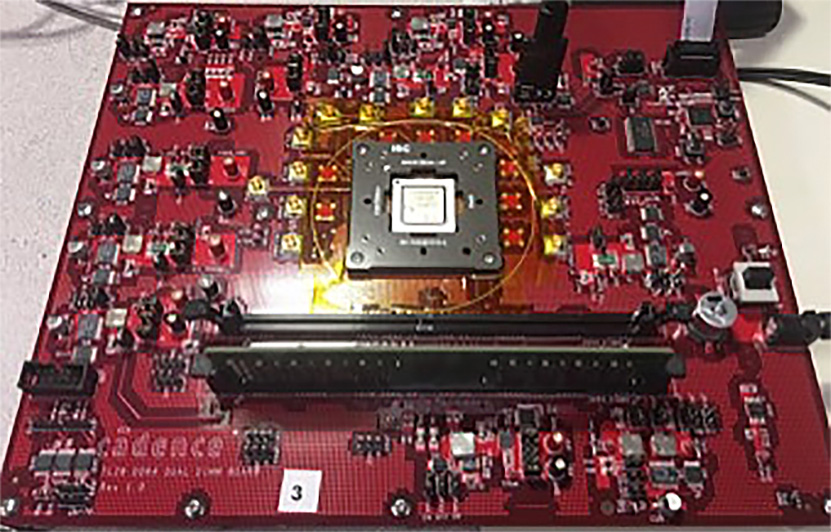

Nyt Cadence on julkaissut blogin, jonka mukaan DDR5 tulee saapumaan markkinoille vielä tämän vuoden aikana huolimatta siitä, että JEDEC ei ole julkaissut vielä edes lopullista versiota DDR5-standardista. Yhtiö tekee läheistä yhteistyötä JEDECin ja sen eri toimijoiden kanssa, mikä mahdollistaa muistien ja ohjainten kehityksen jo ennen lopullisen standardin viimeistelyä. Yhtiö kehitti maailman ensimmäiset 7 nanometrin DDR5-testisirut jo liki kaksi vuotta sitten.

Cadencen mukaan sen DDR5-muistiohjain ja PHY-moduulit (Phsyical Layer, eli muistiohjaimen fyysiset liitännät) ovat löytäneet tiensä jo yli tusinaan eri siruun. Yhtiö odottaa ensimmäisten muistien ja niitä hyödyntävien tuotteiden saapuvan markkinoille jo tämän vuoden aikana. Isommalle yleisölle tutummilta nimiltä kuten AMD:lta ja Inteliltä on tulossa ensimmäiset DDR5-muisteja käyttävät sirut näillä näkymin ensi vuonna Genoan (Zen 4) ja Sapphire Rapidsin muodossa, mutta toistaiseksi ei ole varmuutta käyttävätkö ne juuri Cadencen muistiohjaimia.

Ensimmäiset muistit tulevat toimimaan DDR5-4800-nopeudella, jonka jälkeen Cadence odottaa ainakin virallisten JEDEC-standardien osalta hyppyjen 5200- ja 5600-nopeuksiin tapahtuvan 12 – 18 kuukauden sykleissä. Todellisuudessa markkinoille myyntiin tulevat muistit voivat tukea selvästi korkeampiakin nopeuksia, kuin JEDECin virallinen standardi. Kapasiteetin puolella muistisirut lähtevät 16 gigabitistä ja kasvavat sen jälkeen 24 ja 32 gigabittiin. 24 Gigabitin muistisirujen myötä markkinoilla tullaan näkemään myös totutusta poikkeavia 24 ja 48 gigatavun muistikampoja.

Mutta 24 gigatavun kammalla rajoitutaan yhteen muistikanavaan, mikä vie puolet kaistasta, ja 12 Gt muisteja tuskin on tulossa, kun ei kukaan tee niin "harvaa" DDR5-muistia

Läppäreihinhän tuommoisella saa sen 12Gt kamman kun niissä on noita neljän piirin kampoja.

Todennäköisempää on että 24Gb piirejä käytetään ECC tukevissa järjestelmissä ohjelmistopohjaisen virheen korjauksen toteuttamiseen kuten LPDDR4:ssa

– The minimum density of a single DDR5 die is 8 Gb, while the maximum is 64 Gb, quadrupling the maximum capacity of DDR4 dies

– addition of Error-Correcting Code (ECC) support for memory. This feature is now not exclusive to special dies, like with DDR4, but rather is built inside every die.

Oho, meinaavat 8 Gb:tä? Cadence tosiaan puhui että 16 Gb olisi lähtötiheys

16Gb siruilla tarvitsisi olla sirujen 16 bitin kaistalla.

Onko joku tietty syy, miksi DDR5-muisteja pitäisi saada 8Gt DIMMEinä? Siinä vaiheessa kun rupeaa valumaan edullisemman pään koneisiin (pari vuotta luultavasti vähintään vielä) DDR5:sta 16 Gt yhdellä kammalla toteutettuna ei välttämättä ole enää liikaa

Meinaat kuitenkin että jossakin laitteessa olisi vielä 64bit muistiväylä parin vuoden päästä?

Kyllä, meinaan että jatkossakin OEM-valmistajat tulevat myymään etenkin edullisemmassa päässä koneita, joissa on käytössä vain yksi muistikanava oletuksena, vaikka prosessori useampaa tukeekin.