Paketointiteknologiat ovat nousseet viime vuosina entistä suurempaan rooliin tehokkaiden piirien valmistuksessa. Erilaisia 2,5D- ja 3D-paketointiteknologioita on esitelty ja käytetty useiden eri valmistajien toimesta ja trendi näyttää jatkuvan myös tulevaisuuteen. Ääriesimerkkinä Intelin Ponte Vecchio rakentuu peräti 47 eri sirusta, jotka on liitetty toisiinsa Foveros-paketointiteknologian ja EMIB-siltojen avulla.

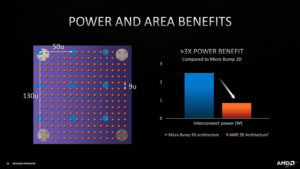

Sekä AMD että Intel ovat nyt esitelleet Hot Chips 33 -tapahtumassa uusimpia innovaatioitaan ja suunnitelmiaan lähitulevaisuuden paketointiteknologioihin ja piirien pinoamiseen. AMD:n kohdalla seuraava uusi askel on välimuistin lisääminen nykyisiin Zen 3 -siruihin uudella V-Cache -sirulla, joka asennetaan suoraan Zen 3 -prosessorisirun oman L3-välimuistin päälle TSV-läpivientien (Through Silicon Via) avulla. Piirit yhdistetään suoraan toisiinsa kuparikontaktein, minkä kerrotaan pienentävän tehohävikkiä kolmannekseen micro bump -kontakteja käyttävään malliin verrattuna.

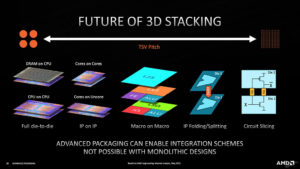

TSV-kontaktien pienentyminen tulee mahdollistamaan tulevaisuudessa entistä enemmän vastaavankaltaista integraatiota. AMD:n diassa esitellään paitsi mahdollisuuksia pinota DRAM-muistia suoraan prosessorin päälle, myös prosessorien tai yksittäisten ytimien ja muiden prosessorin osien kuten uncoren pinoamista päällekkäin. Pidemmällä tulevaisuudessa tavoitteena on mahdollistaa jopa virtapiirin jakaminen kahteen päällekkäin pinottuun siruun.

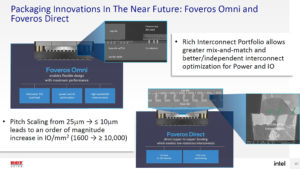

Intelin esitelmässä keskityttiin jo aiemmin tänä vuonna esiteltyihin teknologioihin, kuten Foveros Omni ja Foveros Direct. Nykyisessä Foveros-teknologiassa päällä olevan piirin on oltava hieman pienempi, kuin alla oleva. Foveros Omni tulee hylkäämään tämän rajoitteen mahdollistaen kontaktien viemisen myös alla olevan piirin ympäriltä. Foveros Direct puolestaan mahdollistaa piirien yhdistämisen suoraan kuparikontaktein AMD:n V-Cachen tapaan. Se pienentää kontaktien pinta-alan 25 µm:stä alle 10 mikrometriin, mikä mahdollistaa pinnien määrän yli kymmenkertaistumisen neliömillillä. Voit tutustua Intelin teknologioihin tarkemmin aiemmassa uutisessamme.

Olisi voinut olla samalla tavalla kirjoitettu molemmilla kerroilla.

Tarkoituksella ei ole.

Oliko tässä jokin logiikka takana? Muissakin kohdin etusivun feediä käytetään lauseen sisällä sekaisin numeroita ja sanoja kuvaamaan samoja asioita. Omaan silmään se pistää, mutta Kotus voi toki olla eri mieltä.

Yleensä pyritään kirjoittamaan lyhenteet vähintään kerran auki. Numeroissa taas olikohan se kymmeneen asti tjsp kun on suositeltu kirjoitettavaksi sanoina eikä numeroina

Numerot on ihan selvä, mutta se että ensin käytetään lyhennettä ja heti perään vertailua tehdessä kirjoitettua, tuntuu erittäin epäloogiselta. Tuossa piti itse oikein miettiä että hetkinen, oliko tosiaan sama yksikkö eikä esim nm vs µm. Mielestäni aivan turhaa lukijan sekoittamista tässä tapauksessa.