AMD on päätynyt käyttämään toistaiseksi vain yhtä, Zeppeliniksi nimettyä sirua kaikissa Ryzen-, Ryzen Threadripper- ja Epyc-prosessoreissaan. Yhtiön seuraavan Zen-arkkitehtuuriin perustuva siru on koodinimeltään Raven Ridge ja se tulee sisältämään yhden CCX-prosessoriklusterin eli neljä ydintä sekä maksimissaan 11 Next-gen Compute Unit -yksikön Vega-grafiikkaohjaimen.

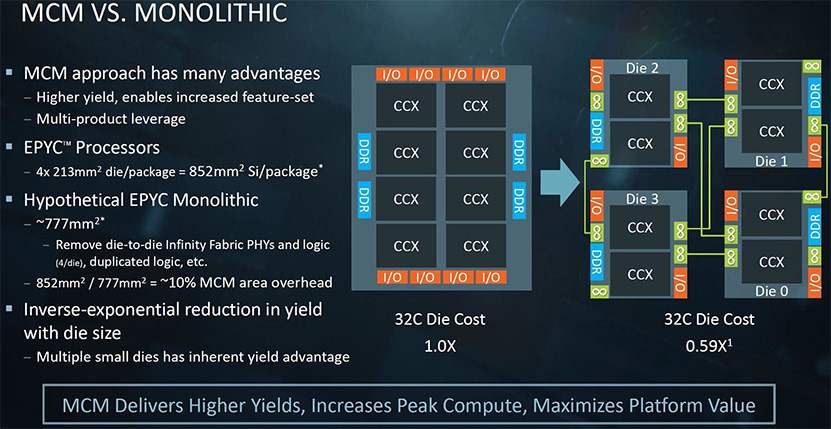

AMD:n HotChips-tapahtumassa julkaisema dia käsittelee mielenkiintoisesti Epyc-prosessoreiden eroja hypoteettiseen Epyciin, jossa olisi neljän sirun sijasta yksi jättimäinen siru. AMD:n mukaan hypoteettisen jättisirun kanssa säästettäisiin noin 10 % kokonaispinta-alaa verrattuna neljään Zeppeliniin, kun siitä poistettaisiin monen sirun tuomat päällekkäisyydet ja Infinity Fabric -linkit. AMD tosin perustaa laskelmansa 213 mm2 pinta-alaan, kun Zeppelinin todellinen pinta-ala on noin 195 mm2.

Vastapainona noin 10 % suuremmalle kokonaispinta-alalle AMD saa kuitenkin merkittävästi parempia saantoja, sillä todennäköisyys virheisiin sirussa kasvaa eksponentiaalisesti sirun koon kasvaessa. Lisäksi säästöä tulee vain yhden, kaikissa tuotteissa käytettävän ytimen suunnittelusta usean ytimen suunnittelun sijasta. AMD:n mukaan neljän sirun Epyc maksaakin vain noin 59% hypoteettisen jättisirun hinnasta. MCM-ratkaisun eduksi AMD laskee myös korkeamman maksimisuorituskyvyn, kiitos pienemmällä sirulla saavutettavien korkeampien kellotaajuuksien.

MCM:n ehkä huonoimpana puolena suurta yhtenäistä L3 välimuistia ei ole. Sitä ei läheskään kaikessa tarvita ja MCM rakenne tarjoaa mainituista syistä jotain erilaista mitä Intelillä on tarjolla.

En silti ihmettelisi mikäli Zen2:n Epyc versiossa olisi MCM:sta eroava rakenne.

Mahdollista, mutta Zen2 lienee ennakkotietojen perusteella vain paranneltu version nykyisestä Zenistä ilman mitään radikaaleja muutoksia. Eli eiköhän seuraavaan siruun perustuvat epycit ole myös neljästä prossasta koostuvia. Jahka amd pääsee (?) 7-8 nm tuotantoon, niin ehkä yhteen proossaan tungetaan enemmän ytimiä. Joillain joko päästään vielä useampaan kokonaisytimeen tai vähäisempään määrään prosessoreja. Luultavimmin ensimmäiset versiot vain pienentävät yhden yksikön kokoa.

Zen2:n ei tarvitse tehdä mitään erityisen radikaalia, voivat esim lisätä paremman AVX-tuen. Zen2:n arkkitehtuuri on oletettavasti valmistunut samoihin aikoihin kuin Zen1:n arkkitehtuuri. Zen2:n tulee 7nm valmistustekniikalla jonka todennäköisesti ratkaisee julkaisuajankohdan.

Itse en noin paljoa lähtisi olettamaan; varmasti joitain suuntaviivoja zen2den suhteen on vedetty jo zen1 aikana, mutta aivan varmasti AMD on myös valmistautunut korjaamaan zen1stä käytännössä ilmenneitä bugeja ja heikkouksia. Ensimmäinen vedos täysin uudesta arkkitehtuurista ei koskaan ole ollut niin optimaalinen, etteikö siitä opitun perusteella voisi seuraavaa viilailla parempaan.

Yhden piilastun ryzeneissäkään ei ole sitä yhtenäistä L3-välimuistia. Ettei sen puutteesta oikein MCM-ratkaisua voi syyttää.

Mitä selkeitä heikkouksia Zen1:ssa on? Ei tule mieleen yhtäkään. Zen ykkösestä jätettiin prosessorin pääsuunnittelijan mukaan pois monia asioita jotta saatiin virrankulutusta alaspäin. Helppo arvaus: ne poisjätetyt ominaisuudet tulevat Zen2:n ja Zen3:ssa muutetaan asioita enemmän. Sikälikin järkevää ettei Zen2:ta kannata viivyttää arkkitehtuurin takia mikäli GlobalFoundries oikeasti saa sen 7nm tuotannon aikataulussa käyntiin.

Yhden piilastun Ryzeneihin laitettiin tarkoituksella kaksi neljän ytimen rypästä, joka yksinään tarkoittaa jaettua L3 välimuistia, MCM:sta riippumatta.

Jokin syy Intelilläkin on tehdä prosessoreita 70 megan L3 välimuisteilla.

Kuten uutisessakin sanotaan, AMD:n ratkaisu on erittäin kustannustehokas ja mahdollistaa piirien valikoinnin. Lisäksi tuotanto on hyvin yksinkertaista kun ei tarvitse tehdä useampia erilaisia piirejä vaan yksi kelpaa kaikkialle. Huono puoli tulee noiden tasojen määrästä ja siitä ettei yksi ydin pysty nopeasti hallitsemaan suurta L3 välimuistia. Viimeisen syyn takia en ihmettelisi vaikka AMD toteuttaisi Zen2:ssa jotain eri tavalla. AMD:n huhutusta, todellista jättipiiristä, 32-core+HBM+Vega yhdistelmästä ei ole pitkään aikaan kuulunut mitään. Siinäkin saatettaisiin nähdä erilainen toteutus. Edes huhuja ei ole tullut vastaan pitkään aikaan.

Onko tuossa uutisessa virhe vai enkö nyt tajua jotain :)?

Alussa lukee: ”AMD käyttää EPYC-prosessoreissaan NELJÄÄ Ryzeneistä tuttua Zeppelin-sirua, mikä paitsi tuo säästöjä monelta kantilta, parantaa myös maksimisuorituskykyä.”

Ja seuraava lause on: ”AMD on päätynyt käyttämään toistaiseksi vain YHTÄ, Zeppeliniksi nimettyä sirua kaikissa Ryzen-, Ryzen Threadripper- ja EPYC-prosessoreissaan.”

AMD käyttää Epycissä neljää kappaletta Zeppelin siruja.

AMD käyttää yhtä ja samaa (= ei kahta erilaista) sirua Ryzenissä, Threadripperissä ja Epycissä.

Eli täysin ymmärrettävästi sanottu.

Ei siinä ole virhettä. Kaikki Ryzen, Threadripper ja Epyc mallit koostuvat samanlaisista siruista eli sirumalleja on tasan yksi, mutta niiden määrä vaihtelee 1-4 välillä mallista riippuen (Ryzen = 1, Threadripper = 2, EPYC = 4)

Ok, nyt tajusin :D!

Eikö GPU kannattaisi tehdä samalla logiikalla eikä näitä nykyisiä jättimäisiä siruja?

Varmaan vielä tullaan tekemäänkin. Jos kerran Crossfire/SLI nostaa tehoja ja välissä on PCIe väylä niin eiköhän se olisi ihan mahdollista. Ikuisuus kudosta vaan pienempien GPU kivien väliin.

Tuollainen on varmasti vähintään suunnittelupöydällä. Ainakin yksi ongelma on lämmöntuotto, yksi jättipiiri tuottaa jo nyt sellaisen määrän lämpöä ettei kaksi jättipiiriä samassa paketissa helposti onnistuisi. Samat sanat virransyöttöön. Crossfire/SLI on jäähdytyksen ja virransyötön kannalta selvästi helpompi.

Käsittääkseni Vegojen jälkeen AMD on siirtymässä myös graffapuolella useampaan pienempään siruun.

Non-temporal writejen käsittelyssä on jotain hyvin epäoptimaalista, koska niiden käyttö hidasti jossain pelissä ryzeniä selvästi, mutta ei hidastanut intelin prossuja.

Ongelma on muistikaista. Jos infinity fabricin tyyliset ratkaisut ovat ainakin toistaiseksi aivan liian hitaita tarjoamaan muuta kuin NUMA-muistia ja täten ongelmat ovat samat kuin SLI:ssä, ts kummallakin sirulla pitää olla erilliset muistit.

Tarvitaan parempi paketointi kuin perinteinen Orgaaninen cpu-kotelointi, jotta saadaan tarpeeksi kaistaa piirien välille. Intel esitteli omia ratkaisuitaan juuri hotcipissä (anandilla on sepustuksia) ja AMD:llä on tietty pii-kiekkointerposer joka tarjoaa mahdollisuuden ongelman ratkaisemiseksi.

Niin tarkoitinkin siis ettei nykyisiä GPU jättipiirejä enää tehtäisikään vaan pienemmistä paloista kuten nämä Zenit.

Muistikaista tuskin on ongelma koska tosiaan SLI/CF toimii jo nykyään, vaikka ei kaksi kiveä tuplaakaan tehoja niin +80% luokkaa ilmeisesti kuitenkin oikeissa olosuhteissa.

Mutta, pian tulee banaania offtopicista joten jätetään tältä erää tää tähän 😀

Tuosta olikin juttua jossakin vaiheessa. Osin jäi epäselväksi oliko kyseessä Ryzenin bugi vai tehtiinkö asia "Intelille sopivalla tavalla", koska Ryzen on AMD:n ensimmäinen SMT-prosessori. Jos tiedät lopullisen "ratkaisun", kelpaa hyvin. En ehtinyt seuraamaan asiaa tarpeeksi.

AMDltä tuli lausuntoja heti Ryzenin jälkeen, että heillä on jo optimointeja, joita ei ehditty laittamaan Ryzen1 joten osa, jopa iso osa Ryzen kakkosesta on jo testausvaiheessa tai ainakin päätymässä siihen. Enkä usko että 7nm ehtii Ryzen kakkoseen millään…

Se on puhdasta spekulaatiota ja "sattumalta" alkoi huhusivustoilla heti kun NVIDIAn MCM-paperi tuli julki

Roadmapissa joo, mutta ei vain millään jaksa uskoa että 7nm ehtisi tuotantokäyttöön vielä ensi vuonna, kun Intelkin kipuilee vielä oman suunnilleen yhtä tiheän 10nm tuotantonsa kanssa.

No ehkä ensi vuonna ei tule Ryzen2:sta vaan se siirretään 2019 julkaisuksi, mutta oletan silti että ensi vuonna tulee facelift versio.

Mutta olisihan se erinomaista jos ensi vuonna tulisi Ryzen2 7nm piireillä. Pitäisi Intelin tiukoilla, mutta en vain millään jaksa uskoa että ehtii…

Tuleeko Zen 2:t jo ensi vuonna? :confused2:

Miksei jos GlobalFoundries…

Ilmeisesti tarkoitus olisi tulla ensi vuoden puolella, mutta todennäköisyys myöhästymiselle 2019 puolelle lienee kohtalaisen suuri.

Öö.. mitä?

Katsohan pari reilun vuoden vanhaa adoredtv videota jossa asiaa jo käsitellään. Vega lienee viimeinen iso gpu amd:n puolelta. Navin slideissä "scalability".

Eiköhän siellä tule perusyksiköksi noin 480 tehoinen piiri, joita sitten lätkitään kasaan, kuten topicissa zenejä.

Tietokoneiden parhaat myyntisesongit ovat yleensä:

Back to school (heinäkuun puoliväli-syyskuu)

Black Friday (marraskuu)

Joulu

Mikäli 7nm tekniikka ehtii jouluksi 2018, sillä todennäköisesti tehdään pieniä määriä kalliita tuotteita, joilla saadaan rahat pois. Mikäli ei ehdi jouluksi, odotettavissa hieman suurempi launchi maalis-huhtikuun paikkeilla jotta saadaan kesän aikana alustoja hiottua back to schoolia varten.

Et sitten viitsinyt laittaa edes linkkiä siihn videoon.

Ja se että joku mr nobody jossain youtub-videossa väittää jotain on juuri sitä mitä kaotika sanoi: epämääräisen huhusivuston huhu.

"Scalability" voi tarkoittaa käytännössä ziljoonaa eri asiaa. Se voi tarkoittaa myös sitä, että samalla arkkitehtuurilla voidaan tehdä piirejä väliltä 1-128 ydintä.

Tai se voi tarkoittaa sitä että kellotaajuus skaalautuu 500 MHz ULV-laitteista 2 GHz high end-piireihin.

Onhan spekulaatiota ollut aina, itsekin muistan tehneeni yhden kuvaväärennöksen aiheesta joskus aikoinaan syötiksi, mutta se heräsi uudelleen tuon NVIDIAn MCM-tutkimuksen myötä

Scalability voi yhtä hyvin viitata paluuseen erittäin vähävirtaisien piirien markkinoille (jopa mobiililuokkaan asti)

Todennäköisesti kyllä, mutta itse CCX:n tulee 2 corea lisää. AMD on jo lipsauttanut että Starship koodinimeä kantavassa suorittimessa on 48 corea. Ja 7nm siirryttäessä 6 corea per CCX on iha järkevä ratkaisu.

Onhan siinä monia, esim. muisti latencyt kun mennään zeppelinistä toiseen.

AMD EPYC Infinity Fabric Latency DDR4 2400 v 2666: A Snapshot

Tuossa on ihan hyvää settiä tuosta muisti latencystä ja EPYC varmasti tykkäisi 3200 muisteista myös mutta sellaisia tuskin tullaan näkemään servereissä ihan heti kun toi 3200 tuntuu olevan jo kotikoneissa melkoista tappelua.

Tuossa videolla on myös hyvää infoa ja siitä selviää myös PCI-E vahvuudet ja heikkoudet.

Miksei onnistuisi? AMD on tuomassa 2 lastun laskentakortin jossain vaiheessa. Ei se vaadi mitään muuta kuin hiukan tiputtaa kelloja ja jännitteitä niin tehontarve tippuu aivan älyttömästi kun taas suoritus kyky ei tipu paljoa.

OT

En, koska kipeänä sängyssä.

Lähinnä se että väität spekulaation alkaneen nvidian tiedotteen jälkeen. Kyllä sitä spekuloitiin jo paljon aikaisemmin. Toki nvidian tiedote nosti taas kierroksia ja antoi "vahvistusta" spekulaatiolle.

/OT

Juurikin näin. GPU:ista puhuessa vega 64 oli aivan liian korkealle kellotettu ja voltitettu. Kaksi sopivalla tehoalueella toimivaa vega 64:sta toimisi hienosti, eikä lämpötilan kanssa tulisi mitään ongelmaa.

Ylipäätään voisin veikata että yhden ison piirin aikakausi alkaa olla lopuillaan. Niin CPU kuin GPU puolella. Epyc on hyvä esimerkki. Halpa, helppo ja toimii lähes kaikkeen hyvin.

CPUissa vaan kehitys mennyt täysin toiseen suuntaan, ja jatkaa menemistään täysin toiseen suuntaan.

EPYCiä ei myydä kuluttajille, vaan se on monta tonnia maksavat palvelinprossu, ja halvimmankin threadripperin hinta on lähellä tonnia. Järeitä palvelinprossuja AMD on ennenkin tehnyt MCM-ratkaisuina.

Sen sijaan aiemmin on ollut erillisinä piireinä

1) CPU

2) pohjoissilta(muistiohjain)

3) eteläsilta(io-ohjaimet)

4) näyttis

ja nyt on paljon piirejä joissa nämä kaikki on yhdellä piilastulla.

Ja intelillä on aiemmin olltu MCM-ratkaisuna kuluttajaprosessori kuluttajahintaluokassa, ei ole enää.

Monen piilastun ratkaisussa ongelmana on se kaista niiden piilastujen välillä. Nyt on tullut uusia väyliä, jotka taas hiukan helpottavat tätä ongelmaa, mutta ne eivät ratkaise sitä, ja kun laskentakapasiteeti ja kaistantarve taas kasvaa, sitten nämä nykyiset väylät jää taas jäljken.

Liioittelua tuo ongelma. Supertietokoneiden prosessorit ovat jollain valokuitu lähiverkolla toisissaan kiinni. Ja ne on aika nopeita koneita laskemaan asioita. Infinity Fabric lienee hieman nopeampi kuin joku valokuitu LAN.

Viivanleveyttä ei voi ikuisesti pienentää joten ainoa ratkaisu on juuri tämä mitä AMD nyt tekee.

Piti kuitenkin klikata "näytä huomioimatta jätetty sisältö"..

Suosittelen myös katsomaan niitä supertietokoneiden hintalappuja.

Se, että jotain käytetään n. 100ssa maailman nopeimmassa supertietokoneessa, ja se että

se yleistyy muutaman satasen hintaisissa kuluttajapiireissä on täysin eri asia.

Ja niillä supertietokoneilla lasketaan sellaisia ongelmia, jotka ovat "embarassingly parallel", joissa sitä kommunikaatiota on vähemmän, ja toisaalta niissä on myös varaa duplikoida joka nodelle teratavuittain muistia.

Kuluttajalaitteissa taas yksi oleellinen hintaan vaikuttava tekijä on muistin määrä. Ei ole varaa duplikoida samaa dataa moneen eri muistiin vaan jotta sen saa joka paikassa ladattua nopeasti.

Eikä ole, kuluttajahintaluokassa.

Normaalit ihmiset yksinkertaisesti eivät halua maksaa niissä kalliista MCM-ratkaistuista kun halvempi yhden piilastun ratkaisu on ihan tarpeeksi nopea kaikkeen mihin he tietokoneitaan ja muita älylaitteitaan käyttävät.

Toki sitten tulee niitä ammattikäyttöjuttuja, joissa sitä laskentatehoa oikeasti tarvitaan paljon ja ollaan valmiita maksamaan siitä, ja aina löytyy pieni määrä liikaa rahaa omaavia harrastelijoita, jotka haluaa vain "nopeinta" piittaamatta siitä, onko siinä mitään järkeä ja tekevätkö he sillä oikeasti mitään.

Henkilökohtaisesti on pakko tuumata, että tämän kyseisen "mr. nobody":n vuosia vanhat huhut olivat jo silloin paremmin kartalla, kuin puolet tehcpressistä on tänä päivänäkään. Sama pätee ihan omiin kommenttehisi, noita kun on tullut jonkin verran nähtyä ja ellen väärin muista niin muutamalla muullakin sivustalla. Se vaan valitettavasti on niin, että näissä IT-hommissa tietyt "mr. nobodyt" tuntuvat aina olevan ne, jotka ovat oikeasti syvällä näistä asioista. Siksi vituttaakin nähdä joku dissaamassa juttuja sen takia, että ei ole mitään "muropakettia" tai "orava-mediaa" jätkän taustalla, ettei sanoisi että dissauskin kun kuuluu vielä samasta "nobody"-porukasta.

Noita Adoren videoita tuli tuolloin vuosi sitten katseltua ja ne pointit joita se noissa aikoinaan esitti, riippuivat jos jostakin ulosannista, testistä, tiedonannosta tai tuloksesta, yleensä monesta eri lähteestä ja jotka se selitti ihan suoraan ilman niin että epämääräisyyksiä ei juuri jäänyt. Tosiaan vaikka noiden kanssa tuli otettua lusikallinenkin suolaa, kun poikkesivat valtavirran käsityksistä monesti paljonkin, niin ei ole kovin hirveän ihmeellistä että osui suhteellisen oikeaan siitä mitä ennusti. Se kun osasi kaivaa perus tylsästä bisnestiedonannostakin sellaisia viitteitä, jotka normaali jenkki-techpress jätti kuuntelematta, tarttuessaa ensimmäiseen klikkihuoraukseen vääntäen siitä juttunsa.

Kai ainakin voisi L1d:n assosiaatiokonflikteista nopeammin selvitä (himeno).

Koska vastaavaa ei saada esiin juuri missään muussa ohjelmistossa, laitan huonon ohjelmiston piikkiin asian. Ei prosessoria kannata suunnitella periaatteella "selviää huonosta koodista jota löytyy yhdestä softasta miljardista".

Ei varmaankaa, mutta eiköhän niitä softia ole useampiakin joissa hypyt ytimellä toiselle ovat kalliita tehon suhteen.

Ryzen oli eka julkaistu iteraatio, joten viilattavaa varmasti jäi, mutta ei niillä viilauksilla enää isoa hyppyä saada aikaan, jos vertaa vaikka Intelin saavutuksiin IPC puolella. AIna löytyy pientä parantamisen varaa, mutta vaikutukset ovat merkittäviä usein vain hyvin spesifisissä tilanteissa. Ryzenissä ehkä hiomalla on saavutettavissa vähän enemmän kuin Intelin puolella jossa arkkitehtuuri on perustaltaan jo aika iäkäs. Uusi mesh isoissa prossissa sitten muuttaa jo aika paljon ja kyseisen tekniikan valuminen kuluttajapuolelle on mielenkiintoista seurattavaa. Seuraavat lienevät vielä perinteistä ringbussia?

Toisaalta matalimmat hedelmät kannattaa poimia ensin.

Eiköhän AMD:llä ole Excelissä korjaukset/muutokset/optimoinnit listattuna oletetun saavutettavan hyödyn perusteella, josta napataan X määrä järkeviä toteutuskohtia.

hmm, millähän optioilla nuo Phoronixilla oikein on tuota käännelleet…

Imutin tuon single-thread c-version lähdekoodin, käänsin gcc -O3lla, ja sain skylakella(i7-6700) tulokseksi Skylakella 4636 megaflopsia, Ryzenillä(1700) 5647 megaflopsia.

gcc:n versiona 5.4.0

Tuskin tuossa on kyse hypyistä ytimeltä toiselle vaan jostakin ihan muusta.

Ryzenistä jätettiin pois monta parannusta virrankulutuksen pienentämiseksi, eli kyllä sieltä jonkin verran on saatavilla lisätehoa. Ei tietenkään mitään 50% jne. Kellotaajuuden nostolla single thread nopeus Zen2:ssa luultavasti kasvaa enemmän kuin arkkitehtuuriparannuksilla.

Ring bus ei paljoa hidasta pienillä ydinmäärillä ja toisekseen kuluttajaluokan prosessoreissa on integroitu näytönohjain, siksi en usko meshin ihan heti tulevan kuluttajaluokkaan (6 ydintä ja alle).

Mesh on aika turha sellaisella ydinmäärällä, mitä kuluttajasarjan prossuissa on, en odottele sitä kuluttajaprossuhin piiitkiin aikoihin.

No nythän sinä vallan paskaa rupesit puhumaan. Kyllähän se on juuri toisinpäin että isot monoliittiset ratkaisut ne vasta kalliita on ja ja tuhlaa pii-pintaalaa huonompien saantien vuoksi.

Missasit pointini täysin.

Suuri määrä pii-pinta-alaa on JOKA TAPAUKSESSA kallis, tekee sen MCM:nä tai monoliittipiirinä (ja monoliittipiirinä se on jonkin verran kalliimpi)

Tulevaisuudessa vaan ei mihinkään kuluttaja tarvi suurta määrää piipinta-alaa, ja se PIENI määrä sitä piipinta-alaa minkä kuluttaja tarvii, on halvempi ja kätevämpi tehdä monoliitipiirinä kuin MCM:nä.

Kristallipallot on ennenkin olleet väärässä eli sinunkin on parempi alkaa tarkastelemaan asioita ilman kristallipalloa. Nyt kun AMD pisti tämän ydinsodan alulle, niin se tarjoaa täysin uusia mahdollisuuksia koodaajille.

Se että 10v kuluttajapuolella mentiin karkeasti sanottuna dual core ehdoilla, voikin tulevaisuudessa muuttua hyvinkin nopeasti.

nVidia on jo sanonut että monoliittisen yhtimen raja on tullut vastaan ja ovat alkanu MCM vaihtoehtoja tutkimaan. Jos asiat olisi niinkuin sinä ne näet, niin ei AMD olisi MCM ratkaisuun hypännyt saatikka nVidia tutkisi vaihtoehtoja. Ja tuskin Intel myöskään jättää MCM ratkaisua huomioimatta.

Vaikka MCM tekniikalla hiukan piitä kuluukin enemmän teoriassa jos oletetaan saantien olevan 100%, niin käytännössä MCM tulee halvemmaksi koska siellä on aina sellaisia siruja jotka ei toimi laisinkaan.

Kun roskiin menee 800 neliön piiri 200 neliöisen sijaan niin onhan siinä valtava ero.

Mistähän mahdollisuuksista nyt oikein puhut?

Ei se tarjoa mahdollisuuksia vaan päin vastoin, lisää vaivaa että pääsee samaan lopputulokseen

Ytimien kanssa tällä ei ole mitään tekemistä.

Ja edelleen jätät ymmärtämättä pointin.

800 neliömillimetrin piirit ovat tavalliselle kuluttajalle täysin EVVK. Ne on vaan yksinkertaisesti aivan liian kallita, myös MCM:nä tehtynä.

MCM-ratkaisuja tarvitaan järeissä ammattilaispiireissä.

Kuluttajalle riittää se erittäin hyvin se maksimissaan n. 400mm^2 piiri, ja sen kokoinen piiri ei ole MCM:nä käytännössä yhtään halvempi valmistaa kuin monoliittisena piirinä.

Joku 600mm^2 piiri on MCM:näkin selvästi yli puolitoista kertaa kalliimpi kuin se 400mm^2 piiri, ja joka tapauksessa maksaa liikaa ettei tavallisella kuluttajalla ole mitään halua eikä tarvetta ostaa sitä.

(Toki löytyy aina muutama rikas idiootti, mutta markkinat näille on melko pienet)

Sinä sivuutat nyt kokonaan sen pointin että tulevaisuudessa ei tarvita kuin se MCM malli ja sillä saadaan katettua kaikkien tarve, niin tavallisten kuluttajien kuin ammattilaisten. Mielestäni AMD on jo nyt hyvin sen todistanut Zen arkkitehtuurin kanssa. Painetaan yhtä piiriä. Ei tarvita kuin yksi tuotantolinja ja pari kokoonpanolinjaa ja kaikki on tyytyväisiä, kun vastaavasti Intelillä on aika monta tuotanto ja kokoonpanolinjaa.

Samaa voidaan tulevaisuudessa odottaa tapahtuvaksi myös GPU puolella ja tätä nVidia on jo tutkinut.

Vaikka se ison MCM piirin valmistus teoriassa olisikin hiukan kalliimpaa kun tehdään MCM, niin saantien ja säästyneiden tuotantolinjojen takia lopputulos on halvempi.

Yksi ei riitä millään, ja parillakin tilanne menee helposti ääripäissä epäoptimaaliseksi.

Halvemmissa piireissä on ihan turhaan käyttämättöminä väyläliitäntiä suurentamassa piiriä.

Halvemmissa piireissä on ihan turhaan tuki paljon isommalle fyysiselle muistille kuin mitä siihen millään saa kytkettyä, ja tämän takia esim. välimuistien kirjanpidot ja kaikki piirin sisäiset osoiteväylät vaativat ylimääräisiä bittejä.

CPUssa matalan tason piirisuunnittelu/kirjastosolujen valinta pitää tehdä sen mukaan, että saavutetaan ne vähäytimisen kuluttajahuippumallin suuret kellotaajuudet, mikä selvästi pienemmällä kellolla pyörivässä ziljoonaytimisessä serverimallissa on täysin turhaa ja vaan lisää pinta-alaa ja virrankulutusta.

Ja kommunikaatio-overheadit tulee aina, piirin sisäisen väylän saa aina tehtyä paljon nopeammaksi kuin ulkoisen. Se, paljonko ne haittaa on sitten tapauskohtaista.

Onko sinulla nyt yhtään käsitystä miten mikropiirejä valmistetaan, kun puhut näistä "tuotantolinjoista" ja "kokoonpanolinjoista".

Ihan samaa tehdasta voi käyttää eri piilastuille, ihan yhtä aikaa.

Jopa samalla piikiekolla voi olla montaa erilaista piilastua (tätä harrastetaan tosin lähinnä pienten prototyyppisarjojen kanssa).

ja yksi paketointilinja ei todellakaan riitä kun niitä paketointeja on monta erilaista.

Ja AMD ei ole ainakaan zenillä yhden piilastun riittävyyttä kaikkialle todistanut kun on hyvin pian tuomassa ulos toisen zen-pohjaisen piilastun.

Se, missä MCM-ratkaisulla säästää selvemmin on tuotekehityskustannukset. Piirin layouttaaminen valmistusta varten maksaa. AMDllä on vähemmän insinöörejä ja vähemmän varaa kuin Intelillä, ja AMD myy pienemmän määrän piirejä, niin AMDn pitää säästää tässä enemmän. Intelillä taas on varaa layoutata isompi määrä erilaisia piirejä, ja isompia piirejä, kun se kokonaisuudessaan myykin enemmän piirejä.

Tuotantolinjalla tarkoitan AMD:n tapauksessa sitä kun zeppelin on ulkona.

Kokoonpanolinjalla AMD:n tapauksessa tarkoitan sitä kun se zeppelin istutetaan hartsialustalle ja juotetaan IHS kiinni = sinulla on toimiva CPU

AMD:llä on tällähetkellä tasan 2 eri pakettia. AM4 ja SP3, jälkimmäinen kattaa myös Threadripperin.

Vähävirtaiset mallit toki erikseen.

Miksi kaikesta pitää alkaa aina nussia sitä pilkkua?

Paketoinnista: Kaksi on suhteellisesti aika paljon enemmän kuin yksi.

Ja kolme on vielä enemmän kuin yksi. Se, mitä väitit yhdeksi, on pian todellisuudessa kolme. (Raven Ridge vaikka menee myös AM4-väylään, vaatii erilaisen paketin kuin Zeppelin, koska piilastu on eri kokoinen, ja kaikki pädit on siinä eri paikassa, johdotukset paketin sisällä menee ihan eri tavalla)

Threadripperissä ilmeisesti paketin sisällä on joku dummy-die jotta voidaan käyttää sitä samaa paketointia kuin EPYCissä.

Jaa että kun ensin hypetät innokkaana sitä kuinka "yksi riittää" ja sitten kun yksi ei riitäkään, siitä huomattauminen siitä on mielestäsi "pilkunnussintaa". EI se ole pilkunnussintaa, se on sinun virheellisten väitteidesi korjaamista.

Eikä Raven Ridgessä ole kyse vain vähänvirtaisista malleista. Siinä on ylipäätään kyse malleista, joissa on näyttis integroituna samalle piirille.

Ja näitä tullaan todennäköisesti myymään moninkertainen määrä zeppelin-pohjaisiin piireihin verrattuna.

Ja siihen oikeasti vähävirtaiseen markkinasegmenttiin saattaa joskus tulla kolmas zen-pohjainen piilastu, mutta tällä hetkellä AMDllä ei riitä tuotekehitysresurssit sen tekemiseen, joten aluksi siihen myytävät piirit tehdään kytkemällä Raven Ridgestä osia pois päältä. (vrt Stoney Ridge, joka oli pienempi excavator-pohjainen piiri)

Heh!

Te puhutte aika eri asiasta. Hkultakala puhuu oikeista kuluttajista. Niitä joille riittäisi 200€ puhelimen soc kaikkeen mahdolliseen. JiiPee taitaa puhua enthusiast käyttäjistä jotka tuhlaavat koneeseen 1000€ tai jopa sen yli.

Ihan varmasti pieni monoliitti on parempi Matti Meikäläisen marketti mikroon. Yksinkertaisempi ja selvästi halvempi. Joku tehokäyttäjä 64-128 ytimellä luultavasti koostaa laskentapiirinsä useammasta kuin yhdestä osasta.

Mutta tavallinen kuluttaja ei takuulla tarvitse paria kolmea ydintä enempää siihen että käy facebookissa ja pankissa. Sekä katsoo siinä samalla kissavideoita tuubista 😉

Olen 99% varma että itse pärjäisin vielä vuosia hyvällä neliytimisellä, mutta kyllä sitä siitä huolimatta kutkuttaisi hankkia joku 16 ytiminen mörssäri, joka olisi 99% käyttöajasta totaalinen overkill ja lopun aikaakin luultavasti vain overkill…

No toivottavasti olen väärässä ja tulisin tarvitsemaan sitä kuuttatoista johonkin jo muutaman vuoden sisään… no edes kahdeksaa…

Nimenomaan. Itsellä pölyttyy nurkassa vanha koneeni Athlon 5000+ / 8gt ddr2 800mhz / nvidia 550Ti

Peruspertti ei huomaisi surffauksessa varmaan mitään eroa tuon koneen ja 16-core Threadripper+Vega64 välillä varsinkin jos käytössä vielä SSD lätty.

Tarkoittako tämä "En usko!"?

Minun gcc 5.4 ja 6.4 näytti käyttävän AVX2:een kuuluvaa käskyä (vbroadcastss) vain alustusfunktioissa mat_set() ja mat_set_init(), laskenta oli edelleen iloisesti skalaari-avx:ää.

Normi Himenolla minulla on ollut Ivyllä heittoja 1200-1600 gflopsin välillä riippuen siitä, ajetaanko se bootin jälkeen vai sitten kun uptimea on tullut reippaammin. Ryzenillä se olikin sitten välillä 50-1100 gflops, tyypillisesti tuota pienempää ja pienemmät datasetit nopeutui aiemmin uptimen kasvaessa. En tiedä miksi, mutta modaamalla himenoa niin, että muistin varauksen kanssa pistin memsetin alustamaan muistin nollasta poikkeavalla arvolla, himenon suorituskyky stabiloitui Ryzenillä niin, että saatoin profiloida sitä. Tuo auttoi myös Ivyllä. Enabloimalla transparent hugepages kernelistä Ryzen ei enää tarvitsisi tuota workaroundia, mutta Ivy kyykkää enemmän. TLB trashingia kenties.

Mutta itse asiaan. Binäärit ovat käännetty -O3:lla, mikäli oikein muistan. Ajot jostain kuukauden takaa.

"Hieman" huteja koodille jossa seuraava iteraatio on "lue seuraava tuosta vierestä".

Huomasin että datasettien koot ovat ikävästi kakkosen potensseja ja koodi näytti siltä että loopin sisällä haettiin dataa alueilta, jotka saattoivat olla offsetattu toisistaan korkealla kakkosen potenssilla datasetin koosta johtuen. Datasetin koon muuttaminen antoikin välitöntä palautetta. Muokkasin osoitteenlaskentamakroa:

Eli lisäsin paddingia (ja varasin hitusen enemmän muistia kuin normi himeno).

Pikkasen vihasemmin kulkee koodi, varsinkin Ryzenilla.

Skimmasin läpi tuon himeno 2:n, erona näkyy olevan ettei se laske indeksejä makrolla ja mikä tärkeintä, datasettien koot välttää kakkosen potensseja (on 2^n+1).

Lopeta valehtelu. En ole väittänyt että yksi riittää, vaan olen tarkoittanut että ne mitä on ulkona, niille riittää yksi tuotantolinja ja 2 paketointilinjaa. Joka on edelleen aika helvetin paljon vähemmän mitä Intelillä on desktop/serveripuolelle. En ole missään vaiheessa väittänyt että MCM olisi jotenkin universaali kattaen ihan kaiken mahdollisen vaan tarkoitin mitä AMD on nyt saanut pihalle joka kattaa serverit/desktopit.

Muttas sinun piti alkaa heti nillittää asiasta ihan vain koska siihen sait mahdollisuuten koska en tarpeeksi SELVÄSTI herralle asiaa ilmaissut.

Se että lätkitäänkö raven nippuun samalla kokoonpanolinjalla kuin rytsölät, sitä et tiedä sinä enkä sitä tiedä minä. Se on vain sinun mutuiluasi että se tarvitsee omansa.

Vaikea lopettaa, koska en ole koskaan aloittanutkaan.

Sinulla tuntuu olevan aika valikoiva muisti sen suhteen, mitä olet aiemmissa viesteissäsi sanonut.

Juuri niin olet tuossa sanonut.

Se, mitä tarkoitat tuntuu aina muuttuvan sen mukaan, kun jäät kiinni siitä, että se mitä alunperin tarkoitit paljastuu ettei pidäkään paikkaansa.

Sen sijaan että rehellisesti myöntäisit olleesi väärässä, alat keksimään ettei oikeasti tarkoittanutkaan sitä mitä alunperin väitit.

Tässä aika oleellinen kysymys on, että mitä tarkoitetaan "kokoonpanolinjalla".

Sinä niistä aloitit höpisemään, ilmeisesti tietämättä itse mitä tarkkaaonttaen sillä tarkoitat (tai määrittelemällä sen niin epäselvästi, että pystyn taas tarvittaessa vääntämään määrittelyt jälkikäteen sinulle edulliseen muotoon)