Intel on kertonut sijoittajapäivillään rutkasti uutta tietoa lähivuosien suunnitelmistaan ja varmistanut aiempia vuotoja tosiksi. Tapetilla tapahtumassa olivat muun muassa valmistusprosessit ja tulevat Xe-arkkitehtuurin näytönohjaimet ja laskentakortit.

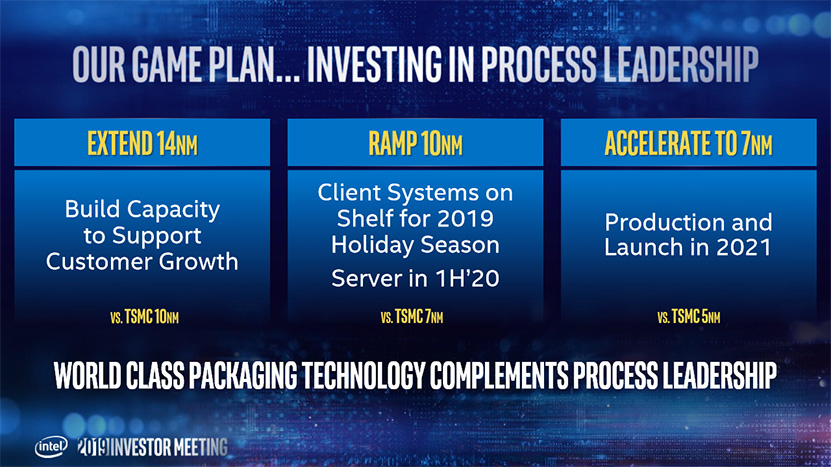

Ei ole salaisuus, että Intelin 10 nanometrin prosessi on pahasti myöhässä aikataulustaan. Nyt asia nostettiin esiin myös dioissa, jossa rehellisesti todettiin prosessin olevan nyt kolme vuotta myöhässä aikataulustaan. Yhtiön mukaan valoa on kuitenkin tunnelin päässä, sillä 7 nanometriin aiotaan siirtyä nopealla aikataululla.

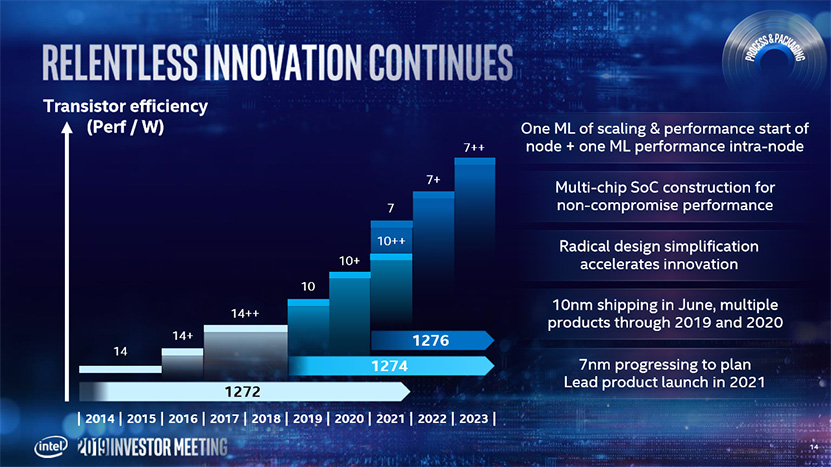

Intelin diojen mukaan 10 nanometrin prosessia tullaan parantamaan 14 nanometrin tapaan kahteen kertaan. Vuonna 2021 julkaistava 10++-prosessi tulee kuitenkin saamaan rinnalleen ensimmäisen 7 nanometrin valmistusprosessin, joka tulee niin ikään saamaan 7+- ja 7++-päivitykset vuoden välein. 7 nanometrin myötä myös Intel tulee ottamaan käyttöön EUV-litografian ja prosessi on suunnattu kilpailemaan TSMC:n 5 nanometrin prosessia vastaan.

Yhtiön ensimmäinen 7 nanometrin tuote tulee olemaan Xe-arkkitehtuuriin perustuva laskentakortti datakeskuksiin. Laskentakortin kerrotaan tulevan hyödyntämään Foveros-teknologiaa. Intel varmisti lisäksi, että se tulee käyttämään nimenomaan datakeskuksiin suunnattua varianttia Xe-laskentakortista Aurora-supertietokoneessa.

Vaikka datakeskuksiin julkaistava Xe-laskentakortti on yhtiön ensimmäinen 7 nanometrin tuote, se ei tule olemaan ensimmäinen Xe-arkkitehtuurin edustaja. Xe-arkkitehtuuri tuodaan näillä näkymin ensimmäisenä prosessoreihin vuonna 2020 julkaistavan Tiger Laken myötä, joskin Raja Koduri on myös twiitannut aiemmin ensimmäisen Xe-erillisnäytönohjaimen julkaisun tapahtuvan 2020, mikä varmistettiin nyt uudelleen.

Intel esitteli dioissaan myös visionsa datakeskisestä tulevaisuuden prosessorista lanseeraten samalla ”XPU”-termin. Konseptikuvassa samalle alustalle olisi integroitu parhaimmillaan 16 HBM-pinoa ja yhtä monta XPU:ta, millä yhtiö tarkoittaa sekä prosessoreita, grafiikkapiirejä että muita mahdollisia kiihdyttimiä. Piirit voidaan toteuttaa myös kullekin yksittäiselle piirille parhaiten sopivalla valmistusprosessilla.

Lähde: Intel

Eipä taida ensimmäinen versio 10nm:stä taipua desktop puolelle tarvittaviin kelloihin.

Mun mielestä aika kova juttu, että 7 nm prosessi tulee jo vuonna 2021, vaikkakin ilmeisesti desktop-prosessoreja pitää odotella sen jälkeen vielä vuosi.

10nm tapaan myöhästyy 3 vuotta ja tulee 2024 :hammer:

Palvelinpuolelta ylipäätään ei näyttänyt olevan mitään erikoisempaa kerrottavaa. Tietävät etteivät pärjää Epyc Romelle joten pyyhe kehään suosiolla tässä vaiheessa.

Tuskin… Intelillä on varaa polttaa rahaa tuotekehittelyyn ja vaihtaa kaikki vaikka kuinka moneen kertaan. Eli 7nm tulee ajoissa riippumatta täysin siitä mitä 10nm käy jatkossakaan.

Mutta vielä hetken aikaa AMDlla on aikaa tehdä 7nm tuotteilla tulosta ainakin jossain määrin. Mitä tuli luettua, niin osa valmistajista on jo perunut aikeitaan käyttää AMD prossia omissa tuotteissaan, joten tiukassa elää käsitys, että vain Intelin prossilla voi tehdä liiketoimintaa… huokaus…

"Liimattu kasaan" sanoi Intel silloin kun AMD julkaisi Epycit. 😀

Kelloista ei pahemmin mainintaa. Olen saanut jostain käsityksen että näissä pienemmissä viivanleveyksissä on helpompi saavuttaa virransäästöä kuin kasvattaa kelloja ja olikohan se nyt niin että vähän pakko tehdäkin niin koska sähkövuotojen ja ylilyöntien riski kasvaa etäisyyksien pienentyessä. Joka tapauksessa Intel tuntuisi nyt paukuttavan sitä kuinka kirjoittavat mobiilipuolen uudestaan jne, mikä vähän viittaisi siihen että virrankulutus tulee joo pienenemään mutta varsinaisesti vauhti ei tule samassa suhteessa kasvamaan tyyliin samat kellot, mutta 20% pienempi virrankulutus, niin noi perf/watt-käppyrät näyttävätkin jotakuinkin tuolta.

Ei ole punaisenkaan leirin fiaskot estänyt lupauksien nielemistä.

Eiköhän tuolle 10nm prosessillekin ollut varaa polttaa rahaa tuotekeittelyyn vaikka kuinka. Ihan kaikkea rahallakaan ei saa.

Mistäs tuollaista luit ja mistä tuotteista kyse?

Tätä 7 nanometrin prosessia kehitettiin rinnakkain 10 nm kanssa ja se pohjautuu EUV:hen, jonka pitäisi toimiessaan tehdä valmistuksesta helpompaa.

katso liitettä 226127

Vain aika näyttää, miten tämä käytännössä menee, mutta ainakin teoriassa 7 nm voisi tulla suhteellisen vikkelään.

Yksi EUV:tä haittaava tekijä on sopivien valolähteiden kalleus ja tehottomuus. Valotukset kestävät pitkään ja laite maksaa ziljoona miljoonaa -> kallista touhua.

Sitä mukaan kun ASML:n ja kumppaneiden EUV-laitteet tehostuvat suhteessa hintaan, niiden käyttö muuttuu realistisemmaksi massatuotteiden valmistamiseen.

Sitä kuulemma kehitettiin erikseen, joka tietenkään ei tarkoita etteikö senkin kanssa voisi tulla ongelmia. Eihän kukaan olisi viisi vuotta sitten uskonut jos olisi väitetty Intelin 10nm prosessin myöhästyvän yli 3 vuotta. Eli katsotaan kun tulee.

Toki voi tulla, mutten usko. Intel on kompastellut aikaisemminkin, mutta rahalla noussut kaivosta aina takaisin.

This olla Anandtechin artikkelissa, jossa puhuttiin siitä kun Intel sanoo prossapulan helpottavan puolessa välissä tätä vuotta, joka oli sitten jo johtanut muutaman firman perumaan aikeitaan käyttää AMD prossia… Voisi kuvitella, että kyseiset firmat eivät alun perinkään olleet kiinnostuneet ajatuksesta käyttää AMD prossuja, joten ei kai mikään iso uutinen, mutta ikävä osoitus markkinoiden Intel vetoisuudesta.

Aika epäloogista. Historiassa prosessoripulat ovat Aina helpottaneet jossakin vaiheessa. Ei kenellekään voi tulla yllätyksenä ettei minkään valmistajan prosessoripula voi jatkua ikuisesti (ellei valmistaja suoraan lopeta tuotantoa). Muutenkin mikäli prosessorille on oikeasti tarvetta heti, ostetaan sitä mitä on saatavilla. Jos taas ei ole tarvetta heti, kyse on vain "ostan joskus jotain enkä tiedä mitä" tason jutusta. Ei tuollaisella "uutisella" ole sen takia mitään arvoa.

”Intel esitteli dioissaan myös visionsa datakeskisestä tulevaisuuden prosessorista lanseeraten samalla ”XPU”-termin. Konseptikuvassa samalle alustalle olisi integroitu parhaimmillaan 16 HBM-pinoa ja yhtä monta XPU:ta, millä yhtiö tarkoittaa sekä prosessoreita, grafiikkapiirejä että muita mahdollisia kiihdyttimiä. Piirit voidaan toteuttaa myös kullekin yksittäiselle piirille parhaiten sopivalla valmistusprosessilla.”

Tuossa on nähtävissä tiettyä synergiaa kun

AMD ”lainasi” piirisarjanimet Inteliltä vaihtamalla Z tilalle X niin nyt

Intel ”lainaa” AMD:lta Apun ja vaihtaa A:n tilalle X:än APU > XPU

🙂

Pitää myös muistaa, että AMD on täysin TSMC:n vastuulla prosessin suhteen.

Käsittääkseni tässä ei ole mistään uudesta "XPU"-termistä kyse sinänsä, vaan se vain tarkoittaa että se voi olla CPU, GPU (tai joku muu xPU)

Tuossa on monia mahdollisuuksia.

Voi olla, että ovat ajaneet testiä AMD:n raudalla ja eivät syystä tai toisesta olleet tyytyväisiä.

Voi olla, että Inteliltä on tulossa riittävän lähiaikoina entistä parempia tuotteita.

Vo olla, että prossupula ei ole tuolla PRO puolella niin näkyvä asia, kuin peruskäyttöpuolella.

Niin, paha tuosta on sanoa. Virallisestihan palvelinprossut on ensisijalla tuotannossa, läppäripuoli taisi olla kakkosena. Ja se tiedetään että läppäripuolella prossupula tuntuu (Apple maininnut asiasta)

Juu jos jossakin Pro puolella joudutaan vaihtamaan prossupulan takia Intelistä AMD:hen niin se on perus toimistomikrot ts ei mikään erityinen rahasampo niin että vaikka vaihdos tapahtuisi se ei merkittävästi näy AMD:n tuloksessa.

Noissa Lenovo tekee vaihdon varmaan suht helposti mutta Dellille on isompi kynnys tehdä AMD kone ja HP on siitä välillä, eli jos joku perui AMD toimistokoneiden teon niin se on Dell.