Intel on kertonut Memory/Storage Day -tapahtumassaan yhtiön lähitulevaisuuden suunnitelmista muistiteknologioiden saralla. Yhtiö silmäileekin tällä hetkellä jo 5 bittiä soluun tallentavien NAND-solujen suuntaan.

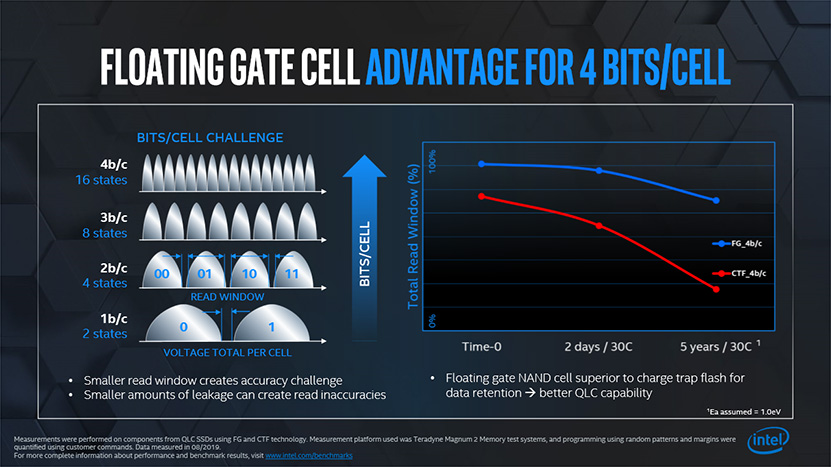

Intelin mukaan sen Floating Gate Cell -teknologia on monin tavoin perinteisiä Charge Trap Cell -teknologioita parempi. Sen kerrotaan esimerkiksi parantavan jännitetasojen erottelua eri solujen välillä ja parantavan datan säilyvyyttä. Yhtiön mukaan sen CMOS Under Array -teknologian käyttö yhdessä FG-teknologian kanssa tekee yhtiön 96-kerroksisista NAND-siruista markkinoiden tiheimpiä. Kehitys ei kuitenkaan ole pysähtynyt ja yhtiö uskoo aloittavansa 144 kerroksisten NAND-sirujen valmistuksen ensi vuonna.

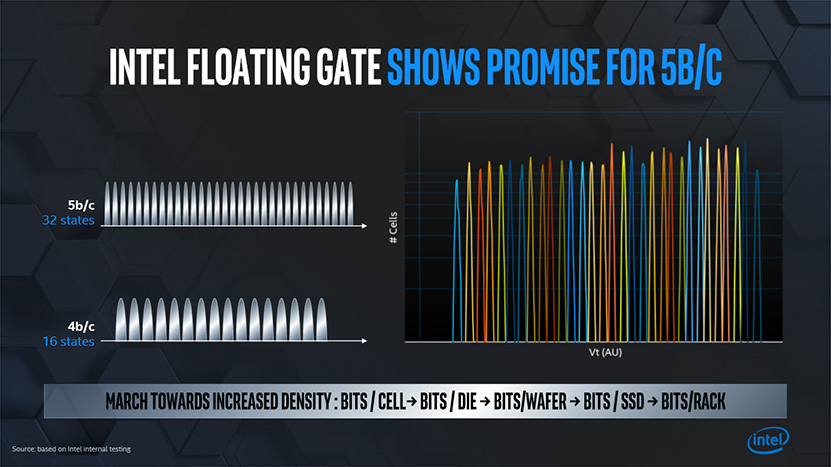

Markkinoille on tuotu askel askeleelta enemmän bittejä per solu tallentavia ratkaisuja. Useampien bittien tallenus solua kohti parantaa muistien kapasiteettia, mutta samalla heikentää niiden luotettavuutta. Nykyisellä neljä bittiä soluun tallentavalla QLC-tekniikalla solussa on jo 16 eri jännitetasoa ja mitä enemmän jännitetasoja on, sitä pienempi on solun lukuikkuna ja sitä pienemmät vuotovirrat voivat vaikuttaa datan lukemisen tarkkuuteen. Intelin mukaan sen FG-teknologia mahdollistaa paitsi alun alkaen suuremman lukuikkunan, myös pitkässä juoksussa kymmeniä prosentteja suurempana pysyvän lukuikkunan, mikä parantaa datan säilyvyyttä. Yhtiön mukaan se uskoo FG-teknologian taipuvan myös seuraavaan askeleeseen eli viiteen bittiin per solu. Viisi bittiä tallentavissa soluissa on jo 32 erillistä jännitetasoa.

Lähde: Intel

Vaikka intelin solu olisi luotettavampi, tuntuu että ei se oikeasti näy kuin markkinapuheissa.

Ilmeisesti kuitenkin valmistaja tiedostaa, etä suurin ongelma kummassakin tekniikassa on muistien jännitteen häviäminen soluista.

Voisiko Intelin SSD tekniikasta käyttää jopa termiä analoginen digitaali tekniikka, ainakin itse sain käsityksen että siinä ei ole kiinteitä jännitearvoja vaan lasketaan maksimista mitä on jäljellä.

Pelottaa kun valmistaja määrittelee datan säilymisen laskevan vain 2 päivän päähän.

Onhan noi pelottavia lukemia, mutta jollain sitä kapasiteettia on saatava lisää ja pakkaaminen pienempään tilaan on se edullisin.

Eli ei data diskiksi, mutta boottausasemaksi ehkä.

Ei tästä taida olla peruskäyttäjän levyksi. QLC on jo nyt todella hidas kun SLC-cache loppuu, ja tässä nopeus laskenee tasolle ”suunnilleen sama kuin 7200RPM kovo”.

Käyttötarkoituksena lienee lähinnä palvelimet jossa SSD:n käyttöä voi optimoida nimenomaan tälle teknologialle.

Miten niin kahden päivän? Eikö kuitenkin tuon kuvaajan oikea reuna ole ”5 vuotta 30 asteessa”, ja silti jäljellä luettavuutta?

Peruskäytössä tuo slc cache ei tule levyn elinajan aikana loppumaan koskaan.

No se on QLC mutta kahden päivän päästä jo tippunut lähemmas 30-40%

Tarkoitin vain miten huonoa tavaraa on markkinoilla jatkossa ja purukumilla yritetää tieto pitää kasassa.

Muutaman viikon päästä jännite 50% tason kohdalla. Toki virhekorjauksella luettavissa.

Mielestäni 2 päivän päästä ei tietojen säilytyspaikassa saisi tapahtua minkäänlaista mahdollisuutta tiedon korruptoitumiseen.

katso liitettä 283427

SLC cache loppuu kun levy alkaa täyttyä.

Esim jos haluat 10GB SLC cachea käyttää esim elokuvan kopioinnissa.

pitää levyllä olla 50-100GB tyhjää tilaa. Tarve riippuu miten taustalla slc cachea tyhennetään levylle normaalitilaan.

No 1GB dram cache helpottaa samsungin QLC levyllä muutenki huomattavasti, mutta jos tulee ilman dramia olevia levyjä on ne pidettävä tyhjinä.

:facepalm:

On aika puusilmä jos ei näe eroa purukumin ja modernien virheenkorjausalgoritmien välillä.

Jospa nyt heittäisit roskiin kaikki tällä vuosituhannella valmistetut massamuistisi ja tyytyisit vaan siihen n. vuodelta 1995 olevaan 500-megaiseen levyyn. Suurinpiirtein Niin kauas pitää mennä, että tulee vastaan massamuisteja jotka on suunniteltu siten, että se data voidaan oikeasti tallentaa sinne luotettavasti, eikä mitään virheenkorjausta tarvita.

Mistä ihmeestä nyt tuon "jännite 50% kohdalla"-väitteesi repäisit. Tuo linkkaamasi käyrä ei puhu mitään siitä.

MIstähän sen elokuvan sinne levylle oikein olet kopioimassa?

Verkon yli? Verkon kaista on kuitenkin se rajoittava tekijä.

Ulkoiselta massamuistilta? Se on kuitenkin se rajoittava tekijä.

Se, että jonkun teratavuluokan tiedoston kirjoittamisessa levyn nopeus putoaa selvästi alle maksiminopeutensa on kotikäyttäjälle täysin merkityksetön ongelma. Sillä on väliä jossain palvelinjutuissa sekä videonkäsittelyssä.[/quote]

>Verkon yli? Verkon kaista on kuitenkin se rajoittava tekijä.

Gigabit ethernet on standardi integroiduissa "paskaohjaimissa", 10GigE on ollut olemassa jo 12 vuotta, ja isoissa kaupungeissa valokuitu alkaa tulla seinään asti eli sille alkaa pikkuhiljaa olla käyttöä kotiverkossakin. Jälkimmäisellä saa MLC levynkin jumiin, ja etummalisella saa modernin QLC levyn jumiin kun se lähenee täyttä. Nämä tulevat PLC levyt tukkeutuvat paljon nopeammin ellei näille lyödä oikeasti tolkuton määrä välimuistia. Välimuistin ulkopuolella olevan tiedon lukemisesta verkkoon puhumattakaan. Mene ja mittaa 32 eri tasoa luotettavasti ja nopeasti. Onnea.

Halpa, nopea, laadukas. Valitse kaksi. Pätee myös SSD ohjaimiin. Ja PLC:n koko pointti on tehdä se mahdollisimman halvaksi, eli siihen ei varmastikaan lyödä huippukallista ohjainta jolla on jopa jotain toivoa lukea nuo 32 eri jännitetasoa nopeasti ja luotettavasti. Huom: intel ei puhu edes teoriassa siitä että tämä olisi ylipäätään mahdollista.

>Ulkoiselta massamuistilta? Se on kuitenkin se rajoittava tekijä.

Perus 7200RPM NAS tason SATA kovo tulee todennäköisesti olemaan nopeampi kuin PLC SSD sequential read&write tehtävissä, 10k RPM ja 15k RPM SAS levyistä puhumattakaan. Laita noita vielä pari pari kappaletta RAID 0/1/10:ksi niin kuin kotiNAS palvelimilla usein tehdään, niin sillä saa jo modernin QLC SSD levyn tukkoon jos luku/kirjoitus on pyörivän levyn puolella sequential read ja QLC SSD alkaa olla lähellä täyttä.

Ja kyllä, peruskäytössä QLC on kotikäyttäjälle ongelmallinen. Alkuvaiheessa se on vielä ok, mutta kun levy lähenee täyttä, nopeus romahtaa. Itse en hankkisi TLC:tä heikompaa NAND flashia oman koneen muistiksi, ja silloinkin vain jos ohjaimella on välimuistina mukava määrä SDRAMia eikä pelkkä SLC. Varsinainen nimensä mukainen "massa"muisti kannattaa olla mieluummin pyörivällä medialla, tulee halvemmaksi ja sequential readissa jota isojen tiedostojen pomputtelu on, se pärjää vallan mainioisti QLC:lle, tästä tulevasta PLC:stä puhumattakaan.

Totta puhut. Intel 660p .. VMP VMP VMP VMP … menee hermot. :rage:

Ei minkäänlaista DRAM cachea, kun SLC bufferi lopahtaa niin ohjain vetää koko koneen tillintallinlukkoon kunnes kirjoitus valmistuu. Koska minkäänlaista DRAM kakkua ei ole, tuo kuratunkki ei pysty mitenkään fiksusiti scheduloimaan kirjoituksia ja lukuja, vaan stallaava kirjoitus jumittaa ihan koko helvetin koneen jos ko. asemmalle on käyttis asennettuna. Näillä QLC kokemuksilla minua ei saa puhuttua PLC:lle kyllä mitenkään. QLC:n kohdalla pitää tarkasti katsoa ohjain ja sellaisella ajetut testit.

En ole henk. koht päässyt DRAM:lla avustettua QLC:llä testailemaan, mutta kotoolta löytyy erilaisia TLC asemia, ja DRAM cachettomien kanssa on sama ongelmaa kuin tuola 660p:llä. SLC bufferin lopahtaminen kesken kirjoituksen tai trimmin ajo bufferittomalle asemalle vetää koneen jumiin. Esim trim:n ajon aikana Firefox käynnistys kestää 2 minuuttia. Samsungin DRAM kakullisella ohjaimella näin ei käy. DRAM cachettomista asemistani Kingstonit tuntuvat jumivan koneen kaikkein pahimmin em. tilanteissa.

— edit —

660p:ssä näimä on DRAM cache. Eli ohjain on ihan kelvotonta kamaa.. 🙁

Miten tuollaiselle saa edes stallauksen aikaan ”normaalikäytössä”?

Entäs jos vertaillaan 1TB Inteliä ja saman hintaista ”nopeampaa” 512GB Nvme asemaa, joista kummallakin on 500GB data. Kumpi on nopeampi normaalikäytössä (vaikkapa steam-pelin asennus) kun sinne yritetään kirjoittaa 20GB lisää?

Epäilisin että Inteli aika tavalla nopeampi kun NVMe:ltä loppuu tila kesken :geek:

Täällä on 2Tb 660p "TM käyttötestissä", katsotaan tuleeko ongelmia vastaan :nb:

Työpöytä/läppäriinhän tuon pitäisi sopia koska oletettavasti suurimmassa osassa ei kirjoiteta teratolkulla dataa päivittäin ja cache kikkailulla saadaan pidettyä hyvä suorituskyky. Sitten taas johonkin raid pakan cacheksi täysin sopimaton levy. Ja olen käsittänyt että kaikissa SSD:ssä alkaa suorituskyky menemään kuralle jos levy tulee täyteen.

Tämä on aika pelottavaa. Onko siis mahdollista, että kesken pelaamisen tietokoneeni alkaa lähettämään 10gb videotiedostoa käyttöjärjestelmäni levylle ihan itsestään, kun pelikirjastoni makaa QLC levyllä, joka oli ostaessa hyvä idea koska se on reilusti halvempi eikä pelit tarvitse niin nopeaa SSD levyä toimiakseen yhtä nopeasti kuin vaikka SATA liitännäisellä SSD levyllä?

Tilanne huolestuttaa, varsinkin kun koko koneessa ei ole varmaan ainoatakaan yli 1GB tiedostoa ja tuskin tulee ikinä olemaankaan. Olenko ostanut nyt itselleni jotain mistä olen tähän asti pitänyt todella paljon, mutta onkin täysin käyttökelvotonta?

Ajatella että minua voisi vielä melkein pitää tietokoneen tehokäyttäjänä, mutta jos tämä ei kerran peruskäyttäjällekään kelpaa niin vaihdettava se kai sitten on.

"En tiedä mistä puhun, siispä vittuilen."

Todellisuudessa win10 voi laittaa vaikkapa trimmauksen päälle pelaamisesi aikana, jos peli on sellainen joka ei aggressivisesti striimaa tekstuureja. Ja sitten jossain vaiheessa tulee "hetkinen, miksi tämä seuraavan levelin lataus kestää kymmenen sekunnin sijasta kaksi minuuttia?". Tai päivitysten imeminen. Tai muuta hienoa win10 touhua. Mikä lyö tyypillisen QLC levyn niin pahaan tilttiin, että siinä on pahimmillaan koko käyttis jumissa kun I/O odottaa vastausta.

Mutta sinulla on varmasti tehokäyttäjänä suora pääsy win10 lähdekoodiin, ja win10 versiosi on tietenkin itsesi kokoama niin että siinä on nämä ongelmat tottakai korjattu, eikö niin?

Ja sitten olet tajunnut ottaa "näytä piilotetut ja järjestelmätiedostot" päälle ja katsonut järjestelmälevyn pohjakansioon, josta löytyy näitä vähintään yksi kappale windowsin pakottamina sitten Vistan, joka on kaiken muun hienon lisäksi sellainen tiedosto joka päivitetään jokaisen käynnistyksen yhteydessä. Kaksi oletusasetuksilla. Puhumattakaan win10 hienon päivitysmekanismin aiheuttamasta datastore.edb koosta kun järjestelmä on ollut samalla levyllä tarpeeksi pitkään. Joka on muuten juuri se tiedosto jota win10 update tykkää tökkiä silloin kun sille tulee mieli hakea päivityksiä.

Muthei, minähän olen tässä se peruskäyttäjä ja sinä se paljon osaava tehokäyttäjä. Älä välitä paskanjauhannastani, ja täytä se QLC levysi tappiin huoletta. Se rankka hidastelu joka sitä tulee seuraamaan ei varmastikaan ole jonkun peruskäyttäjän höpinän mukaista seurausta.

On enemmänkin "Tiedän mistä puhun, mutta osaan käyttää tietoni järkevästi, enkä sumentaa ajatustani autismilla"

Jos olisit huomannut, niin sanoin pelilevyni olevan QLC. En laittaisi välttämättä QLC levyä käyttöjärjestelmälevyksi, mutta ne on todella hyviä levyjä esimerkiksi juuri pelikirjastoihin. Toisaalta nyt kun ajattelen taaksepäin, niin minulla on niin kauan kuin muistan ollut pelkälle käyttöjärjestelmälle oma levynsä, tämä tarkoittaa myös sitä että siellä on oikeasti vain pelkkä käyttöjärjestelmä ja pari ohjelmaa, joten 120 – 250gb levy on aina riittänyt, eikä se ole koskaan tullut lähellekään täyteen koska siellä pidetään pelkkää käyttöjärjestelmää. Sanoin sen nyt tahallaan pariin otteeseen ettei tällä kertaa menisi ohitse.

Pidätkö tosiaan kaikkea dataa yhdellä levyllä ja jaat sen osioihin? Sehän on todella outo ratkaisu. Levyn vaihtamalla joudut hävittämään aina kaiken datan, tai sitten jos se yksi levy vaikka hajoaisi. Käyttöjärjestelmän uudelleen asennuskin helpottuu, eikä käyttöjärjestelmän levy mene koskaan täyteen kun siellä on vain se pelkkä käyttöjärjestelmä.

Missä kohtaa nyt QLC on kauhean ongelmallinen? Voisin vaihtaa vaikka tuon 970 evon samantien QLC lättyyn eikä minulle varmasti tulisi yhtään ongelmaa, sen enempää kuin nykyäänkään.

Tuskin olen ainoa henkilö kun tekee näin.

Riippuu mitä kenenkin "normikäyttö" on. Kun se on sitä yleistä pelailua, web härdellöintiä, jotain satunnaista tiedoston siirtelyä jne. Ei tule ongelmia. Joku videoeditointikaan ei pitäisi olla ongelma, koska se on jokatapauksessa CPU bound ongelma.. eli ei riitä oikeen missään koneessa CPU:ssa voima työntää niin nopeasti streamia läpi että tuo asema tukkeutuisi.

Mun päivittäinen käyttö on softadevailua. Tiettyjen testien ajelu generoi non-SQL kantaan satoja gigoja kirjoituksia 1-2 tunnissa kun testataan integraatiota vanhasta uuteen järjestelmään, silloin tuo 660p aiheutttaa täydellisen pään leviämisen.

Työntanajan ostamassa koneen romussa oli tuollainen, ei kestänyt hermot ostin paremman saman kokoisen ja iskin tuohon työntajan koneeseen, 660p siirtyi omaan pelikoneeseen jossa se ei tietenkään aiheuta ongelmia. Sitten jokus kun tuo työntajana kone lähtee eläkelaitumille työnnän tuon 660p:n sinne takaisin ja otan omani pois.

Sinulla taitaa nyt olla aika melkoinen harhakäsitys siitä, miten trim toimii.

Windwosin oletusasetuksilla TRIM-komento lähetetään windowsin toimesta SDD-levylle aina kun tiedosto tuhotaan. Se, koska se SSD-levy siihen reagoi riippuu sitten mm. siitä, millainen kuormitus sillä SSD-levyllä on. Jos se on kuormitettu paljon, se laittaa sen jonoon odottamaan hetkeä jolloin kuormitusta on vähemmän. Ja kun niitä pieniä trim-komentoja tulee sille levylle tasaisesti, se voi toteuttaa ne nopeasti silloin kun kuormitus on pientä, ilman mitään suurta jumia.

(Vain) jos joko

1) suuressa tehokäyttäjän viisaudessassaan(tm) mennyt kytkemään sen automaattisen trimmin pois päältä, tai

2) käyttää muinaista käyttistä joka ei sitä trimmiä tue,

joudutaan sitä trimmausta tekemään kiireessä silloin kun se tila meinaa loppua kesken, ja tarvii kirjoittaa uutta dataa levylle jolla tyhjää trimmattua tilaa ei ole, ja siitä tulee niitä suuria jumeja.

Ja jos itse samalla kun pelaa laittaa koneen taustalla siirtelemään gigatavuluokan tiedostoja joista voi tulla isoja trim-pyyntöjä, se on ihan omaa typeryyttä eikä mikään windowsin vika.

Tekstuurien streaamaaminen pitäisi levyn näkökulmasta olla read-only-operaatio. Se ei tee mitään mikä voisi laukaista isoja trim-pyyntöjä.

Sieltä taustalla pitää tehdä jotain muuta, joka sitä tiedostojen tuhoamista (tai ylikirjoittamista) aiheuttaa.

… mutta kellään ei ole koskaan mitään syytä alkaa kopioimaan swapfilettä tai hibernate-filettä partitiolta tai levyltä toiselle; Vaikka ne haluaisi siirtää, niitä ei kopioida vaan systeemille sanotaan wttä swaappaa tai talleta hibernate-fule tuonne, ja se luo sinne uuden. Ja swap-fileeseen tulee kirjoituksia n. 4 kilotavun vituaalimusitisivu kerrallaan.

Hibernate-fileeseen tulee kirjoituksia vain konetta nukuttaessa. Eli tällä on kotikäyttäjälle väliä ainoastaan kun kone nukutetaan.

Kahdessa ja puolessa vuodessa tälle tiedostolle on minulla tullut hurjat 25 megaa kokoa. Että jopa on hieno gigatavuluokan tiedosto :facepalm:

Se rankka hidastelusi kuulostaa lähinnä EVOltasi.

Ja jos verrataan sitä, että meillä on samalla hinnalla tehtynä joko 400 gigan SLC, 600 gigan MLC, 800 gigan TLC tai teran QLC, niin

1) siinä vaiheessa kun siellä levyllä on 398 gigaa dataa, se 600 gigan MLC toiminee aina paljon mukavammin kuin 400 gigan SLC;

2) siinä vaiheessa kun siellä levyllä on 598 gigaa dataa, se 800 gigan TLC toiminee aika paljon mukavammin kuin 600 gigan MLC

3) siinä vaiheessa kun siellä levyllä on 798 gigaa dataa, se teran QLC toiminee aika paljon mukavammin kuin 800 gigan TLC.

Minulla on mökilläni valokuituliittymä. Itse kuidusta menisi läpi vaikka kuinka paljon dataa, mutta operattori tarjoaa kahta nopeusvaihtoehtoa, 50(/100) ja 100(/100) Mbit/s. Valitsin näistä 50 Mbit/s koska se tuli kuukausimaksultaan halvemmaksi, ja koska se on minulle oikein tarpeeksi.

Ja jo muinainen pyörivä kovalevy pystyy yli 10 kertaa suurempiin nopeuksiin sekventiaalisessa kirjoituksessa.

Se, mikä sen verkkokortin teoreettinen nopeus on kotikäytössä aika merkityksetöntä, kun data tulee kodin ulkopuolelta, selvästi hitaampaa linkkiä pitkin.

Normaalilla kotikäyttäjällä ei ole mitään tarvetta floodata levyllen gigatavuittain dataa suurella nopeudella.

Sen siijaan normaalille kotikäyttäjälle on suuresti väliä, sillä, mikä sen levyn hakuaika on – erityisesti järjestelmälevyllä se tuntuu aivan kaikessa.

Höpöhöpö. 7200 rpm pyörivät levyt on sequential-nopeudeltaan 100 megaa sekunnissa luokkaa.

Flashillä taas sitä sequential-read nopetta saadaan rajatta lisää laittamalla vaan enemmän piirejä rinnakkain.

Se (oikeasti melko merkityksetön) sequential-read-nopeus teran QLC-NAND-flashi-SSDllä on helposti 1.5 GB/s luokkaa, n. 15 kertaa suurempi, eikä PLC hidasta tätä merkittävästi.

Kirjoitusnopeus taas… 660p:n (QLC) kirjoitusnopeus saatiin tompan testissä rankalla kuormituksella pudotettua 158 megaan sekunnissa. Edelleen n. puolitoista kertaa nopeampi kuin sen 7200 rpm pyörivän levyn nopeus.

Ja näiden sustained-nopeuksien tuijottaminen on vielä todella typerää. Todellisessa käytössä satunnaislukujen nopeus on paljon merkittävämpää, ja siinä hitainkin SSD on pari kertaluokkaa nopeimman pyörivän levyn edellä.

Edelleen selvästi hitaampia.

:facepalm:

Saanet laittaa niitä sen >5 kappaletta rinnakkakkain että pääset siinä täysin merkityksettömässä sekventiaalisessa lukunopeudessa lähelle edes yhtä SSD-levyä.

Ja vertaat niitä yhteen ssd-levyyn.

Jos sitä typerää sekventiaalista nopeuttasi haluat lisää, niin entäs jos laitettaisiinkin niitä SSD-levyjä myös monta siihen raidiin…

Mutta tuollaisten sekventiaalistin kirjoitusnopeuksien vertailu osoittaa joka tapauksesa lähinnä sitä, että ihminen on täysin pihalla siitä, mitä niillä levyillä yleensä tehdään, ja millä on väliä (koti)tietokoneen käytännön nopeudelle.

Hakuajoissa hitainkin SSD on aivan eri kertaluokkaa kuin nopeinkaan pyörivä levy, ja melkein aina kun levyltä jotain odotellaan, sillä hakuajalla on enemmän väliä kuin sekventiaalisella siirtonopeudella.

:facepalm:

Edelleen, samalla rahalla saa paljon isomman QLCn kuin TLCn tai TLCn kuin MLCn.

Samalla rahalla hankituissa levyissä se QLC ei tule täyteen siinä missä se TLC tulee täyteen. Jos on varaa jonkinkoiseen TLC-levyyn, on varaa isompaan QLC-levyyn, joka toimii 84% kuormitusasteella todella paljon nopeammin kuin se TLC-levy 99% kuormitusasteella.

Itse ostin juuri teraisen SSDn "massatallennuslevyksi". Harkitsin TLCn ja QLCn välillä, päädyin ostamaan n. 3% kalliimman ja 4% pienemmän TLCn – ei nopeussyistä, koska tuossa käytössä mihin se tuli, kaikki SSDt on aivan tarpeeksi nopeita, eikä benchmarkit osoittaneet noiden levymallien välillä mitään merkityksellistä nopeuseroa, vaan sen takia, että kun tuon levyn olisi tarkoitus kestää vuosia, niin TLCltä voi monen vuoden jälkeen odottaa inasen parempaa luotettavuutta, ja tuon n. 7% enemmän/koko olin valmis tästä odotuksesta maksamaan.

Jos tämä on joku äärirasituksessa saatu lukema, siitä voikin vetää johtopäätöksen, että 1 Gb/s verkkkoyhteydellä ei vielä saa levyä jumiin. Sitä nopeammilla periaatteessa voikin, mutta jos siitä aiheutuu jotain oikeaa haittaa, mistään normaalista kotikäytöstä ei enää puhuta.

Jätetäänpä tällaiset autismipuheet pois keskustelusta.

Mitenköhän tuo Intelin floating gate vs. charge trap vaikuttaa datan säilyvyyteen.