Yhä useammat piirit perustuvat yhden ison sijasta useampaan pieneen siruun (chiplet), joita yhdistetään toisiinsa eri paketointiteknologioita ja siltoja hyödyntäen. Kuluttajille teknologia on tuttu esimerkiksi AMD:n Ryzen-prossoreista, jotka ovat perustuneet alusta lähtien useampaan siruun ja Zen 2:sta lähtien erilliseen I/O-siruun ja prosessorisiruihin.

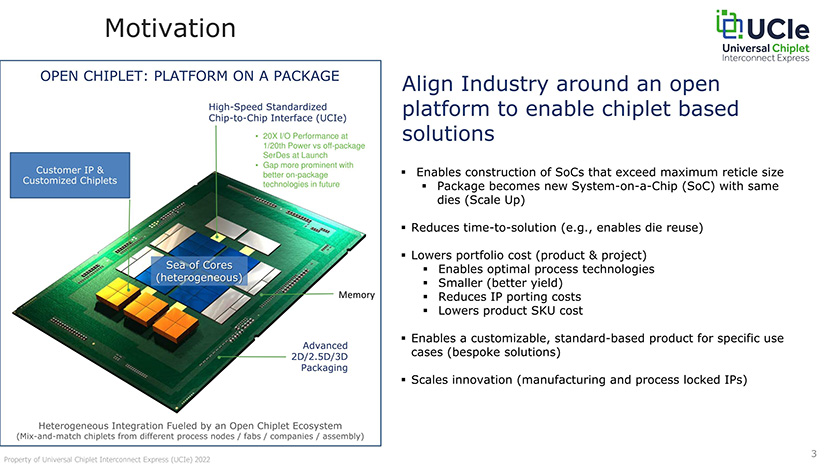

Universal Chiplet Interconnect Express eli UCIe on uusi AMD:n, Armin, ASE:n (Advanced Semiconductor Engineering), Googlen, Intelin, Metan, Microsoftin, Qualcommin, Samsungin ja TSMC:n (Taiwan Semiconductor Manufacturing Company) perustama yhteenliittymä, joka hallinnoi nimensä mukaista avointa standardia. UCIe on standardoitu sirujen välinen yhdysväylä, joka sisältää niin fyysisen kerroksen, tarvittavat protokollat kuin ohjelmistomallit ja testiohjelmatkin.

UCIe:ta voidaan hyödyntää käytännössä kaikkien modernien siltojen kanssa, oli kyse sitten Intelin EMIBistä tai esimerkiksi TSMC:n CoWoSista. Itse kommunikaatioprotokolla perustuu ainakin UCIe 1.0:ssa CXL:ään ja sen kautta PCI Expressiin. Tulevaisuudessa standardiin on tarkoitus sisällyttää mahdollisesti uusia kommunikaatioprotokollia, kehittyneempiä paketointi- ja siltateknologioita ja muita tarpeelliseksi nähtyjä päivityksiä.

Lisäksi standardissa on varauduttu saman teknologian käyttöön myös paketoinnin ulkopuoliseen kommunikointiin. Käyttämällä uudelleenajoittimia UCIe:ta voidaan hyödyntää jopa räkkitasolla, joskin silloin luonnollisesti otetaan takkiin niin tehonkulutuksessa kuin viiveissä. Tällöin yhdessä räkissä voisi olla esimerkiksi yksi vain muistille ja/tai tallennustilalle dedikoitu yksikkö ja useampia sitä käyttäviä laskentayksiköitä, jotka toimivat viiveitä ja vastaavia lukuun ottamatta täysin samoin, kuin samalla piirillä olevat UCIe:tä hyödyntävät laskentasiru ja muisti toimisivat.

Suosittelemme asiasta tarkemmin kiinnostuneille esimerkiksi AnandTechin katsausta teknologiaan.

Lähde: UCIe

Kommentoi uutista tai artikkelia foorumilla (Kommentointi sivuston puolella toistakseksi pois käytöstä)

Lähetä palautetta / raportoi kirjoitusvirheestä