AMD on esitellyt Next Horizon tapahtumassaan ensimaistiaiset tulevista prosessoreistaan ja laskentakorteistaan. Sekä tulevat grafiikkapiirit että prosessoriytimet valmistetaan TSMC:n 7 nanometrin valmistusprosessilla.

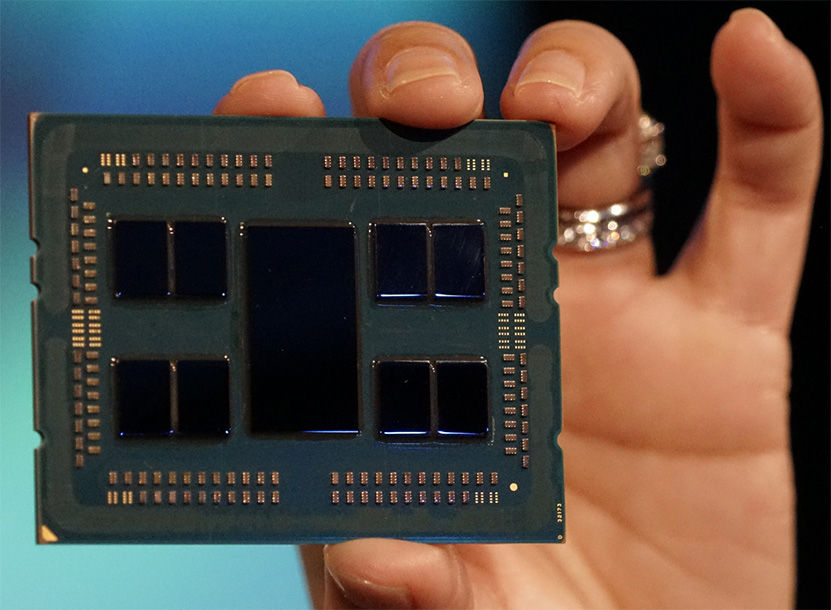

Illan päätähti oli Zen 2 -arkkitehtuuri ja siihen perustuvat Rome-palvelinprosessorit. AMD jatkaa odotetusti useamman piirin ratkaisulla, mutta vie sen vielä astetta pidemmälle. Rome-prosessoreissa on reunoilla yhteensä kahdeksan 7 nanometrin prosessilla valmistettua CPU-pikkupiiriä ja keskellä 14 nanometrin prosessilla valmistettava I/O-piiri. Yhteen Multi Chip Module- eli MCM-paketointiin on saatu näin sovitettua 64 ydintä. Prosessoriytimiin on tehty huomattavia muutoksia muun muassa kaksinkertaistamalla liukulukuyksikön leveys ja kasvattamalla välimuisteja.

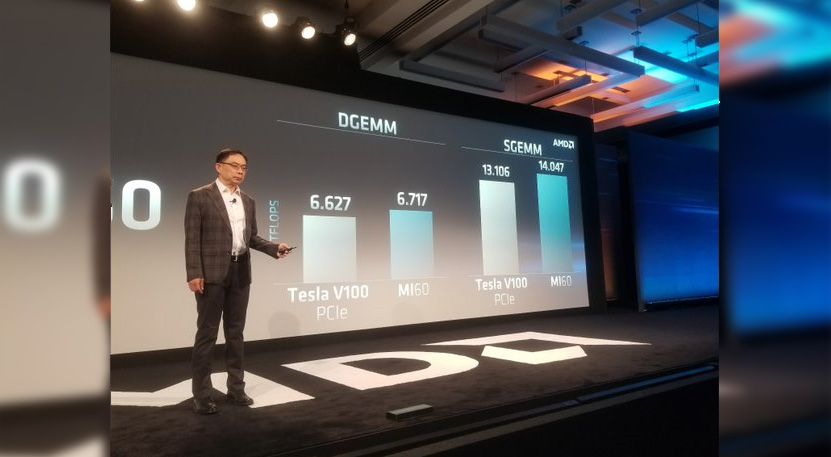

Vega 20 -koodinimellä aiemmin tunnettu grafiikkapiiri on paitsi maailman ensimmäinen 7 nanometrin grafiikkapiiri, myös ensimmäinen PCI Express 4.0 -standardia ja piirien välistä Infinity Fabric -linkkiä tukeva GPU. 13,28 miljardin transistorista rakentuvan piirin kooksi kerrotaan 331 mm2. Huhujen mukaisesti grafiikkapiiri tarjoaa 1:2-suhteen perus- ja tuplatarkkuuden laskuille. Radeon Instinct MI60 -huippumallin luvataan tarjoavan 14,7 TFLOPSin edestä laskentavoimaa FP32-tarkkuudella ja 7,4 TFLOPSia FP64-tarkkuudella, mikä riittää AMD:n testien mukaan Tesla V100:n PCI Express -version peittoamiseen DGEMM- ja SGEMM-testeissä. Muistikaistaa grafiikkapiirillä on käytössään teratavu sekunnissa ja sen 4096-bittisen muistiväylän jatkeena on 32 Gt HBM2-muistia. Radeon Instinct MI60:n rinnalle julkaistaan myös kevyempi MI50-vaihtoehto.

Julkaisemme huomenna AMD:n Zen 2 -prosessoreita ja Vega 20 -grafiikkapiiriä sekä niiden tuomia muutoksia tarkemmin käsittelevän uutisartikkelin.

Lähde: Tom’s Hardware

Ei se 128-bittinen muistiväylä ole 16 ytimellä suurimmalla osalla softista mikään paha pullonkaula.

Jollain 3.2 GHz datansiirtotaajuudella teorettista kaistaa on kahdella kanavalla 51.2 GB/s

Does dual-channel memory make difference in gaming performance? – Page 2 of 8 – Hardware Secrets

Tuossa verrattiin 12.8 GB/s vs 25.6 GB/s kaistoja keskenään 4-ytimisellä prossulla eikä pelitesteissä nähty juuri mitään eroa niiden välillä suorituskyvyssä.

Kommentit siitä kuinka parannettu micro-op-cache parantaa kellottuvuutta on ainakin täyttä potaskaa. Kellottuvuuteen vaikuttaa arkkitehtuurissa liukuhihnan pituus, tai siis hitaimman liukuhihnavaiheen viive.

Micro-op-cachen parannukset vaikuttaa siihen, kuinka suuri osa voidaan suorittaa sieltä, ja kuinka suuri osa normalin käskynhaun kautta. Tällä on vaikutus IPChen ja virrankulutukseen, ei kellottuvuuteen.

Päin vastoin, aina kun jotain tietorakenteita suurennetaan, on suurempi riski, että niistä tulee uusia kriittisiä polkuja hidastamaan kellotaajuutta.

Ja sitten nuo spekulaatiot vegan perusteella.. Massivisesti rinnakkaiden Vegan kelloa rajoittaa lähinnä virrankulutus.

CPUn maksimikelloa rajoittaa lähinnä kriittisten polkujen pituus.

Toki näiden välillä voi hiukan treidata jännitettä muuttamalla, mutta..

Nykyään tyypillisesti uudet valmistustekniikat pienentävät virrankulutusta pienehköillä ja keskisuurilla kellotaajuuksilla selvästi (mikä mahdollistaa lämörajoitteisen piirin ajamisen selvästi suuremmalla kellotajuudella), mutta eivät kovin paljoa paranna maksimikelloja ei-lämpörajoitteisessa tilanteessa (turbo-mode)

Ah hyväkun huomautit. Näimä ajatus katkesi kesken kirjoituksen… . Tarkoitus oli sanoa, että 2 chipletin / 16 Coren ylittäminen ei liene järkevää AM4:n kahdella muistikanavalla.

Ei toki pelatessa muistikaista nappaa kiinni (dGPU tässä oletuksena). Tosin sekin on kyseenalaista tarviiko siihen pelaamisene esim sitä 16C. Ehkä sitten joskus kun se RayTracing tulee kunnolla käyttöön. 🙂

Tuota muistikanavaa pohdin ihan jo sillä, että duunissa se saatiin pullonkaulaks. Tosin siitä on aikaa ja se kyseinen rautakin on museota. Meillä oli noita (Nehalem?) Xeoneja (E5530) workstation pannuissa.

Vakiona tulivat tilatessa vajaalla rammi kalustuksella (2/3 kanavaa kalustettu). Siinä sitten ajeltiin erilaisia peformance testejä omassa softa projektissa ja arkkitehdillä oli kone vielä alkup. kuosissa ja itsellä uusilla rammeilla @ 3/3 kanavaa.. ja se kovasti ihmetteli että miksi #¤%"#4:ssä sen kone on ~30% hitaampi. =)

Tosin eipä tuo AM4:n markkina segmenttiä sinänsä olekkaan tuo duunikäyttö. Onneksi sain perusteltua uudeksi WS:ksi TR:n, vähän tuli rutinaa hinnasta tosin.. 😀

Ei mutta mikäli se ei tarkoita APU:a + oletetaan ettei Threadripperiä tehdä erikseen vaan se on joko Epyc tai Ryzen pohjalta, silloin kyseessä on Ryzen

Kyllä meinaan eikä asiassa ole mitään epäselvää, koska GF sen sanoi suoraan ilman mitään vaaraa väärästä tulkinnasta:

https://www.eetimes.com/document.asp?doc_id=1333326&page_number=2

GF:lla oli ihan riittävästi asiakkaita myymään kaikki 7nm tuotanto. Ongelma oli seuraava: yhä harvempi asiakas haluaa maksaa paljon huippuluokan prosesseista + huippuluokan prosessien kehitys on todella kallista = kehityskustannuksien kattamiseen tarvitaan paljon kapasiteettia joka myy. Eli karkeasti: kehityskustannukset pitää saada katettua joka onnistuu vain jos on riittävästi kapasiteettia JA kapasiteetin tuotokset saadaan myytyä. GF pelkäsi ettei jälkimmäinen toteutuisi jos kapasiteettia olisi riittävästi kattamaan kustannukset. Koskee myös 7nm:n jälkeisiä prosesseja.

Kapasiteettia ei riittänyt edes AMD:lle joten siitä ei ollut kyse. Ja lähdettä tuolle "AMD tiesi GF:n ohareista kauan etukäteen"?

–

Mitä tähän Epyciin tulee, AMD ei sanonut kaikkien Epycien olevan samalla chiplet kaavalla. Eivätkä varmasti olekaan. Pienien ydinmäärien Epyceillä ei ole mitään järkeä luopua integroidusta muistiohjaimesta eikä myöskään yhdessäkään työpöytäprosessorissa.

Nythän tiedetään AMD:n halunneen tehdä jotain muuta ydintä kuin Epyc chiplettiä (jonka oli pakko olla APU tai jokin mikä Ryzeniin kelpaisi) GlobalFoundriesilla niin nopeasti kuin GlobalFoundries saa jotain valmiiksi. Tuotannon siirryttyä TSMC:lle AMD sanoi näin:

Jos tuo pitää täysin paikkaansa, siinä tapauksessa AMD tekee/teki TSMC:llä myös toisenlaisia Epyccejä joita voidaan käyttää Ryzeneissä. Ei tarvitse kaukaa hakea mitä: Zen2 arkkitehtuuri + copypastella Zen1:n I/O:t. Niitä oli tarkoitus käyttää vain Epyceissä mutta kuten Zen1:n tapauksessa, samaa sirua Ryzeneihin ja Epycceihin, miksi ei?

Koska TSMC:n ja GF:n prosessit ovat hyvin samankaltaiset, ei tule juurikaan kustannuksia suunnitella samaa piiriä molemmille.

Vaikuttaa ettei Ryzen kolmosia tarvitsekaan odottaa ensi syksyyn :kippis:

GloFo olisi oikeudessa ja tuomittu nopeammin kuin ehtii kissaa sanoa jos se out of the blue ilmoittaa lopettavansa tulevan prosessin kehityksen vaikka on jo tehnyt sopimuksia sen käytöstä asiakkaittensa kanssa.

Mitä tuo "out of the blue" asiaan vaikuttaa? Vältytäänkö oikeusjutuilta jos GF kertoo ehkä luopuvansa valmistusprosessin kehityksestä?

Onko esimerkkejä tällaisista oikeusjutuista? Intelin 10nm on myöhässä vuosia eikä sitä ehkä koskaan tule sellaisena kuin luvattiin. GlobalFoundriesin 20nm prosessi peruttiin kokonaan kuten myös 14nm prosessi.

Aika hiljaista oikeusjuttujen kanssa ollut. Eiköhän noissa ole iso kasa klausuuleja "mitäs jos ei onnistukaan" -juttujen varalta.

kenelle intelin ulkopuolella ollaan 10nm-prosessia on luvattu?

Ainakin LG:lle ja muutamalle firmalle jotka tekevät ARM-pohjaisia tuotteita Accelerating Foundry Innovation for a Smart and Connected World | Intel Newsroom

Eikös tämä kirjoitus nyt ole aika vahvasti ristiriidassa ihan itsensä kanssa. Jos ei ole maksavia asiakkaita, silloin ei ole asiakkaita.

Ei ole ristiriidassa itsensä kanssa mutta olisi voinut kirjoittaa selkeämminkin.

Tuossa yritettiin selittää ettei GF uskonut huippuluokan prosesseille olevan niin paljoa kysyntää että myynneistä saadut rahat kattaisivat kehitys ja tuotantokustannukset. Eli saadakseen voittoa pitäisi myydä X määrä piikiekkoja mutta ostajia on vähemmälle määrälle kuin X.

Siitä ei ollut kahtakaan vuotta kun GloFo oli tehnyt AMD:n kanssa viimeksi uuden kattavan viisivuotissopimuksen liittyen mm. 7nm prosessiin, kun ilmoitettiin julkisesti että 7nm kehitys on pysäytetty.

Siinä oltaisiin taatusti istuttu oikeudessa sopimuspetoksesta, ellei GlobalFoundries olisi jo kauan ennen ilmoitusta informoinut ja neuvotellut AMD:n kanssa kyseistä sopimusta uudelleen, etenkin kun sopimuksen mukaan AMD joutuu maksamaan GloFolle muilta ostamastaan kapasiteetista. Siten se "out of the blue" liittyy siihen.

GloFolla lienee hyvin ystävällisesti autettu AMD:ta siirtymään TSMC tuotantolinjoille.

Ei ole mitään syytä olettaa, että kukaan on tehnyt minkäänlaisia yllätys ohareita.

Semmoinen olisi aikalailla paha juttu tulevan Avera Semi foundry support busineksen alulle. :dead:

"Avera Semi will leverage deep ties with GF to deliver ASIC offerings on 14/12nm and more mature technologies while providing clients new capabilities and access to alternate foundry processes at 7nm and beyond."

Radeon™ Instinct™ MI60 Accelerator| Deep Learning and HPC | AMD

64 CU @ 1800 MHz Boost, 32 Gt HBM @ 2 Gbps

Radeon™ Instinct™ MI50 Accelerator | Deep Learning and HPC | AMD

60 CU @ 1746 MHz Boost, 16 Gt HBM @ 2 Gbps

Tukevat vain Linuxia (mikä asettaa entistä kyseenalaisempaan valoon FFXV-benchit kortilla missä ei ole näyttöliittimiä, kun FFXV on vain Windowsille)

Haastoiko AMD GlobalFoundriesin oikeuteen myös 20nm valmistustekniikan peruutuksesta? Tiettävästi ei.

Lueskelin tuon WSA:n läpi eikä siellä selkeää mahdollisuutta ole AMD:lla haastaa GF:a oikeuteen. Tai voivathan he mutta sitten voi olla vaikeampaa saada muita hyötyjä neuvoteltua GF:n puolelta. WSA näyttää jättävän aika paljonkin tilaa neuvotteluille mutta samalla myös se on aika joustava eikä siinä suoraan sanottu GF:n olevan velvollinen kertomaan AMD:lle mikäli aikoo lopettaa 7nm prosessin kehittämisen. Siellä on erikseen käsitelty 7nm prosessi, hyvin joustavin sanamuodoin.

GF auttoi AMD:ta käyttämään myös TSMC:n tehtaita, syynä se ettei GF:n kapasiteetti riittänyt kaikkeen mitä AMD halusi. Edelleenkään siitä "GF kertoi AMD:lle etukäteen" hommasta ei ole mitään todisteita. Tuollainen olisi myös hyvin vaikea pitää salassa. Vaikeasti salassapidettävä asia josta ei minkäänlaisia huhuja eikä edes arvauksia etukäteen on nykyään aika harvinainen tapaus.

Myös TSMC:lla olisi varmasti mietitty mitä tapahtuu kun AMD yhtäkkiä haluaakin lisää kapasiteettia tuotteille jotka "pitäisi" valmistaa GF:lla :think:

Jos puhutaan Ryzenin ei APU versiota (ts ei GPU ydintä) niin onko sinulla hajua siitä minkälainen valmistus kustannusero voisi olla kahden versin välillä versio A käyttäisi samoja chipletttrejä kuin tuo Epyc2 ja siinä olisi vartavasteb Ryzeniä avrten suunniteltu köykäisempi io piiri ja versio B olisi täysin yhdelle sirulle suunnitelty 7nm Ryzen jossa kumminkin käytettäisiin niin suoraa tuota nykyistä CPU chiplettiä kuin voi suunittelun lähtökohtana.

Ts kuinka todennäköistä on valmistuskuntannusten kannalta se että Ryzen ei käyttäisi suoraan noita Epyc chippletttejä vaan olisi kokonaan erillinen piiri (sisältäen IO:n).

Koko prosessorin valmistuskustannusten kannaltahan se kokonaan erillinen Ryzen piiri on teitenkin halvempi mutta sitä käyttäen AMD menetää myös valmsituspuolen joustavuutta (Ryzen piiri ei kävisi Epyckiin ja Epyc piiri ei kävisi Ryzeniin) joten olisiko kustannussäästö niin suuri että AMD valitsisi sen tien.

Juu ihmiset vain sotkee mielessään toisistaan riipumattomia asioita kun Ryzenin teho on ollut riipuvainen muistikelloista joka vaikutta sen sisäiseen tiedonsiirtonopeuteen ts se muistipiirien muistikaista ei ole ollut mikään pullonkaula vaikka äkkiseltään päältäpäinkatsoen voikin tehdä selllaisen hätäisen johtopäätöksen.

Nää siun jutut on nyt viistossa. Jos GF:llä ei muka riittänyt kapasiteetti edes AMD:lle niin eikö silloin järkevintä olisi ollut lisätä sitä kapasiteettia eikä ohjata kilpailijan puheille.

Jos GF:llä ei kerta kapasiteetti riittänyt edes AMD:lle niin melkosen nyrkkipajan se toiminnasta antaa ja myös amatööri kuvan. Ei se varmaan nyt mitään rakettitiedettä vaadi että voidaan laskea paljonko kapasiteettia tarvii olla että päästään plussalle.

GF olisi mennyt vuosia siis tappiollisena jos kapasiteetti oli muka niin pieni ette AMD pelkästään olisi syönyt kaiken.

En kyllä nyt siihen sekoittanut, moni varmasti sekoittaa ihan ymmärrettävistä syistä.

Tuossa välissä olevassa postauksessani kerronkin, kuinka saatiin Xeon E5530:lla duunissa ihmetellä 30% tehoeroa kahden muuten identtisen koneen välillä, mutta toisessa oli 2 muistikanavaa kalustettuna ja toisessa 3. Muistin määrä ei vaikuttanut tuohon testiin, softa vaati testitilanteessa pyöriäkseen alle 2GB, mutta aiheuttaa ihan törkyisen määrän muistiliikennettä.

Nyt on duunissa alla 1920X, kaikki kanavat kalustettuna yhdellä kapulla. En ole viitsinyt testailla tehoeroja kalustamalla vain 2 kanavaa. Valiettavasti ei riitä aika tuollaiseen protoiluun, ollaan sen verran aliresurssoitu sw-dev yksikkö.

Ymmärrän kyllä mistä/miksi näkökulmasi tulee, mutta halusin nyt tuoda esille että olen liene se poikkeus joka vahvistaa säännön. 😉

Chiplet ei sisällä muistiohjainta ja Ryzen ilman prosessoriin integroitua muistiohjainta on ajatuksenakin täysin mahdoton. Ja jos laitetaan se muistiohjain prosessoriin, chiplet-systeemin hyöty on käytännössä olematon pienillä ydinmäärillä.

Kyllähän Ryzen piirit voivat edelleen käydä Epycceihin kuten käyvät tälläkin hetkellä. Tuo chiplet homma on tehty ratkaisuksi saada prosessorille iso määrä ytimiä jotka eivät tarvitse alhaisia muisti/IO-latensseja. Pienemmillä ydinmäärillä voidaan käyttää vaikka Zen1:sta copypastettua Infinity Fabricia tai jotain parempaa. AMD tulee lähes satavarmasti julkaisemaan Zen2 Epyccejä integroidulla muistiohjaimella, niissä ei enää puhuta chiplet rakenteesta ja mikäli AMD haluaa, niitä voidaan käyttää Ryzeneissä.

GF:lla oli kaksi vaihtoehtoa: 1. lisätään 7nm/5nm/…kapasiteettia tai 2. luovutaan kokonaan 7nm/5nm/… tuotannosta.

Kapasiteetin lisäyksessä on se ongelma että se maksaa. Ja kun kyse on 7nm kapasiteetista se maksaa Paljon. Kun kyse on 5nm kapasiteetista, se maksaa Todella Paljon. 3nm maksaa vielä enemmän…

7nm kapasiteetti ei riittänyt AMD:lle. Varmasti GF:lla juuri tuota laskettiin. Kapasiteettilisäys maksaa X ja tuottaa tuloja Y. Laskelman tulos: X<Y joten ei kannata.

GF:lla oli muitakin asiakkaita. Heidän 7nm kapasiteettinsa olisi AMD:lle riittänyt jos olisivat palvelleet vain AMD:ta ja unohtaneet kaikki muut.

Olisiko aika siirtyä takaisin aiheeseen, ihan sama mitä gf tai joku tehnyt tai ei tehnyt… Sille voi toki oman topickin tehdä

Huh! Aika jäätävät kellot! Sanoo vielä tuolla, että passiivijäähy, mutta TDP on kuitenkin 300 W.

Räkkipalvelimiin menevät kortit tuppaavat olemaan passiivisia TDP:stä riippumatta, koska kaikki siinä räkissä jäähdytetään perään asennetuilla turbiineilla

Huomaa ettet ymmärrä serverirautaa. 😀

Kortti passiivinen kun siellä on 8-10 kpl tuplatuuletinta puskemassa painetta koko koneen läpi. Koneen jossa voi olla helposti 4 tai 8 tuollaista korttia. Pelkät tuulettimet voivat viedä lähes 100W tehoa pyöriessään täysiä. 🙂

Toimistolla pelastin räkistä dadaa levyltä. Kerkesiköhän se perkele olla 5 minuttia käynnissä niin mun käskettiin painua kellariin pelastamaan dadaa. Tämä ei aina välttämättä kaikille ole ihan selvää miten nuo on jäähdytetty. Peltoreja tekee mieli kun lyö virrat päälle ja on samassa tilassa. 😉

Lue se minun hkultalalle suunnattu kysymys uudelleen kun et selvästikään tajunnut sitä (en missäänvaiheessa välttänyt että chiplettiä käytettäisiin Ryzenissä ilman IOta).

Sinä et selvästikkään tajunnun sitä että mikään ei estä chipletin/chiplettejen ja IO-osan integroimista yhdelle ja samalle piisirulle (AMD on puhunut paljon modulaarisesta CPU suunnitelusta ja siitä tuossa olisi nimenomaan kyse).

Ei serverivehkeissä ole koskaan pasiivijäähy se tuuletin on vain serverin rungossa kiinni ei siinä kortissa.

Aika monet muutkin suositut testit on aika kamalia. Phoronix test suite on enemmän moronix test suite. Geekbenchin tuloksetkin vaihtelee version mukaan ja ihmiset vertailee niitä keskenään. C-ray tosiaan mittaa jotain osia prosssorin liukuhihnasta, mutta ei maksimaalista suorituskykyä. Moronixin testeissä lame/flac-testit ajetaan aina yhdellä corella vaikka gnu parallelilla kaikkien ytimien käyttö olisi ihan simppeli one-liner ja mielenkiintoinen lisä. Kernelin käännöstä ei ole kerrottu, tehdäänkö se tmpfs:ssä vai onko kovalevy pullonkaulana. No, onhan sitten vielä bogo mips 😀

Enemmänkin.

https://store.supermicro.com/40mm-fan-0163l4.html

Tuollasia laikkoja kun lätkitään 10kpl niin haukataan 19A virtasta josta tulee 228W

Ah totta. Laskeskelin joskus aikanaan että nuo vie noin 1A per tuulari, mutta nyt unohdin laskea tuplatuularille tuplatehon, vaikka sen tuplatuularin itse viestissäni mainitsinkin. 😀

Toisaalta poimittua:

GPU-to-GPU kaistaa saatavilla IF-linkeillä 200 Gt/s eli ilmeisesti vähintään kaksi IF-linkkiä per Vega 20, osaa käyttää lisäksi PCIe-kaistaa jolloin teoreettinen maksimikaista korttien välillä on 264 Gt/s. Muistihakujen latenssi toisen GPU:n muistista 60-70ns

Ei, mutta muistiohjaimia ei voi enää viedä sinne lisätiedonsiirron aiheuttaman latenssin ja virrankulutuksen takia. Tämä chiplet-juttu toimii koska etäisyys chipletiltä IO-piiriin on jotain pari senttiä, niin AMD voi tehdä leveän väylän jossa virrankulutus per bitti on hyvin pientä.

Prossujen pitää sopia SP3-socketille, jossa on Epyc 1:stä varten suunniteltu virransyöttö. Virransyötön piuhat pitää vetää niin että pituus minimoituu ja että niitä ei tarvi vetää ristiin datapiuhojen kanssa (häiriöiden minimisoimiseksi). Niimpä chipletit on laitettu siihen missä zeppeliinit olivat.

Tämä on imho myös suurin syy epäillä että chipleteissä on PCI-E — se meinaan lähtee socketilta siitä missä chipletit ovat, niin jos se ei ole siinä se pitää sitten reitittää sinne IO-siruilta virran ja sen chiplet-IO linkin ohi.

Ei, mutta antoivat ottaa lähikuvan prossusta jossa selkeästi ei ole mitään interposeriin tai EMIB:iin viittaavaa.

Luokkaa 150-200mm^2. Se loppu on varmaan täynnä cachea.

IMHO nämä mahdollisuudet ovat niin todennäköisiä juurikin siksi että AMD:lla on jo yksikkö joka yrittää tälläistä kaupata. Ennen chiplettejä tuollaisella custom-piirillä on aika hemmetin kovat minimikustannukset, eli myyntiä tarvii paljon ennen kun kannattaa edes harkita. Nyt taas jos AMD pitää huolen että tuollaiseen chiplet <-> väylään pääsee hyvin kiinni, niin voi monia acceleraattoreita yms tekeviä yhtäkkiä himoittaa paljon pistää sellainen piirille, kun sitten voi myydä kovan luokan serveriprossuja joissa juuri se oma tiedonliikennenopeutin. Veikkaan että latenssit prossulle ovat aika paljon pienempiä kuin PCI-E:n yli.

Päivityssykli voi hyvinkin tuplaantua kun voivat todennäköisesti päivittää IO-piiriä ja prossua erikseen, ja varmaan kannattaakin vaihtaa ne uuteen aina vuorotellen. Eihän kuitenkaan ole aina pakko ostaa ihan sitä uusinta, jos ei koe että päivitys ei tuo tarpeeksi lisää tehoja :).

Siitähän tämän on tosi hienoa että kun vaihtavat DDR5-seen niin voivat vielä myydä uusimpia prossuja DDR4 IO:lla päivitykseksi niin kauan kun vaan markkinoita löytyy. Ei ihme, että uskalsivat luvata että AM4, SP3 ja SP3v2 saavat kaikki vielä monta päivitystä.

Veikkaan että threadripperit nimenomaan sisältää saman IO-piirin, ihan vaan siksi että jos yhdessäkin IF-linjassa tai muistiohjaimessa (tai PCI-linjassa, olettaen että ovat IO-piirillä) on virhe, ei piiriä voi myydä EPYCissä. Jos serveripuolen myynti kasvaa niin kuin olettaisin sen kasvavan, AMD voi tehdä kaikki Threadripperit EPYC-hylkiöistä. Tuon takiahan se 32-ytimen TR varmaan tehtiin, siinä sai kivasti rahaa siitä että pystyi myymään risat piirit.

ZRAM ei toimi enää moderneilla prosesseilla. Se ilmeisesti toimi jotenkin sillä vanhalla SOI-tekniikalla jossa sitä kehitettiin, mutta shrinkkaus ei onnistunut.

Jos haluaa noihin eksoottisempaa muistia, niin vaihtoehtoja on 2: 14HP:ssa on tarjolla eDRAM, joka voisi olla syy miksi IO-piiriä mainostetaan 14nm eikä 12nm piirinä.

Oma lempparivalintani olisi kuitenkin MRAM. GF kehittää sitä 22FDX ja 12FDX-tekniikoilleen. FDX on FD-SOI-tekniikka, mikä on parempi IO:n tarvitsemille analogisille komponenteille kun finfetit, ja jos siihen saa kestävää MRAMia, niin siihen mahtuisi myös enemmän cachea kun finfet-tekniikoihin.

Mitä AM4-chipletteihin tulee, niin kannattaa muistaa että on arvioitu että SOC-piirin kehittäminen 7nm prosessilla maksaa ~$300M per lastu. Itse koen että yhden piirin 7nm APU on mahdollinen, mutta jos AM4:seen tulee >8 coren prossuja, on ne väkisikin tehty chipleteillä. Ihan vaan siksi että markkinat ovat liian pienet että kannattaisi enemmin käyttää vähemmän piitä mutta enemmän eri 7nm piirejä.

Nykyinen "piirisarja" on kutakuinkin sama kuin south bridge aikoinaan. Ryzenit ovat olleet alusta lähtien SoCeja ja sen "piirisarjan" ainut tehtävä on tarjota olemassa olevien päälle vielä lisää liitäntöjä. Emot voisi rakentaa myös täysin ilman mitään piirisarjaa karsituin liitännöin.

EMIB ei näy päälle millään tapaa.

EMIB:ssä ei myös ole järkeä, mikäli piirit ovat kaukana toisistaan.

Koko homman idea on pienentää ”interposer” osan kokoa, joka pudottaa sen hintaa vs. Koko paketoinnin kokoinen interposer. Jos chipletit ovat valtavan paketoinnin kulmissa, pitäisi EMIB-palasten olla valtavan kokoisia, mikä tekisi niistä kalliita.

Ihan normaali paketointi tuo varmastikin on.

Mutta eikö noi tulokset kuitenkin olisi vertailukelposia saman kellotaajuden ja core-määrän sekä muistimäärän ja nopeuden omaavien EPYC järjestelmien välillä? Itse en ole noita testejä tosin nähnyt, joten ei tietoa, näyttääkö rome prossu liian hyvältä vai täysin epäonnistuneelta tuotteena.

Näyttää siltä että ovat saaneet mahdutettua yhteen sockettiin yhtä paljon/ vähän enemmän laskentatehoa kun mikä ennen vaati kaksi socckettia, ja tuplaten enemmän muistikaistaa.

Juuri noin kuvittelen sen itsekin tapahtuvan kun Ryzeneitä ilman iGPU:ta meni kaupaksi paljon koska ei ollut sitä iGPU:llista vaihtoehtoa aikaisemmin niin että nyt kun se on niin AM4 myynti tulee olemaan pääosassa niitä Ryzen Apuja joten nuo 6-16c AM4 Ryzenit tulee suhteessa pienestä myyntimäärästä johtuen olemaan paljon järkevämpää toteuttaa noila samoilla chipleteillä jotka on käytössä myäs Epyc ja Threadripper malleissa.

Eli kaikki 2 sukupolven AMD:n Zen2 pohjaiset prosessorin syntyisi kolmella eri piipalalla (Ryzen Apu piiri joka sisältää sekä ytimet että IO:n, Chiplet jota käytetään kolmessa eri prosessori tuoteessa ja sekä iso että pieni IO piiri joita yhdistellään eritavoin (IO piirejä voi mahdollisesi olla 3 jos Threadripper tarvii omansa eikä käytä Epyc versiota).

Ellei AMD tee jotain ihmettä ja saa tuota I/O-piirin muistilatenssia todella pieneksi, ei ole mitään pelkoa asiasta. AMD ei myöskään sanonut kaikkien Epyccien olevan chipletillä eivätkä varmasti olekaan, ellei sitä muistilatenssia saada hyvin lähelle nykyisiä lukemia.

Tuollaisesta 64-ytimen Epycistä voi pyytää ainakin 10K$ kappaleelta, siksi tuollainen kannattaa kehittää vaikka samaa rakennetta käytettäisiin vain siinä.

Ei tule toteutumaan ellei AMD jollain ihmeen konstilla pysty saamaan muistilantensseja kuriin. Kaiken järjen mukaan chipletissä muistilatenssit ovat todella suuret. Koko chiplet homma onkin tarkoitettu tilanteisiin joissa tarvitaan laskentatehoa muttei pieniä muistilatensseja.

Eli minä veikkaan kolmea eri rakennetta: Chiplet, nykyisen kaltainen CCX-rakenne jota käytetään muissa kuin chiplet prosessoreissa (Ryzen, Threadripper ja Epyc) ja sitten APU versio erikseen.

Haloo tuo chiplet + erillinen IO piiri on nimenomaan parempi Threadripperissä kuin nykyinen toteutus kun yhdenkään chipletin ei tarvi hypätä toisen prossu piirin kautta päästäkseen käsiksi muisteihin vaan kaikki chipletit on suoraan yhteydessä IO piirin jossa on se L4 puskuroimassa jotein vaika Threadripper2 prosessorissa on vain sama 4 musitikanavaa kuin aikaisemmissakin niin se on kumminki muistilatenseiltaan paljon parempi kuin nykyiset 32c Threadripperit.

Olen myös täysin valmis veikkaamaan että tuon IO piirin yksi tarkoitus on irtikytkeä muistien ja prosessorin sisäisten väylien riipuvuus toisistaan niin että ne musitiviive ongelman siltäosin poistuu.

Kun vaika tuo irtikytkentä aiheutaisi musitiyhteyteen lisäviiveen niin se kumoutuu jo sillä että kaikilla chipleteillä on suoraan näkyvissä kokko IO piirin musitikasta (ts Threadripperissä chiplet näkee suoraa 4 kanavaa ja Epycissä chiplet näkee suoraan 8 kanavaa).

Ts sinä messuat ongelmasta jonka nimenomaan tämä chipletit + IO piiri rakenne poistaa, eli täysin päivastoin kuin sinä väität tapahtuvan.

TR hyötyy siitä että saa yhtä paljon L4-kakkua kun mitä EPYC, puolta vähemmillä ytimillä, jolloin kasvanut muistilatenssi haittaa vähemmän.

Uskon että on mahdollista saada alemmas kun nykyisen. Chiplet<-> IO hyppy maksaa vähän, mutta nykyisen Ryzenin suurin akilleen kantapää on että se muistiohjain on oikeasti aika kuraa. Intel saa >20ns alemmat latenssit samoilla muistikammoilla, ennen kun edes otetaan klusterirakennetta mitenkään huomioon. Jos se muistiohjain on korvattu paremmalla, voi latenssi olla aina parempi kuin edellisellä Ryzenillä, io-piiristä huolimatta.

Sitten jos Zen2:selle tehdään erillinen APU, voisi se helposti olla linjan paras peliprossu jos se voittaa muistilatenssissa chipletversiot.

Entäs ne pienempiytimiset Threadripperit? Kannattaa muistaa että se 32-ytiminen "Threadripper" on todellisuudessa Epyc joka sopii Threadripper emolevyihin.

Sen tarkoitus on tasata muistilatenssit, eli kaikilta chipleteiltä on yhtä suuri latenssi keskusmuistiin. Huonona puolena muistilatenssit kasvavat lähes varmasti ja sen takia chiplet systeemi ei sovellu systeemeihin joissa pieni muistilantenssi on tärkeää. Lisäksi pienemmillä ydinmäärillä tuosta I/O piirista saatu hyöty muistihakujen synkkauksessa menee hyvin nopeasti lisääntyneeseen latenssiin.

L4 cachen olemassaolo on toistaiseksi spekulointia. Kasvanutta muistilatenssia ei muutenkaan ihan helposti korvata L4 cachella.

Ryzenin muistiohjain ostettiin muualta eikä siihen välttämättä olla tekemässä merkittävää parannusta vaan DDR5 muistiohjain on se johon AMD panostaa. Chiplet-I/O välin hyppy on latenssien kannalta sen verran suuri etten usko tuolla rakenteella päästävän samaan kuin Zeppelinillä vaikka kuinka viriteltäisiin muistiohjainta.

APU joka voittaa Ryzenit peliprosessorina on ajatuksena aika mahdoton koska silloin kukaan ei ostaisi "kalliita" Ryzeneitä vaan "halpoja" APU:ja. Juuri tuosta syystä on aika vaikea uskoa Ryzenin tulevan Chiplet versiona, ellei sitten AMD väännä jollakin magialla I/O piirin aiheuttaman latenssilisän voitoksi.

Ei ole (katso esim: Ber8aurerin röntgen kuvat).

Miksi sinä oletat että AMD:llä olisi pakottava tarve myydä "kallitta" Ryzeneitä peliprosessoreiksi "halpojen" Apujen sijasta.

Luulisi että AMD haluaa mahdollisimman suuren markkinaosuuden peliprosessoreista mahdollisiman suurella katteella eli se "halpa" Apu on se parempi vaihtoehto markkinaosuuden maksimoiseen, Intelin kyykyttämiseen ja AMD:n omien peliprosessori katteiden maksimoimiseen.

Itse oletan että uudessa 7nm Apussa tulee olemaan 8c toteutus koska siinä on vieläkin 2 kanavaiset DDR4 muistit niin GPU puolen kokoa ei ole järkeä paljoa kasvattaa (kaista ei riitä) mutta 8c prossu puoli mahdollistaa sen että Apu valtaa peliprossu puolen mellkein kokonaan joten se varsinainen iGPU:ton Ryzen jää marginaali tuotteeksi (selliseen käytöön jossa hyödytään suuremmista välimuisteista (joita ei Apussa ole)) ja siinä varsinaisessa Ryzenissä saattaa olla enempi kuin 8c (pelikäytössä enemmästä kuin 8c16t toteutuksessa ei ole hyötyä vielä muutamaan vuoteen).

On ja ei ole, itse piirit olivat täysin samoja 1st genissä, Threadripperistä vain kytketty kaksi sirua pois käytöstä. Kakkosgenissä olisi muuten sama (+uutena kaikki sirut käytöstä mutta parista kytketty osa ominaisuuksista pois), mutta Epyciä ei päivitetty Pinnacle Ridge -ytimiin.

3rd gen Threadrippereissä AMD:lla olisi mahdollisuus joko käyttää samaa metodia kuin 1st genissä (ts Epyc josta pari chiplettiä pois käytöstä ja I/O-piiristä osa ominaisuuksista disabloituna) tai vaihtoehtoisesti jättää osa chipleteistä latomatta alustalle.

Ryzen = 1 CCX

Threadripper = 2 toimivaa CCX:a (4 yhteensä)

Epyc = 4 toimivaa CCX:a

Sitten on se yksi poikkeus jossa 4 toimivaa CCX:a mutta vain 4 muistikanavaa. Menee paljon enemmän Epycin puolelle, vaikkei tietenkään ole Epyc koska 4 muistikanavaa puuttuu.

APU:a on aika hankala valmistaa halvemmalla kuin Ryzeniä sen grafiikkapiirin vaatiman tilan takia. Kun vielä näytönohjain rajoittaa prosessorin virrankulutusta kun sitä käytetään, AMD:n kannattaa suunnata pelaajille Ryzeniä josta saa selvästi suurempaa katetta. Ellei AMD sitten siirry linjalle jossa prosessoriin integroitu näytönohjain voi Intelin tapaan voi olla ennemminkin 3D-hidastin.

Pienempi ytimiset rojut syntyy helposti niin että laitetaan esim uloimpien chiplettien kohdalle täysin vialliset chipletit jolloin jäljelle jää 4 toimivaa eli max 32-core. Todella nerokas systeemi ja kuten aiemmin on todettu niin vialliset IO-ytimet voidaan myydä threadrippereissä joissa vaikka muistiohjain on paskana.

Cacheista ei vielä tiedetä juuri mitään, eikä sen puoleen latensseistakaan. Voi olla että chipletillä on L1, L2 ja jopa L3 ja IO:lla L4 tai sitten chipletillä on L1 ja L2 ja IO:lla L3. Katsellaan nyt kun tietoa tulee enemmän ja tuomitaan vasta sitten.

Epyc ja TR pohja ei ole sama vaikka ne toimisivat ristiin Epyc/TR emoissa niin niiden musitiväylä vedot on erit.

Sinä sivuutat täysin realiteetit.

Sellaiset pelikoneen ostajat jotka ostaa koneen jossa on iGPU:ton proseesori ovat todella harvinaisia.

Ts vaikka iGPU:to Ryzen olisi halvempi valmistaa sen kysyntä on määrällisesti niin valtavasti peinempi kuin Apu:jen että tuo kertaluokaero tekee iGPU:tomasta Ryzenistä pelikoneessa AMD:n kannalta kustannuksiltaan kallimman kuin se bulk Apu on.

Sinun ei pidä unohtaa sitä että pöytäkone myynti suhteessa kannettaviin on nykyäään häviävän pienin ja noista pöytäkoneista pelikoneita on vielä mitättömämpi määrä joten niille iGPU:ttomille peliprosessoreille on lähtökohteisesti todella marginaalinen kysyntä.

Ts vaika Apun valmistuskate olisi pienempi niin sillä ei ole merkitustä kun nitä Apuja myydään 100 tai 1000 tai 10000 kertaa enempi kuin iGPU:ttomia Ryzeneitä tuo valtava volyymiero tekee Apuista kokonaisuuden kannalta AMD:lle paljon kannattavampia.

Sitäpaitsi on AMD:n etujen mukaista että pelikoneissa käytetään Apuja iGPU:tomien prosessorejen sijasta koska se osaltaan autaa heikentämään Nvidian markkinaosuutta eli AMD puskee varmasti Apuja OEM:eille paljon enempi kuin iGPU:tomia Ryzenejä (joiden pariksi voi päätyä Nvidia näytönohjain siihen pelikoneeseen).

Chiplet rakenteessa tuskin tarvitsisi edes "täyttää" niitä tyhjiä kohtia viallisilla. Zeppelin pohjainen Threadripper oli tuote jota ei alunperin pitänyt edes tulla.

Latensseista ei tiedetä varmasti mutta mikäli ulkoisella muistiohjaimella saisi pienemmät latenssit kuin prosessoriin integroidulla, niin kehitys lähtisi yhtäkkiä kulkemaan vastakkaiseen suuntaan kuin mitä on menty viimeiset 15 vuotta.

CCX:n osalta pohjat ovat samat. Ja koska ennen sitä yhtä poikkeusta pystyttiin CCX:n määrällä määrittelemään onko Ryzen, Threadripper vai Epyc, ei noin hyvin toimivaa luokitusta kannata heittää roskiin yhden poikkeuksen takia.

Pelikoneiden ostajat ostavat pääasiassa vähintään kuuden ytimen prosessoreita eivätkä käytä sitä integroitua näytönohjainta vaikka sellainen olisikin. AMD ei vieläkään ole julkaissut yli 4-ytimistä prosessoria integroidulla näytönohjaimella eikä Intelkään sitä tehnyt vuosiin. Coffee Lake poikkeuksena koska Intel ei halua luopua linjauksesta jossa LGA11xx kannan prosessoreissa on aina integroitu näytönohjain. Ihan mutunakin helppo väittää suurimman osan Intelin 8-ytimisen LGA1151 prosessorin ostajista jättävän integroidun näytönohjaimen käyttämättä eikä heitä tippaakaan hetkauttaisi vaikka se näytönohjain prosessorista puuttuisi. Ihan kuten aikakautena jolloin 6+ ydintä sai vain LGA20xx alustalla tai vielä kalliimmalla.

Mikäli AMD jatkaa samalla linjalla kuin Zeppelinin kanssa, eli samaa CCX:a (tai jopa chiplettiä) käytetään kautta linjan Ryzeneissä, Threadrippereissä ja Epyceissä, silloin nimenomaan APU on se joka joudutaan tekemään "erillisenä" tuotteena ja voluumiero tekee nimenomaan APU-piireistä vähiten kannattavia.

Prosessorin valmistuskustannsu ei ole yhtäkuin pelkkien piisirujen valmistuskustannus.

Apussa on yksi alusta ja yksi piisiru.

Jos Ryzen tehdään Chipleteillä niin siinä on vähintään alusta 2 Chipletiä ja IO piiri eli sen valmistus on paljon monimutkaisempaa = kallimpaa.

Ts normaaleihin kuluttajatuotteisiin/pelikoneisiin AMD:n ei kannata tyrkyttää Chiplet pohajaista Ryzeniä koska se on AMD:lle kallimpi kuin Apu josa olisi 8 ydintä ja suht iso iGPU.

Ota huomioon että on vielä vuosia siihen että kuluttajat on valmiita maksamaan AMD tuotteesa enempi kuin Intel tuotteesta joten se "yber hieno" Chiplet Ryzen ei voi olla erityisen kallis vaiikka se kilpailisi Intelin 8c kiuasta vastaan joten AMD:n täytyy aina myydä tehoa halvemmla kuin mitä Intel myy, ts AMD:n täytyy puskea Apuja niin suurella volyymillä kuin suinkin vain voi vallatakseen mahdollisimman suuren markkinaosuuden Inteliltä.

Jos AMD haluaa myydä yritysmaailmaan muutakin kuin tehotyöasemia tai servereitä niin silloin niistä on löydyttävä iGPU. Ei paljon auta että rusina on halvempi kun se ero ulosmitataan pakollisella erillisnäytönohjaimella. Silloin on sama ostaa inteliä kuten ennenkin.