AMD on esitellyt Next Horizon tapahtumassaan ensimaistiaiset tulevista prosessoreistaan ja laskentakorteistaan. Sekä tulevat grafiikkapiirit että prosessoriytimet valmistetaan TSMC:n 7 nanometrin valmistusprosessilla.

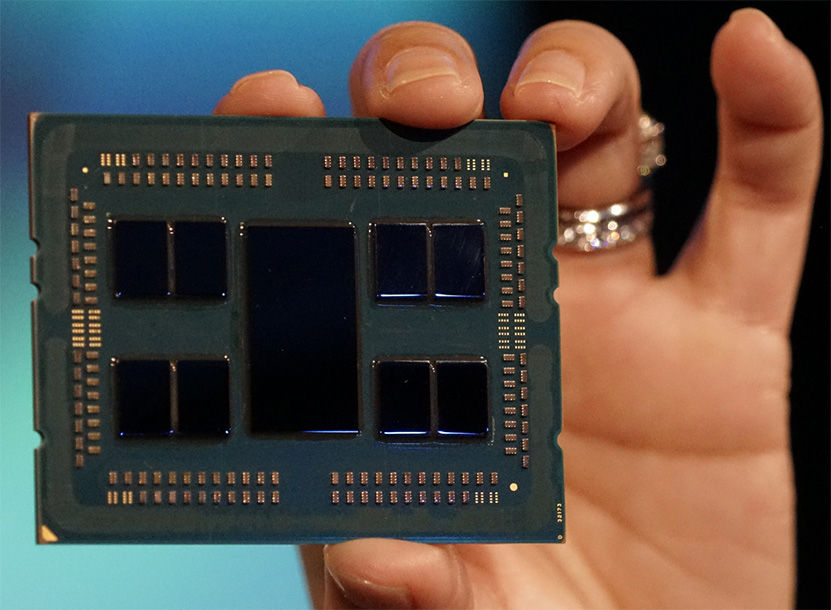

Illan päätähti oli Zen 2 -arkkitehtuuri ja siihen perustuvat Rome-palvelinprosessorit. AMD jatkaa odotetusti useamman piirin ratkaisulla, mutta vie sen vielä astetta pidemmälle. Rome-prosessoreissa on reunoilla yhteensä kahdeksan 7 nanometrin prosessilla valmistettua CPU-pikkupiiriä ja keskellä 14 nanometrin prosessilla valmistettava I/O-piiri. Yhteen Multi Chip Module- eli MCM-paketointiin on saatu näin sovitettua 64 ydintä. Prosessoriytimiin on tehty huomattavia muutoksia muun muassa kaksinkertaistamalla liukulukuyksikön leveys ja kasvattamalla välimuisteja.

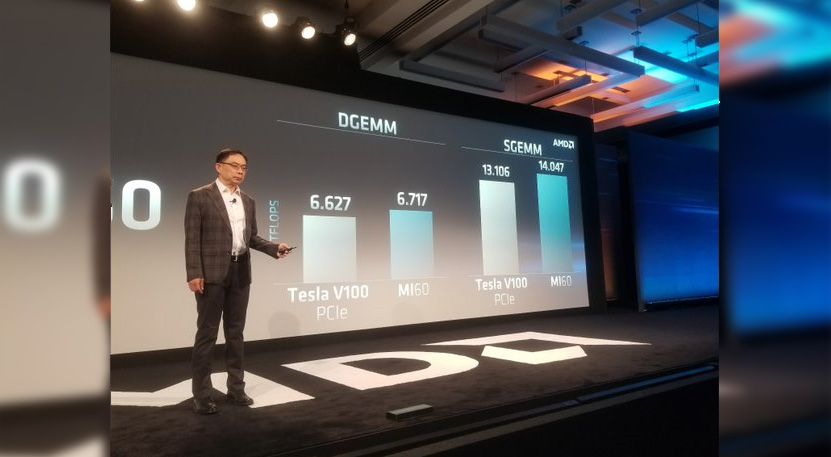

Vega 20 -koodinimellä aiemmin tunnettu grafiikkapiiri on paitsi maailman ensimmäinen 7 nanometrin grafiikkapiiri, myös ensimmäinen PCI Express 4.0 -standardia ja piirien välistä Infinity Fabric -linkkiä tukeva GPU. 13,28 miljardin transistorista rakentuvan piirin kooksi kerrotaan 331 mm2. Huhujen mukaisesti grafiikkapiiri tarjoaa 1:2-suhteen perus- ja tuplatarkkuuden laskuille. Radeon Instinct MI60 -huippumallin luvataan tarjoavan 14,7 TFLOPSin edestä laskentavoimaa FP32-tarkkuudella ja 7,4 TFLOPSia FP64-tarkkuudella, mikä riittää AMD:n testien mukaan Tesla V100:n PCI Express -version peittoamiseen DGEMM- ja SGEMM-testeissä. Muistikaistaa grafiikkapiirillä on käytössään teratavu sekunnissa ja sen 4096-bittisen muistiväylän jatkeena on 32 Gt HBM2-muistia. Radeon Instinct MI60:n rinnalle julkaistaan myös kevyempi MI50-vaihtoehto.

Julkaisemme huomenna AMD:n Zen 2 -prosessoreita ja Vega 20 -grafiikkapiiriä sekä niiden tuomia muutoksia tarkemmin käsittelevän uutisartikkelin.

Lähde: Tom’s Hardware

Kovasti amd tuntui mainostavan am4 tukea pitkälle tulevaisuuteen, joten oletan että tulee vielä yli 8 corea am4:lle. Nuo johtimet (ja bios tuki) on varmaan isoimmat rajoitteet. Kalliimman pään levyillä varmaan ihan kivasti toimii, kuten ryzen 2000 sarjakin.

Sehän tässä jännittää. Nyt tulee B-die muisteilla seinä vastaan 3444-14… ja nimenomaan CPU on pullonkaula. Jos ne vaikka saisi kulkemaan 3600-15 tms.

Tuohon core määrän kasvattamiseen AM4lle suhtaudun skeptisesti. En usko että virransyöttö on mitoitettu alkuunkaan siihen.

7nm ja "samat kellot puolella teholla". 😉

Ensimmäisen sukupolven AM4 emolevyt taisivat vaatia BIOS-päivityksen, jotta Ryzen 2xxx-prossut alkoivat toimia. Samalla tavalla käy varmaan Zen2-prossujen kanssa ja siinä BIOS-päivityksen yhdeydessä voidaan myös varmistaa, että emolevy joko ei tue liian paljoa virtaa vaativia prosessoreita tai niille asetetaan tehonkulutuksen osalta tiukemmat rajat (mikäli AMD:llä on mahdollista rajoittaa tehonkulutusta).

Redditissä oli ketju, missä sanottiin "7nm offers 2x density, 0.5x power (at same perf), 1.25x perf (at same power)".

Jos tuo pitää paikkaansa, niin 10-ytiminen Zen2 kuluttaisi samat tehot, kuin 8-ytiminen Zen1.

No se nähdään sitten mitkä kellot ja millä tehoilla. Olen täysin tietoinen valmistusprosessin teoreettisista parannuksista mutta suhtaudun silti tuohon coremäärän kasvattamiseen skeptisesti. Pessimisti ei pety!

Verrattuna mihin? Aika alakanttiin ovat lukemat. TSMC sanoo noin:

10nm: With a more aggressive geometric shrinkage, this process offers 2X logic density than its 16nm predecessor, along with ~15% faster speed and ~35% less power consumption.

7nm: Compared to its 10nm FinFET process, TSMC’s 7nm FinFET features 1.6X logic density, ~20% speed improvement, and ~40% power reduction.

Jos oletetaan TSMC 16nm = GF 14nm, niin saadaan:

Tiheys ~3,2x

Power ~0,4x (at same performance)

Performance ~1,35x (at same power)

Niin noh.. serveripuolella juuri tuplattiin coremäärä samalla socketilla ja tukee myös vanhoja kokoonpanoja. Mahdotonta paljon kevyemmän am4 kanssa? 😀

Eihän se mahdotonta ole, mutta ellei infinityfabric ole huomattavasti edistynyt voi syödä jopa tehoja kun prosessit lyvittäytyvät ties kuinka monelle ccx:lle ja ilman niitäkin ongelmia tehojen hyödyntäminen kaksikanavaisella muistilla on melko haaste.

Lähinnä mainoskikka että on eniten coreja kuluttajalankulla sanoisin, jos tuovat enemmän kuin 8.

Näin minäkin näkisin. Lisäksi tuo veisi turhaan markkinoita Threadripperin seuraajalta (Castle peak?). Pelaajia kuitenkin kiinnostaa lähinnä se, että mitä tuloksia pelitesteissä tulee.

Mielestäni tähän ei vastattu myös sitä, että sähkö kulkee käytännössä valonnopeudella. Eli etäisyyden muutos millimetreinä on latenssin yms. kannalta täysin merkityksettömiä. Toki signaalin voimakkudelle noilla etäisyyksillä on merkitystä.

Tuo oli näytönohjaimeen liittyen, ei prosessiin. Lisäksi kyseiseen näytönohjaimeen tehtiin muutakin kuin pelkkä die shrink.

Sähkön kulkemisen kannalta kyllä juuri näin. Mutta fyysisesti pidemmät johtimet tuovat sitten mukanaan induktanssia, kapasitanssia ja resistanssia eli ei haluttuja parasiittisia signaalin laatua huonontavia tekijöitä. Signaalit vaimenevat, kytkeytyvät viereisiin johtimiin, räpisevät ja tekevät kaikkea muuta ei toivottua suurilla nopeuksilla.

Fyysisesti lyhyemmän matkan yli on helpompi suunnitella nopea ja matalaviiveinen väyläratkaisu oli tekniikka mikä hyvänsä.

Chiplettien sijoittelu kauemmas I/O-lastusta on ilmiselvien jäähdytyshyötyjen lisäksi helpompi routata paketin piirilevyllä.

Kun ei ole pii-interposeria vaan hartsialusta, jolloin tilaa tarvitaan melkoisesti vetojen fan outille piirin alta ja routtaukselle, kun valmistusteknologia ei kykene lähellekään niin tiheään routtaukseen (+ei voi käyttää niin äärimmäisen nopeaa sarjaväylää kuin piillä voisi, luultavasti joku leveämpi ja selvästi hitaampi väylä käytössä -> huomattavasti enemmän vetoja piirilevyllä).

Käytettävissä on yhteensopivuussyistä valtavan kokoinen paketti, ja toki sitä silloin kannattaa käyttää hyödyksi.

Pikakatsaus Zen 2:n, Romen ja Vega 20:n uudistuksiin – io-tech.fi

Alkuperäisen ja tämän uuden uutisen keskustelu on yhdistetty tähän ketjuun.

Kyllä varmaan nämä tulee yhden soketin ratkaisuissa kulkemaan ilman NUMA joka on merkittävä parannus myös koska NUMA toi omat ongelmansa tiettyihin kuormiin.

Onko tuo vahvistettu jossain että nuo chipletit sisältävät sen 2 CCX:ää? Lisäksi ainakin Anandtechissä väitettiin että PCI-e linjat olisivat myös noissa chipleteissä, onko tästä varmaan tietoa suuntaan tai toiseen?

Tulevissa kuluttaja version (AM4) Zen 2 prosessoreissa käytetään varmana yhtä tai kahta tuolaista CPU chiplettiä mutta tuleekohan niiden GPU puoli erillisenä chiplettinä vai tuleekohan kulutajaversiosa olemaan tuo uncore piiri sellainen että se sisältää myös GPU ytimet (jolloin se ei teitenkään voisi ola 14nm piiri vaan se uncorekin olisi 7nm).

Mukana on tietenkin osittain tulkintaa siitä mitä on kerrottu.

AMD ei ole millään tasolla ilmaissut että chipleteissä olisi mitään I/O:ta, joten sitä voitaneen pitää hyvin epätodennäköisenä.

Koska Rome-piirissä on 64-ydintä ja 8 CPU-chiplettiä, tiedetään että niissä on jokaisessa 8 ydintä. 8 ytimellä CCX:ssä tulisi ongelmaksi crossbarin toteutus, jolloin 4 ydintä per CCX kuten ennenkin on ainut looginen vaihtoehto.

Ei kumpaakaan ole virallisesti vahvistettu. Molemmat valistuneita arvauksia jotka saattavat olla pielessäkin.

Minä taas veikkaan ettei Ryzeneissä ole mitään chiplettiä eikä näitä siruja käytetä ollenkaan kuluttajaluokan prosessoreissa vaan vastaavaan tapaan kuin nykyRyzeneissä laitettu prosessoriytimien yhteyteen uncoret. Tuollainen kahden piirin systeemi kuluttajaprosessoriin on liian kallis ja muistin kannalta liian hidas.

Toinen vaihtoehto olisi crossbarista luopuminen ja vaihtaminen esim. jonkinlaiseen meshiin kuten Intelillä, varmaan jossain vaiheessa siitä crossbarista pitää kuitenkin luopua skaalautumisen parantamiseksi.

Silloin AMD menettäisi täysin nykyisen synergiaedun kun samaa piiriä ei voisi käyttää kaikissa sen tuotteissa, kun ottaa huomioon että AMD on hyvin voimakkaansti painottanut tätä etua aikaisemmin epäilen että ei se nyt olisi siitä luopumassa.

Varsinkin kun tuollainen GPU chiplet voisi jossian laskentakäytössä olla hyvinkin järkevä ratkaisu.

Tosin tuollainen 2 kanavainen muisti jarruttaa niin paljon grafiikkasuorituskykyä, ettei mielekkäästi sillä toimiva gpu olisi 14nm prosessillakaan erityisen iso. Osin tämä cpu-chiplet kun voisi johtua kapasiteetin rajallisuudesta ja halusta maksimoida 7nm piikiekkojen hyödynnys- käyttäen kapasiteettia siihen missä siitä on selkeimmin hyötyä.

Mikäli pystyvät gpu chiplettejä hyödyntämään jossain muussakin kuin APU:issa on sekin kai ihan mahdllista

Kaikki Zeppelin-pohjaiset piirit valmistettiin samassa tehtaassa.

Zen2-pohjaisia piirejä piti valmistaa GF:lla ja TSMC:lla.

Helppo sanoa ettei AMD:lla ollut suunnitelmissa miksata GF:n ja TSMC:n valmistamia piirejä keskenään. Siksi TSMC:lla voitiin suunnitella yhtä käyttötarkoitusta varten Zen2-pohjaista piiriä, eli juuri julkaistua Epycciä.

Tämä on puhtaasti omaa spekulaatiotasi.

Kaikkien mahdollisten lähteiden perusteella AMD ei ollut suunnitellut mitään merkittävää GloFon 7nm:lle (vielä) tai sen perumisesta tiedettiin jo niin kauan sitten, ettei sen peruminen käytännössä vaikuttanut yhtään mihinkään.

Eiko AMD:llä ollut hallussa se yksi toinenkin L4 muistiksi käyvä muistipatentti (olikohan sen nimi Zsram tms en muista) voisikohan tuo IO piiri sisältää senkaltaista L4 muistia.

Mahtaako tuolle olla tarvetta ja toisaalta xbarilla viive CXX:n corejen välillä on yhtenäinen, useamman hopin verkkotopologiassa sitten tulee vaihtelevia viiveitä, joka taas aiheuttaa päänvaivaa softa tasolla jos halutaan optimoida suoritusta. Toki sama sama juttu pätee 2 CXX välillä, mutta niissä vielä on helppo tehdä rajaveto 4 askelin, että mihin ryhmään/nodeen mikäkin core kuuluu.

Kohta puoliin alle 4C prossuja ei liene kovin paljon saa myytyä, joten sen tarpeen täyttää niillä joissa CXX on vähän vioittunut ja 2C lyödään pimeäksi. Ylöspäin taas deskari markkinoilla ei ole tarvetta ihan hirveästi scaalata, kahdellakin chipletillä/Zen tyyppisellä piirillä 16C asti, joka jo jokseenkin järjetöntä ennekuin AM4 kanta jää pois, koska muistikaista alkaa ahistaa.

Työasema ja serveri lastuissa taas on sen verran varaa nostaa hintaa, että homma ratkeaa I/O piirillä. Ja jos tekevät useamman erilaisen I/O piirin niin silläkin voi markkinasegmentoida vielä. Sinänsä siis tuo 4C per CXX ja 2 CXX per chippi on ihan ok kokoinen, aina tulee paskoja piirejä niin voi sitten tehdä vähempi coreisia malleja kuten nytkin.

Itse kuvittelisin tuon suureltaosin IO piirin suuren koon syyksi kun Intel ei lisensoi EMIBiä ja AMD kumminkin halusi välttää Interposerin käytön niin IO piirin täytyy olla fyysisesti iso että sen ja kotelon välille mahtuu ne kaikki tarvittavat kytkennät.

Oikeasti luotettavien lähteiden (Globalfoundries ja AMD) perusteella AMD:n piti valmistaa GF:lla 7nm piirejä. Eli mitä piirejä? GF:n prosessin piti mahdollistaa korkeammat kellotaajuudet kuin TSMC:n prosessin, joten on hyvin helppo arvata niiden prosessorien olleen Ryzeneitä tai Threadrippereitä.

Lisäksi Epyc prosessorien validointiin menee kuukausikaupalla enemmän aikaa kuin työpöytäprosessorien, josta voidaan suoraan päätellä Ryzenien julkaisun riippuneen vain ja ainoastaan siitä milloin GF saa 7nm tuotannon kuntoon ja tavaraa ulos.

Ja koska AMD myös sanoi GF:n oharien jälkeen siirtävänsä kaiken CPU tuotannon TSMC:lle (tämäkin luotettavasta lähteestä), sekin kertoo AMD:n aikoneen valmistaa GF:lla tuotteita. Virallista tietoa ei ole siitäkään tiesikö AMD GF:n ohareista kovinkin aikaisin. Sehän nähdään kun "Ryzen 3:" julkaistaan. Koska palvelinkaman validointiin menee karkeasti puoli vuotta enemmän kuin työpöytäkaman, Ryzen on Epycin julkaisuhetkellä puoli vuotta myöhässä. Jos se siitä myöhästyy vielä lisää, on helppo arvata mistä viivästys johtuu.

AMD ei ole ikinä sanonut mitä tuotteita ja milloin se aikoisi valmistaa GloFon prosessilla, eli jälleen mennään omaan spekulaatioosi.

No ei tietenkään voida, koska ei tiedetä onko AMD suunnitellut mitään 7nm Ryzeneitä GF:n prosessille ikinä.

AMD ei sanonut siirtävänsä yhtään mitään, vaan kertoi että kaikki yhtiön 7nm piirit tehdään TSMC:llä.

AMD on sanoi valmistavansa prosessoreita GlobalFoundriesilla, se ei ollut spekulaatiota. Koska AMD sanoi hyvissä ajoin valmistavansa Epyccejä TSMC:lla, GF:lla valmistettavien prosessorien vaihtoehdoiksi jäävät Ryzen, Threadripper ja APU:t. Ja milloin? Onhan teoriassa mahdollista ettei AMD ajatellut valmistaa GF:lla ennen heti kun 7nm prosessi toimii kunnolla. Mahdollista mutta …

No siitä ei olekaan faktaa tiedossa, vain spekulaatiota. Tässä jää kaksi vaihtoehtoa:

– Kaikki Zen2-pohjaiset tehdään samalla kaavalla kuin Zen2-Epycit.

– Epycit tehdään eri tavalla kuin osa muista Zen2-piireistä.

Jos alempi vaihtoehto osoittautuu todeksi JA Ryzenit tulevat vasta reilusti Epyccien jälkeen, se kertoo aika paljon. Vaikkei tietenkään ole faktaa ellei AMD sitä suoraan sano.

AMD aikaisemmin: Valmistamme 7nm prosessoreita GF:lla. Valmistamme 7nm prosessoreita TSMC:lla.

AMD myöhemmin: Valmistamme kaikki 7nm prosessorit TSMC:lla.

Eli GF:n 7nm tuotanto siirtyi TSMC:lle.

ZRAM oli muistityyppi, jonka jotkut muistisuunnittelijat keksivät baari-iltansa päätteeksi kännissä, jatkoivat idean kehittämistä selvinpäin, perustivat firman(Innovative Silicon) ja onnistuivat lisensoimaan sen muutamalle valmistajalle (mm. AMDlle), mutta se ei kuitenkaan koskaan toiminut riittävän luotettavasti kunnollisessa mittakaavassa, että sitä olisi oikeasti voinut käyttää missään. Firma meni nurin, micron osti firman patenttisalkun firman mentyä nurin, mutta micron ei ole yrittänyt markkinoida zramia mihinkään.

Ei siis ole koskaan tulossa zramia mihinkään.

Nyt kaivataan niitä linkkejä sitten jo.

https://www.eetimes.com/document.asp?doc_id=1332049 – Esimerkiksi tässä CTO Papermaster ei sano sanallakaan GloFolla valmistettavista tuotteista, lähimmäs menee kun se kehuu että sekä GloFo että TSMC on tehneet paljon töitä 7nm:n prosessien eteen

Oma muistikuvani on, että AMD on toki puhunut paljon 7nm yhteistyöstä myös GloFon kanssa, muttei ole ikinä sanonut valmistuttavansa yhtään mitään tuotetta siellä (edes tasolla "valmistetaan siellä prossuja")

Ryzen 3000-sarja voi myös tulla ulos EPYC2n jälkeen yksinkertaisesti siitä syystä, että AMDllä on rajallinen määrä piirisuunnittelijoita sekä piirien syntetisointiin käytettävää laskentakapasiteettia, ja AMD päätti priorisoida näiden käytön seuraavaan järjestykseen:

1) EPYC

2) Ryzen

3) Ryzen APU.

(ja Vega 20n piirisuunnittelu pystyttiin tekemään näitä aiemmin koska sen arkkitehtuuri valmistui aiemmin, sen kanssa ei tarvinnut prioritisoida)

Ja tämä EPYCin priorisoiminen "7nm"llä ennen ryzeniä sopii hyvin yhteen sen kanssa, että "zen+"-skipattiin EPYCeissä kokonaan.

AMD:n toimitusjohtaja haastattelussa:

Getting Radeon Vega Everywhere: An Exclusive Media Interview at AMD Tech Day, with CEO Dr. Lisa Su

AMD käyttää molempia, joo, ei täysin suoraan sanota CPU:sta GF:lla. Joten otetaan se CPU GlobalFoundriesin suusta:

https://www.eetimes.com/document.asp?doc_id=1332049

Eli GlobalFoundries sekä sanoo AMD:n prosessorin tape outin olevan tulossa ja että se on ensimmäinen mitä tape outataan GF:n 7nm prosessilla. Joka kertoo AMD:n halunneen prosessorin GF:lta ulos nopeasti. Ja koska aiemmin AMD:n tj sanoi tekevänsä eri tuotteita TSMC:lla ja GF:lla, se CPU ei ollut (tai pitänyt olla) Zen2 Epyc vaan joku muu.

Ennemminkin tuossa priorisoitiin valmistustekniikan taholta. TSMC:n prosessin tiedettiin olevan valmis ennen GF:n prosessia, joten siellä päätettiin tehdä Epyccejä joiden kohdalla 12nm hypättiin yli. Piirisuunnittelun suhteen Zen2 Epyc toi ison määrän muutoksia. "Ryzen 3" ei periaatteessa olisi vaatinut uncoren osalta juuri muuta kuin PCI Express linkit 4.0 versioon ja loput "copypastella". Ehkä muutekin mutta joka tapauksessa erittäin helppo tapaus Epycciin verrattuna.

Tuo GlobalFoundriesin väittämä kuulostaa kieltämättä erittäin suoralta, joskaan sekään ei automaattisesti tarkoita että kyse olisi Ryzenistä.

Mutta , kuka valmistaa näitten Zen2 laitteiden muistiohjaimet ?

Varmaankin se joka tekee I/O piirit…jos sitä tarkoitat?

Eikä varmuutta ole, että muissa kuin epyceissä olisi erillinen I/O.

Niin noh jos tuolle linjalle lähetään niin sitten se muistikaista alkaa ahistaa myös Romessa.

16/2=8

64/8=8

Mahtaakohan tuosta nyt unehtua se ihan alku kun AMD jutteli vain GF virityksistä? Sitten mukaan astui TSMC ja lopulta jäljelle jäi vain TSMC.

Meinaatko että GF:lle olis ollut täysin fine että AMD joka oli GF:n talutusnuorassa aika tehokkaasti olisi sanonut GF:lle että joo nyt on semmone homma pojat et me ostetaan nyt TSMC:ltä kapasiteettia. Tai no toki olisi ollut varmaan GF:lle kun olisivat saaneet ilmasta rahaa, mutta olisiko se ollut järkevää AMD:n kannalta?

Kyllä AMD tiesi GF:n suunnitelmat jo paljon ennen tuon TSMC yhteistyön julkaisua ennen. GF dumppasi varmaan 7nm osin siitä syystä että ei ollu tarpeeksi asiakkaita. Ei ollut kuin AMD ja IBM ja niillä ei vielä kapasiteettia olisi poltettu kaikkea joten tappiollista toimintaa olis ollut.

–

Ekoja testejä odotellessa =) Ihan mielenkiintoinen paketti.

Tällä kaverilla on muitakin mielenkiintoisia videoita. Ennusti Ryzen 2 huippukelloiksi 4,8 GHz ihan uskottavilla todisteilla.

Saisko tekstimuodossa esimerkkejä niistä todisteista?

Vähän hankala puhelimella.

Mutta kyse oli prosessorin rakenteesta ja arkkitehtuurimuutoksista ja sitten se vertasi vega radeonin kellotaajuuksien muutoksia kun mentiin 7nm nodelle.

Valitettavasti ensimmäinen testi on jo tehty, ja se tehtiin ehkä maailmankaikkeuden huonoimmalla testiohjelmalla: c-ray:llä. Onneksi niitiä tuloksia ei ole kauheasti pastettu minnekään, koska ne eivät kerro yhtään mitään näiden suorituskyvystä millään järkevällä softalla.

C-ray on softa, joka on aivan todella kamalaa koodia suorituskyvyn puolesta. Se laskee tuplatarkkuuden liukuluvuilla asioita, jotka voisi laskea floateilla. Se on kirjoitettu siten, että sitä ei voi vektoroida, joten käytännössä siis 256-bittisestä tai 512-bittisestä laskentayksiköstä on käytössä vain alimmat 64 bittiä (laskemassa asiaa, jonka voisi laskea alimmilla 32 bitillä). ELi siis käytetään vain kuudestoistaosa jonkun skylake-SPn , kahdeksasosa skylaken tai zen2n ja neljäsosa zenin laskentakapasiteetista.

Taisi siinä olla pari muutakin todella suuren luokan typeryyttä, mutta ne olen jo unohtanut.

C-Raytä ei siis alunprin kirjoitettu testiohjelmaksi EIKÄ oiekasti tuotantokäyttöön tarkoitetuksi koodiksi jota käytetäisiin mihinkään oikeaan, vaan "opetuskoodiksi" joka tarkoituksella jätetiin optimoimatta yhtään, jotta se olisi mahdollisimman helppo ymmärtää. Ja sitten jotkut idiootit teki siitä benchmarkin.

Odotellaan siis niitä toisia testejä 😉

Tarkoitinkin kunnon testejä, syvä analyysiä =)

Ei AMD:n tai sen käyttämät piiritehtaat ole immuuneja fyysikan esteille. 5Ghz hetkellinen kellotaajuus yhdellä (tai max kahdella) ytimellä on toki mahdollista (vrt. Intel). Siitä eteenpäin, AVX-käskysarjoilla ja kaikki ytimet kerralla – no way.

Uskottavia todisteita tuo video ei ole nähnytkään, kunhan vaan oikaistaan mutkat. Siinähän mainittiin että kaikki on lopulta täysin auki ja eikä voi tehdä arvioita siitä mitä tuo valmistusprosessi lopulta tuo. Eli vaikka mitä laskuja teki niin täysin mutua vielä.

Ja ennenkuin joku valittaa niin muistutan että ilmaisen vain mielipiteeni. 😀

Täysin eri tyyppisen piirin (Vega) kellotaajuuksien muutoksesta ei voi vetää mitään johtopäätöksiä toisenlaisen piirin kellotaajuuspotentiaaliin.

Vega 20 ei ole myöskään identtinen Vega 10n kanssa joten prosessin vaikutuksen arviointi niiden välillä on parhaimmillaankin vain suuntaa antavaa