AMD on esitellyt Next Horizon tapahtumassaan ensimaistiaiset tulevista prosessoreistaan ja laskentakorteistaan. Sekä tulevat grafiikkapiirit että prosessoriytimet valmistetaan TSMC:n 7 nanometrin valmistusprosessilla.

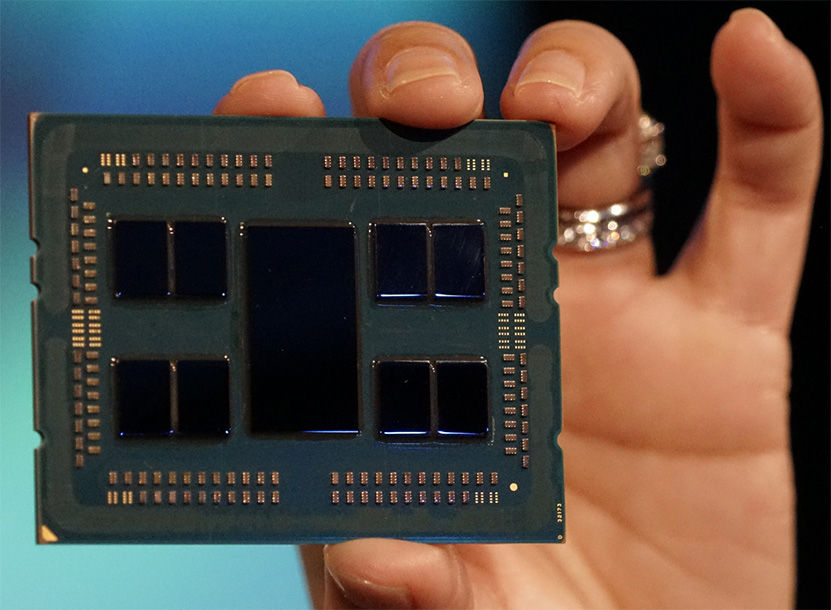

Illan päätähti oli Zen 2 -arkkitehtuuri ja siihen perustuvat Rome-palvelinprosessorit. AMD jatkaa odotetusti useamman piirin ratkaisulla, mutta vie sen vielä astetta pidemmälle. Rome-prosessoreissa on reunoilla yhteensä kahdeksan 7 nanometrin prosessilla valmistettua CPU-pikkupiiriä ja keskellä 14 nanometrin prosessilla valmistettava I/O-piiri. Yhteen Multi Chip Module- eli MCM-paketointiin on saatu näin sovitettua 64 ydintä. Prosessoriytimiin on tehty huomattavia muutoksia muun muassa kaksinkertaistamalla liukulukuyksikön leveys ja kasvattamalla välimuisteja.

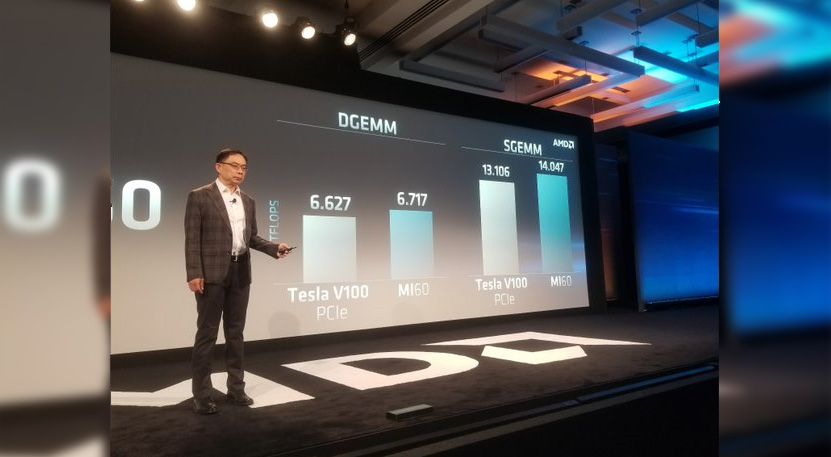

Vega 20 -koodinimellä aiemmin tunnettu grafiikkapiiri on paitsi maailman ensimmäinen 7 nanometrin grafiikkapiiri, myös ensimmäinen PCI Express 4.0 -standardia ja piirien välistä Infinity Fabric -linkkiä tukeva GPU. 13,28 miljardin transistorista rakentuvan piirin kooksi kerrotaan 331 mm2. Huhujen mukaisesti grafiikkapiiri tarjoaa 1:2-suhteen perus- ja tuplatarkkuuden laskuille. Radeon Instinct MI60 -huippumallin luvataan tarjoavan 14,7 TFLOPSin edestä laskentavoimaa FP32-tarkkuudella ja 7,4 TFLOPSia FP64-tarkkuudella, mikä riittää AMD:n testien mukaan Tesla V100:n PCI Express -version peittoamiseen DGEMM- ja SGEMM-testeissä. Muistikaistaa grafiikkapiirillä on käytössään teratavu sekunnissa ja sen 4096-bittisen muistiväylän jatkeena on 32 Gt HBM2-muistia. Radeon Instinct MI60:n rinnalle julkaistaan myös kevyempi MI50-vaihtoehto.

Julkaisemme huomenna AMD:n Zen 2 -prosessoreita ja Vega 20 -grafiikkapiiriä sekä niiden tuomia muutoksia tarkemmin käsittelevän uutisartikkelin.

Lähde: Tom’s Hardware

AMDlla tuntuu kyllä menevän aika lujaa prossupuolella atm. Miettii että millainen tilanne oli se 3-4v sitten, niin aika kummasti tuntuu asetelma kääntyneen kun nyt puolestaan Intel junnaa paikoillaan 10nm prosessin kanssa eikä tunnu olevan helpotusta tiedossa vielä hetkeen. Saas nähdä miten käy, mutta ainakin tämä uutinen antaa aika hyvää kuvaa tulevasta AMDn suhteen etenkin prossupuolella.

Intelin 48 corea vanhentui sitten samantien 😛 (No joo, voittaa se edelleen jotkut yksittäiset testit, mutta tuskin kovin montaa) Harmi kyllä että (odotetusti) ei tullut peli GPU uutisia…

Joku näppärä tyyppi vois tehdä pikasen arvion tuon I/O-sirun koosta, näyttää aivan jäätävän kokoselta kuvassa. Silmämääräsesti katottuna tuo näyttäs isommalta kun nykyset Zeppelinit, olis varsin mielenkiintosta tietää et mitä kaikkee ne on tuonne tunkenu.

Koko entisen uncoren, kasan Infinity Fabric -linkkejä ja 8 muistikanavaa

Karkea arvio TR4/SP3 pohjalta on 350 mm^2 IO-siru ja 70 mm^2 ydinsirut. Tarkkuus luokkaa +-15%.![[IMG]](https://i.imgur.com/uQS39oG.png)

Nykyinen Epyc oli 4 x 213 mm^2 sirua.

I/O-lastu lienee houkutteleva paikka laittaa mittava määrä välimuistia myös.

Eikö tuo 68×50 ole liian pieni TR4:lle? Tuon kuvan arvioilla olisi yhteensä "vain" 910mm^2, Ian mainitsi että yhteenlaskettuna pinta-ala on nelinumeroinen.

Väittelyketjusta.

Juu, tuonkokoisella piirillä voisi helposti olla kymmeniä megatavuja, ehkä yli satakin megatavua L4-välimuistia. Mutta noissa slideissä ei kuitenkaan ilmeisesti sanottu mitään siihen viittaavaa.

Kiinnostaisi tosiaan lukea tarkempia tietoja tuosta.

Näinköhän AMD on päättänyt muuttaa politiikkaa ja siirtyy kolmen piirin tuotantoon: Ryzen uncorella, CPU chipletit ja I/O piiri? Eli Ryzen kotikoneisiin ja kaikki muu kasataan CPU chipleteistä ja I/O piiristä?

Tai I/O piiristä tulee lite versio ryzeniin ja cpu chipletit on yhteisiä.

Tuplapostaus.

Ratkaisu siirtää IO pois CPUsta voi olla ihan järkevä, ainakin saannot luulis olevan ihan kunnossa, kun lastusta saadaan vieläkin pienempi uudella valmistusprosessilla. Oliko 7nm-prosessilla tulossa ollenkaan APU-piiriä? Siinä luulis viimeistään tarvitsevan IO:n samalle kivelle, kun työpöydällä voidaan vielä järkevästi ulkoistaa se piirisarjalle, kuten on tehtykkin, vaikka Summit/pinnacle ridge SOCceja ovatkin.

Nyt viimeistään kannattaa käydä katsomassa AdoredTV youtube videot epyc masterplan ja chiplets. Siellä on hyvin lisätietoa miksi nämä chipletit on hyviä ja esimerkiksi miksi tuo IO siirrettiin omalle piirille.

Täytyy sanoa että Intelin 2×46 corea on aikamoinen purkka verrattuna tähän. 😀

Neljän. Ryzen uncorella ja näyttiksellä.

Tapahtuman presis-dekki (slides):

AMD Next Horizon

Taitaa adoredin setti olla puhdas kopio siitä tovi sitten netissä pyörineestä jonkun insinöörin julkaisemasta konseptista mitä hänen mukaansa AMD tulee tekemään? Siinä oli toki chipletit eri sijoituksilla kuin lopullisessa mutta kuitenkin

Tuo on muuten hyvä huomio. 7nm prosessi on varmaan pullonkaula tuotantokapasiteetin suhteen, joten sillä tuskin kannattaa tuottaa muuta kuin nuo coret ja 14nm kapasiteettia pitäisi olla kyllä hyvin tarjolla kaikelle muulle.

Nyt vain odotetaan tietoa siitä miten hyvin tuo chiplet rakenne toimii. Jos se pelaa kuten AMD kaavailee, niin Intel on oikeasti kusessa, koska silloin monoliittipiirien aika on ohi ja juna meni Intelin nokan edestä ja jätti laiturille.

Mihin tuota toista lastua edes työpöydällä tarvitaan? Perinteisistä piirisarjoista ei ole vissiin vielä luovuttu?

CPU chipletissä on vain coret. Jossakin sen I/O:n pitää olla ja ainakin minusta piirisarja on liian kaukana.

Käytännössähän tämä on vain sen piirisarjan siirtäminen sen CPUn kanssa fyysisesti samaan pakettiin. Ja paluu siihen, että muistiohjaimet on piirisarjalla eikä CPUlla.

Mietityttää, että jääköhän erillisen I/O-lastun myötä NUMA-arkkitehtuuri yhden sukupolven välivaiheeksi yhden prosessorikannan ratkaisuissa?

Se 7 nm ei myöskään oikein auta mitään tuon I/O:n osalta kun ne analogiapuolen osat tarvivat fyysistä kokoa paljon enemmän. Voipi olla jopa päinvastoin, jos/kun analogiapuolta ei ole ehditty kehittää tuolle 7 nm sirulle vielä yhtä valmiiksi. Vähän kyllä ihmetyttää eikö tuo 14 nm piiri sisällä mitään (merkittävää) muuta, kun sitä I/O:ta pystyy laittamaan vain piirin reunoille.

Ei, ollut käytössä jo kolmessa aivan eri arkkitehtuurissa yli kahdeksan vuoden ajalla

AMD's 12-core "Magny-Cours" Opteron 6174 vs. Intel's 6-core Xeon

http://www.legitreviews.com/images/reviews/1741/amd-fx-zambezi-17.jpg

Tuosta I/O piiristähän ei kovin paljoa puhuttu ja minua ei yhtään ihmetyttäisi vaikka siellä olisi kaikenlaista muutakin kivaa kuten esim. täällä spekuloitua cachea. Ei AMD:n kannata kaikkia kortteja vielä nyt lyödä pöytään vaan odottaa milloin todellisuus valkenee Intelille.

Veikkaisin siinä olevan L3 cachen ja L1/L2 on chipleteissä. Fiilispohjalta ryzen menee myös io-lite sirulla ja siihen varmaan lisätään grafiikkapiirikin APU kiville. Jos noin käy, niin on jännää nähdä korkkauskuva, kun coret olisi saatava kai keskelle, jotta olisi paras kontakti prossujäähyihin.

Siihen en ota kantaa, että onko tämä kuin lähellä todellisuutta, mutta mielenkiintoinen kuva nakattu tonne spekulaatioketjuun.

![[IMG]](https://bbs.io-tech.fi/attachments/upload_2018-11-7_8-33-54-png.156233/)

Taitaa olla jonkun spekulaatiota.

Se, mikä tässä hyppii silmille on eDRAM. En tuomitse varmuudella vääräksi, mutta käsittääkseni tuolla Samsung-johdannaisella "14nm" prosessilla millä AMDn aiemmat piirit on tehty, ei eDRAMia tehdä.

Tämän Samsung-johdannaisen prosessin lisäksi GFllä on kuitenkin myös IBMltä peräisin oleva "14HP"-prosessi, jolla eDRAMia voidaan tehdä.

Se, että tämän IO-piirin sanotaan kuitenkin olevan tehty nimenomaan "14nm" eikä "12nm" prosessilla voisi vihjata siihen suuntaan, että tässä käytetäänkin tuota IBMltä peräisin olevaa "14HP" prosessia eikä Samsungilta lisensoitua ja siitä jatkokehitettyä "14nm/12nm" prosessia, jolloin eDRAM olisi mahdollinen.

Kukaan ei tainnut tuolla tilaisuudessa tajuta kysyä, kummasta "14nm" prosessista oli kyse.

L3 on varmasti chipleteillä myös, koska

1) Zenin arkkitehtuurissa on joka CCXlle erikseen eikä mikään vihjaa siihen että tätä oltaisiin muuttamassa. Vaatisi melko suuria muutoksia väyläarkkitehtuuriin muutaa tätä.

2) Sen oleminen tuolla IO-piirillä tekisi siitä latenssiltaan liian hidasta

3) Sen oleminen tuolla IO-piirillä kuormittaisi selvästi noita IO-piirin ja chiplettien välisiä väyliä, niistä tarvittaisiin järeämmät ja lisäksi sähkönkulutu slisääntyi.

4) SRAMia on ihan hyvä valmistaa uusilla valmistustekniikoilla, sen koko pienenee mukavasti.

Sen sijaan siellä IO-piirillä voi olla L4-välimuisti.

Mikäli tuossa io-piirissä on reilummalti välimuistia, sillä kai voivat hieman vähentää intelin useamman muistikaistan tuomaa etua. Näppärä ratkaisu minusta tehdä io erilliselle piirille, kun kuitenkin on tarkoitus monesta sirusta kasailla. Saa käytettyä parhaiten sopivaa prosessiakin.

Tästä kuvasta mulla tuli heti monta kysymystä mieleen mitä heittää ilmoille.

1. Osaako kukaan viisaampi sanoa miksi kaikki nuo neljä 2 ytimen rypästä ovat keskenään ihan toisissaan kiinni, mutta jätetty noin iso rako I/O lastun ja toisten ydinryppäiden välille? Eikö olis ollut fiksumpaa ihan vaan latenssien ja signaalivahvuuksien vuoksi lyttää kaikki ihan toisiinsa kiinni kun ne johtimet kuitenkin kulkevat siellä aluslevyllä? Päälle vielä IHS niin voila. 🙂

2. Onko AMD sanonut onko alla interposer, EMIB vai ihan perinteinen johdinpolku?

3. Osaako kukaan sanoa kuinka paljon 8x muistinohjaimet, L4 cache ja muu I/O vie tilaa tuolta I/O lastulta? Mietin vaan sitä että voisko mahdollisesti mukana olla pieni GPU jolla voitaisiin antaa vähän lisää pontta openCL:n muodossa?

4. Tämä uusi MCM valmistusmallihan antaa mahdollisuuden vaikka tunkea suuren määrän tensor coreja niitä kaipaaville laskentatieteilijöille, tai koko systeemiähän voi pienellä muokkauksella modaa vaikka mihin suuntaan semi cutom puolella.

Mielenkiintoiset ajat edessä todellakin. Taitaa mennä Ryzen 3000 sarja tilaukseen kun selvästi taklattu ryzen 1:sen pullonkauloja ja aika koneen päivitykselle on. Mutta tämä uusi MCM ratkaisu voi myös tarkoittaa sitä että ryzen 3k sarja varmaan jää aika lyhyt ikäiseksi kun takaa puskee jo 7nm+ valmistuksella tehty zen 3 piiri missä entisestään paikattu pullonkauloja ja uusi I/O lastu lisää tuen DDR5:lle ja PCI-E 5:lle varmaan aika piakoin. Voisko olla niin että AMD:tä seuraavaksi syttetään siitä että päivitys sykli muuttuu liian nopeaksi? 😮

Kun mitään L4 cachesta ei edes mainittu, ei ole mitään mahdollisuutta tietää. Sitä muistiahan voidaan tunkea vaikka kuinka ja paljon. Se lienee kuitenkin selvää, ettei pelkkä I/O noin paljoa tilaa varmaan kaipaisi ja lisänä on jotakin.

PCIe 5.0ssa mennään vasta 0.7 draftiversiossa, ei kannata pidätellä henkeä tuon kanssa. PCIe 4 julkaistiin puoltoista vuotta sitten ja nyt tulee eka sitä tuleva rauta.

Muistipuolellakin muistaakseni yleensä aika pitkät viiveet ennen kuin otetaan uutta käyttöön.

Mutta eiköhän AMD pyri julkaisemaan uuden Ryzen sarjan joka vuosi

A) Mitä kauempana ne on toisistaan, sitä helpompi ne on jäähdyttää, kum lämpö jakautuu isommalle pinta-alalle. Heatspreaderit eivät ole täydellisiä.

B) Kaikki liikenne chiplettien välillä ei välttämättä kulje IO-piirin kautta, vaan voi olla, että chiplettien välillä on myös suoria linkkejä. Jotkut paketin puolelta toiselle menevät suorat linkit voi olla helpompi tehdä kun piilastujen väliin jää vähän tilaa. Tästä en kuitenkaan ole varma.

Käsittääkseni ei ole sanottu. EMIBiä pidän hyvin epätodennäköisenä, se on käsittääkseni vain intelillä tällä hetkellä oleva tekniikka.

Systeemissähän käytännössä tarvii jossain olla joku pieni GPU että saadaan sen verran asioita näytölle, että saadaan käyttöjärjestelmä asennettu jne. Tällainen GPU voi kuitenkin olla _todella_ pieni, ja yleensä se palvelinkoneissa on kai emolevyellä joku todella pieni erillinen piiri. Tällainen mahtuisi ihan minne tahansa, ja sen laittamisessa tuonne voisi olla jotain järkeä.

Sen sijaan sen kokoinen GPU, että siitä olisi hyötyä numeronmurskauksessa – en näe järkeä laitta tuonne IO-piirille.

A) Noissa 64ssä zen2-ytimessä on yhteensä suurin piirtein saman verran numeronmurskausvääntöä kuin polaris 10:ssä, ja ainakaan mitään polaris 10n tehoista näyttistä sinne ei mahtuisi. ELi se näyttis olisi siinä numeronmurskauksessa heikompi kuin ne CPUt, mikä tarkoittaisi, että alle puolet laskettavasta kamasta pitäisi offloadata näyttikselle ja reilut puolet pitää CPUlla, ja molempien käytäminen samaan tarkoittaisi heti load balancing-ongelmia näiden välillä.

B) Suurin osa workloadeista, mitä noilla ajetaan, EI osaisi kuitenkaan käyttää sitä näyttistä. Jolloin se olisi siellä suurimalle osalle asiakkaista aivan turhaan.

A) Ei tämä oleellisesti muuta tätä. AMD on ennen tehnyt ja on tekemässä custom-piirejä, joissa on samalla piirillä zen-CCX sekä näyttisytimiä yms.

B) Ja tensoriytimet eivät kelpaa "laskentatieteiljöille", mitä ikinä niillä tarkoitatkaan. Tensoriytimet kelpaavat ainoastaan tekoälyjuttuihin.

Esomerkiksi siihen, että itseajava auto tunnistaa tiellä liikkuvat muut kulkijat osaatkseen väistää niitä, ja liikennemerkit jne.

Tai että googlen kuvahaku osaa luetella kuvat niidein sisällön perusteella ja hakea tietyllä sanalla olevia kuvia. Tai että kiinan isoveli valvoo-järjestelmä osaa tunnistaa epäilyttävien henkilöiden naamat miljoonien valvontakameroiden kuvista ja seurata näiden liikkeitä.

C) AMDllä ei tällä hetkellä ole valmiina omaa tensori-/tekoäly-ydintä. Ja se, että Vegaan 20:een on tulossa normaaleihin shader-ytimiin matalan tarkkuuden konvoluutiota/pistetuloa kiihdyttäviä käskyjä, eli että AMD pyrkii ajamaan tekoälykoodia normaaleilla Vegan Shadereilla ja muuttamaan niitä paremmin siihen soveltuvaksi vihjaisi siihen, että niitä ei aivan pian ole tulossakaan.

Missään ei ole kerrottu kuluttajamallien tulevan MCM-ratkaisuna.

Vain kaksi muistikanavaa sisältävä IO-piiri olisi aika helposti "liian pieni" IO-piiri ollakseen järkevä erillispiirinä, eikä AM4-kanta tue enempää muistikanavia. Ja kuluttajapuolella muistin viiveillä on enemmän väliä kuin palvelinpuolella (jossa kaista merkkaa enemmän) ja erillinen IO-piiri kuitenkin pakosti lisää muistin viivettä.

Mutta en sano varmuudella mitään suuntaan tai toiseen.

Ja pcie express 5n tuloa pian pcie xpress 4n jälkeen tosiaan hypetetään mutta sillä on vielä mahdollisuus myöhästyä paljon. Enkä näe muutenkaan peruskuluttajalla suurta tarvetta siihen. Että ihan turhaa alkaa vielä miettimään sen tuloa.

Tuskin tuolla mitään GPU:ta on kun kannassa ei taida olla pinnejä video ulostuloille?

Juu eiköhän ne ole emoilla

Estäisiköhän mikään sitä, että olisivat siirtyneet 8 ytimen ccx:iin? Tuli vain mieleen, että noi kaksi chiplettiä kylki kyljessä voisi olla samaan tyyliin suoraan yhteydessä toisiinsä kuin vanhemmilla piireillä kaksi 4 coren ccx:ää.

8 coren ccx antaisi kuluttajapuolella melko paljon mahdollisuuksia eri käytössä oleville ydinmäärille (varsinkin jos AM4 ydinmäärää ei kasvateta kahdeksasta). Lähinnä Oem puolelle voisi tulla jotain hassuja 7 core yms virityksiä viallisista piireistä.

Suuri L4 välimuisti taitaa tosin kuluttajasovelluksissa olla lähinnä (kallista) turhaa painolastia.

Eihän tuo mikään kuluttajaprossu olekaan, vaan raskaimman pään palvelinprosessori.:p

Ei estä, mutta olisi siinä haittapuolensa.

Neljän ytimen ja niiden välimuistin välille saadaan vielä hyvin nopea kytkentä crossbarilla, suuremmalla määrällä crossbar alkaisi helposti käydä isoksi/kalliiksi/virtasyöpöksi/hitaaksi , ja toisaalta kytkentätyypin vaihtaminen joksikin muuksi kuin crossbariksi hidastaisi sitä liikennettä siellä CCXn sisällä.

Crossbarissa siis kokonaiskytkentöjen määrä nousee O(n^2) eli linkkimäärän kaksinkertaistuessa kytkentämäärä n. nelinkertaistuu.

Mielenkiintoista nähdä mitä sieltä tulee suorituskyvyn suhteen. Mikäli parantavat muistiohjainta niin mahtaneeko 3xx-sarjalaiset AM4 emot jo olla pullonkaula? Olisi omasta mielestä mahtavaa jos tämän vielä saisi kohtuullisen hyvänä pelkkänä CPU päivityksenä omaan kokoonpanoon, menettämättä koko potentiaalia.

Ei, mutta täällä vedetään kovasti yhdysmerkkejä myös seuraaviin työpöytä zeneihin.

14nm IO palan uudelleen suunnittelu ja valmistus on niin paljon halvempaa mitä 7nm, että todennäkösesti sama jatkuu myös am4 puolelle. Siihen vielä lisättynä ettei 7nm kyseisessä piirissä skaalaa lähellekkään yhtä hyvin. Mielenkiintoisena kohtana oli "doubles the bandwich/channel", ei ainakaan olisi huono apu:a ajatellen tai thredripperiä.

Jos kyseessä on IBMltä peräisin oleva "14HP" prosessi niin ei sekään halpa ole. SoI ja selvästi enemmän metallikerroksia kuin Samsungilta peräisin olevissa prosesseissa.

öö? missä noin sanottiin?

Juu. Tuo voi olla ihan aiheellinen huoli, kun eikös jo nää ryzen 2000-sarjalaiset ole vähän muistisuorituskyvyssä vanhemmilla emoilla sen armoilla kuinka hyvin kyseinen valmistaja alunperin toteutti johtimet.

Hah. Samalla I/O palikalla tuskin ainakaan threadripperiä keveämpiä nähdään ja epäilisin, että niillekkin ehkä tekevät oman I/O-piirinsä, kun ei ole kuin neljä muistikanavaa ja

PCIE linjojakin murto-osa.

Joskohan tulisi sit Threadrippereille ja Ryzeneille (mikäli erillisellä I/O piirillä) samsungin 14nm prosessilla, kun ei edrammia niin kuluttajahärppeissä kaivata.:think:

Erilliset piirit mahdollistavat kaikki tämmöset kikkailut…

Olisiko sekotettu keskusteluun FPU:n muuttumisesta 128bit->256bit.

Varmaan.

Eli kun SIMD-datapolut levennettiin 128->256 bittiin, samalla levennettiin myös L1D-välimuistista ytimen datapolulle tulevat väylät 128->256 bittiin, jotta (L1D-välimuistiin osuvista) lataus- ja tallennuskäskyistä ei tule pullonkaulaa SIMD-suorituskyvylle.

Tällä ei ole mitään tekemistä tuon IO-piirin kanssa eikä ulkoisen DRAMin kaistan kanssa.

öö? missä noin sanottiin?[/QUOTE]

Slideissä oli mainittuna, voi olla että tarkoitti pci4. Samaan aikaan kyseltiin miten aikoivat pitää kaikki coret täydellä syötöllä muistien puolesta. Eivät suostuneet vastaamaan arkkitehtuurin puolesta mutta totesivat kaistan piisaavan kaikille ytimille.

pci expressin versiolla ei myöskään ole mitään tekemistä muistikaistan kanssa. Vaan sen kanssa, mikä on kaista eri laitteiden välillä. Eli esimerkiksi CPUn ja GPUn välillä tai CPUn ja massamuistilaitteiden välillä.

En mä niin väittänytkään. Eiköhän tuo kaikille ole selvää mihin pcie kaista vaikuttaa. Meni vaan asiat sekaisin kun näyttivät kuvaa missä oli double bandwich ja samaan aikaan puhuivat muistikaistasta.

Tuo 14nm tökkäsi itsellekin silmään, kun AMD on muuten mainostanut nyt tätä 12nm prosessia.

Glofon "12nm" prosessilla tuskin tulenee kapasiteettipulaa prossusirujen valmistuksen alkaessa siirtyä TSMC:lle Zen2:n myötä.

Ja nykyisten Zen1 Ryzenien myynnissä tuskin enää tullaan mitään piikkejä näkemään.

Merkkikonevalmistajien joulumyyntikoneisiinkin menevien prossujenhan pitäisi varmasti alkaa olla jo toimitettuna.