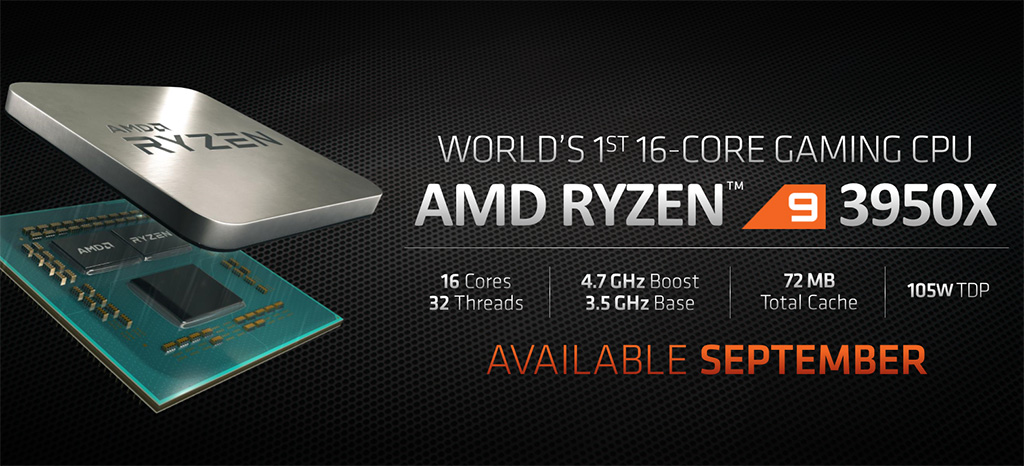

AMD lanseerasi kesäkuun alussa Computex 2019 -messuilla uudet 3. sukupolven Ryzen-prosessorit ja tuolloin tulevaa mallistoa esiteltiin 12-ytimiseen Ryzen 9 3900X -prosessoriin asti. Yhtiö yllätti E3-messujen yhteydessä Los Angelesissa kertomalla tuovansa markkinoille myös 16-ytimisen Ryzen 9 3950X -mallin, joka saapuu myyntiin syyskuussa 749 dollarin hintaan.

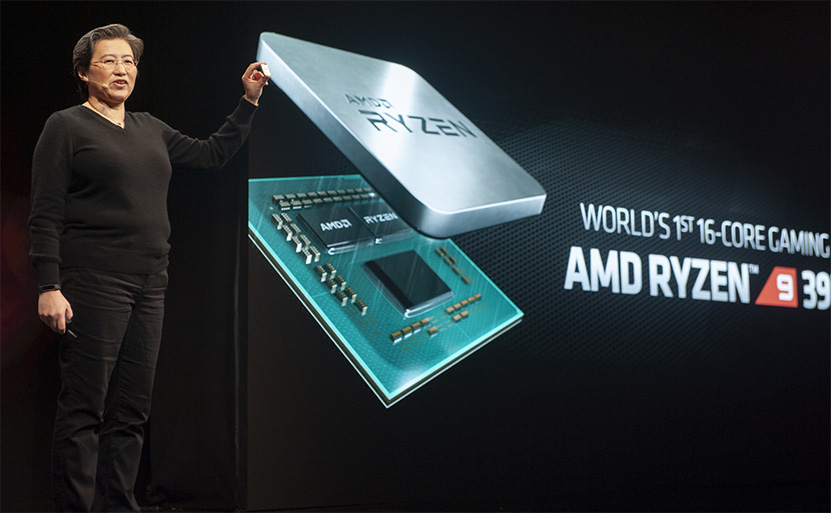

AMD:n toimitusjohtaja Lisa Su totesi medialle, että yhtiö ei aio jäädä odottelemaan Intelin seuraavaa prosessorijulkaisua, vaan tuo pelaajille, striimaajille ja sisällöntuottajille suunnatun AM4-kantaisen 16-ytimisen työpöytäprosessorin markkinoille pikimmiten. Luvassa ovat myös uudet Zen 2 -arkkitehtuuriin pohjautuvat Threadripper-tehoprosessorit HEDT-alustalle, mutta ne julkaistaan myöhemmin.

16-ytiminen ja SMT-ominaisuudella 32 säiettä tukeva Ryzen 9 3950X toimii maksimissaan 4,7 GHz:n Boost-taajuudella ja sen perustaajuus on 3,5 GHz. Välimuistia on yhteensä 72 megatavua ja prosessorin TDP-arvo on 105 wattia.

Suorituskyvystä annettu vielä tarkempia tietoja.

Los Angelesissa AMD esitteli Ryzen 9 3950X -prosessoria pelikäytössä jäähdytettynä Noctuan NH-D15-coolerilla.

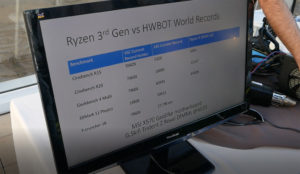

16-ytiminen Ryzen 9 3950X oli esillä myös ylikellotusdemossa, jossa sitä jäähdytettiin nestemäisellä typellä. Prosessorilla saavutettiin uudet maailmanennätykset 16-ytimisten prosessoreiden kategoriassa muun muassa Cinebench R15- ja R20- sekä Geekbench 4 -testissä. Prosessori toimi testeissä noin 5,35 GHz:n kellotaajuudella, kun kulhon lämpötila oli -150 astetta ja käyttöjännite 1,75 volttia. G.Skillin DDR4-muistit toimivat testeissä DDR4-4533-nopeudella 1,5 voltin käyttöjännittellä.

Yleisellä tasolla nuo odotukset alhaisemmista kellotaajuuksista liittyvät siihen, että pienempään prosessiin siirryttäessä maksimi käyttöjännite laskee, joka rajoittaa kellotaajuutta:

katso liitettä 238877

Epäselväksi jäi se missä vaiheessa mitäkin päätettiin. Ei kovin uskottavalta kuulosta seuraava: tehdään Zen niin nopeasti kuin pystytään käyttäen kaikkia mahdollisia kompromisseja ja sen jälkeen mennään min 3 vuotta ilman arkkitehtuuipäivityksiä. Jos Zen2:n ei pitänyt tulla arkkitehtuuripäivityksiä, ne piti tulla aikaisintaan Zen3:n.

Eiköhän WSA:lla (sillä oli satojen miljoonien-miljardiluokan merkitys vuodessa) ja GF:n prosessin ominaisuuksilla ole selvästi enemmän painoarvoa kuin yksittäisen työntekijän sanomisilla :think:

Tuossa näyttäisi kellotaajuus nousevan :confused:

Tuossa testissä on kyllä kummallisen matalat muistikaistat 4-channel Intelille AMD:n 2-channel Ryzeniä vastaan. Muutenkin Intelin muistikellot ovat paljon alemmat jne.

En pitäisi testiä ehkä ihan parhaana mittarina millekään, vaan odottaisin ihan kiltisti niitä sampsan kunnollisia testejä.

Tuossahan nimenomaan sanotaan, että perinteisesti pienempään prosessiin siirryttäessä jännitettä on pitänyt nostaa ja tätä kautta kellotaajuudet ovat laskeneet. Käppyrät kuvaavat, että AMD on onnistunut tästä huolimatta nostamaan kellotaajuuksia vastoin odotuksia.

Siis siinä todettiin paikkansapitäväksi, että piirin kestämä maksimijännite on perinteisesti laskenut uuden prosessinmyötä. Vähemmän jännitettä -> vähemmän kelloja. Uusi prosessi voi muuten olla parempi, mutta tuota jänniteongelmaa ei pääse karkuun millään.

Toi on nyt vähän tuollaista osatotuuksien kertomista.

Prosessin pieneneminen laskee jännitteitä, joo. Se taas laskee kellotaajuuksia, koska matalammalla jännitteellä virrat laskevat ja transistorien hilakapasitanssit latautuvat hitaammin. Mutta prosessin pienentäminen myös lyhentää etäisyyksiä (resistanssi laskee) ja pienentää transistoreja laskien niiden samaisia hilakapasitansseja -> nostaa kellotaajuutta koska aikavakio (RC time constant – Wikipedia) lyhenee.

Yhteisefekti on sitten joko ylöspäin tai alaspäin. Ennenvanhaan se oli paljon ylöspäin, nykyään ollaan oltu enemmän +- 0. Yksi syy, miksi nykyään on vaikeampaa on, että etäisyyden lyheneminen ei välttämättä laske enää laskekaan resistanssia, koska johtimen kaventuminen nostaa sitä enemmän.

2015 ei ole kyllä voinut olla mitenkään tiedossa 7nm todellinen kellotaajuuspotentiaali kuin korkeintaan toivotaan toivotaan asteella. Ja tuolloinhan muutenkin suunniteltiin täyttä häkää vielä GloFon prosessille.

Suunniteltiinko? Kai sinulla joku muu lähde tälle on kuin "koska AMD:n piirit tulivat pääosin glofolta silloin"?

Jos muistan oikein niin oli puhe late 2015 (tai 2016) kun oli päätetty toteuttaa myös IPC-parannuksia Zen 2 -arkkitehtuuriin. Silloin taidettiin olettaa että 7 nm kellot laskee (GF), ja suunnitteilla oli tuoda ainakin aluksi vain palvelimiin. Jossain kohtaa (TSMC 7nm siirtyminen?) todettiin että kellot onkin mahdollista saada ylös ja tuodaan myös Zen 2 työpöydälle, jopa ennen Romea (Epyc 2).

Näitä keskusteluita ei käyty kovin spesifisellä tasolla (vuosi x ja y, prosessi z ja w), vaan ovat osa pidempää ja laajempaa keskustelua aiheesta ja väliin esitettiin muutamia tarkentavia kysymyksiä.

Joka tapauksessa yhteenvetona:

– Zen 2 oli alunperin tarkoitus tuoda vain palvelimiin (koska kellotaajuuden odotettiin laskevan)

– Alunperin tarkoitus oli vain prosessipäivitys

– Mukaan päätettiin toteuttaa IPC-parannuksia

– Kellotaajuus Zen 2:lla skaalautui odotettua paremmin, päätettiin tuoda myös työpöydälle

Tuohon voi sitten yrittää sijoittaa vuosilukuja ja valmistajia haluamansa mukaan, mutta näin siis Zenin pääarkkitehtuurin kertomana.

Lähde AMD:n ja GloFon toimitussopimus sakkopykälineen, ja se, että GloFo ei ollut vielä lähelläkään pyyheen kehään heittämistä. Joku b-suunnitelma on voinut olla, mikä toki on fiksua tällä alalla.

AMD:n sopimus vaati ostamaan tietyn määrän piitä GloFolta, ei rajoittanut käyttämään vain GloFoa. AMD myös oli kertonut kauan ennen GloFon pyyhkeen heittämisiä että 7nm:ää tulee TSMC:ltäkin (ja että ensimmäiset tulee TSMC:ltä)

Joo toki, mutta ei sieltä nyt mitään 7nm piirisarjoja oltu koko rahalla ostamassa. TSMC:tähän AMD on käyttänyt näytönohjaimiin aina, joten tässäkään ei sinänsä mitään uutta. Näytönohjainhan tuli muutenkin ensimmäisenä juuri tuon mukaisesti.

Tää nyt ei kyllä taida pitää ollenkaan paikkaansa. Vegat ja polarikset tehty GloFo:lla.

Ja osa heitti kellotkin vielä 100mhz tarkkuudella oikein.

En tarkoittanut, että kaikki piirit, mutta TSMC:tä on käytetty jo siitä lähtien kun AMD osti ATI:n vaikka AMD:llä oli omatkin tehtaat vielä.

Veikkaan, että tuossa IPC-jutussa on kyse siitä, että todettiin, että ne parannukset saadaan toteutettua melko pienellä vaivalla.

Juuh, juurikin näin.

AMD:llä on ollut tälle vuodelle luvassa jo vaikka kuinka pitkään Vega 20, Navi 10, Ps4 (pro) chippejä, xbox one (X) piirejä, piirisarjoja, zen chiplettejä ja niiden erilaisia IO-die:ä, kaikenlaista polarista, vanhoja ryzeneitä ja epycejä, ryzen apu:ja jne.

Sillä ei olisi ollut mitään ongelmaa täyttää WSA:ta, vaikka se noista nyt jonkun tai parikin piiriä olisi TSMC:lle siirtänyt, vaikka glofon 7nm olisikin valmistunut samalla.

Yhteenveto on tuollaisenaan täyttä roskaa ja sopisi paremmin vaikka tämän foorumin kaatopaikalle.

Käsitellään kaksi ensimmäistä kohtaa yhteenvedosta:

– Zen 2 oli alunperin tarkoitus tuoda vain palvelimiin (koska kellotaajuuden odotettiin laskevan)

Tilanne 2015:

Zen valmistetaan GlobalFoundriesin eikun Samsungin 14LPP prosessilla, tarkoitettu lääppimisvehkeisiin, kellotaajuustavoite noin 3 GHz tai vähän päälle.

Zen2 tullaan valmistamaan GlobalFoundriesin 7nm HP prosessilla, jonka kellotaajuustavoite on luokkaa 5 GHz. Perustelut 5 GHz:lle: IBM myi tuotannnon GF:lle ja aikoi valmistaa GF:lla tulevia PowerPC prosessoreita 5 GHz kelloilla tai niillä main. GF:n pomon sanomiset joiden perusteella prosessi on "5 GHz". Noin 5 GHz:n yltävälle prosessille ainoa kilpailija Intel joka ei paljoa tarjoa prosessiaan muille.

"Odotamme 3,jotain GHz kellotaajuuteen tähtäävän prosessin kellottuvan korkeammalle kuin 5 GHz kellotaajuuteen tähtäävän prosessin." Huutonaurua :srofl:

Ja sitten seuraava:

– Alunperin tarkoitus oli vain prosessipäivitys

Vai niin. Huomioiden edellisen, tässä tapauksessa AMD suunnitteli oikeasti pärjäävänsä Inteliä vastaan "40% parempi kuin Excavator" eli noin Ivy Bridge tasoisella arkkitehtuurilla, Inteliä huonommalla valmistusprosessilla kun Intelillä on arkkitehtuurina vähintään Skylaken seuraaja. Ei hyvää päivää :facepalm:

Eli keskustelut taisivat mennä tasolle jossa kukaan ei tajua mistä prosessista milloinkin puhuttiin ja Clarkin sanomisia tulkittiin miten sattuu.

Palataan vuoteen 2015 niin saadaan yhteenvetoon jotain järkeä. Aikataulu mallia 2015, vuosiluvut noin:

2017: Zen tulee ulos, 14LPP

2018: Zen2 tulee ulos, GF 7nm, ei arkkitehtuurimuutoksia

2019: Zen3 tulee ulos, GF7nm+, arkkitehtuuriparannukset

Tämä ei toteutunut vaan kävi näin:

2017: Zen tulee ulos, 14LPP

2018: Zen+ tulee ulos, GF 12nm, ei arkkitehtuurimuutoksia

2019: Zen2 tulee ulos, TSMC 7nm, arkkitehtuuriparannukset

Ja nyt korjataan yhteenvetoon jotain järjellistä:

– Zen2:n chiplet versio oli alunperin tarkoitus tuoda vain palvelimiin (koska TSMC:n prosessi kellottuu huonommin kuin TSMC:n prosessi)

– 2018 julkaistun Zenin oli tarkoitus olla vain prosessipäivitys ja se olikin

– 2019 julkaistuun Zeniin päätettiin toteuttaa IPC-parannuksia (piti olla Zen3, oli Zen2 koska Zen+ korvasi Zen2:n)

Viimeisessä lausessa ei taas olekaan järkeä.

Skaalautui odotettua paremmin mihin nähden? Jo TSMC:n 10nm prosessin piti kellottua paremmin kuin 14LPP:n tai 12nm:n ja TSMC:n 7nm:n paremmin kuin TSMC 10:nm:n. Myös GF:n 7nm HP:n piti kellottua paremmin. Kaikkien mahdollisten käytössä olevien prosessien (GF ja TSMC) piti kellottua paremmin kuin 14LPP:n tai 12nm:n joten tuohon ei järkeä mitenkään saa.

AMD olisi joutunut maksamaan sakkoja jos käytti muuta kuin GloFoa. Eli kyllä se rajoitti koska AMD:lla oli rahapulaa. AMD käytti TSMC:ta 7nm valmistuksessa koska 1. GF:lla ei vielä ollut tarjolla 7nm tekniikkaa 2. GF sanoi suoraan ettei heitä haittaa (WSA:sta huolimatta tai sen takia) koska heillä ei riitä kapasiteetti kaikkeen mitä AMD tarvitsee.

Ai jaa. Eli SIMD datapolun ja laskentayksiköiden leveyden tuplaaminen, L1 välimuistin pienennys puoleen (ja samalla micro op cachen koon tuplaus) sekä yhden AGU:n lisääminen + kaikki muut parannukset ovat "pikkujuttu" :facepalm:

Koska Zenin AVX yksikkö oli lähes täysin sama kuin Excavatorissa oli, se todennäköisesti suunniteltiin kokonaan uusiksi. "Pikkujuttu" 😀 Herää tietenkin kysymys miksi tällaista pikkujuttua ei tehty jo Zeniin.

Kyllä minuun kannattaa luottaa enemmän kuin Mike Clarkiin. Jos oikeasti kertoi tuollaista soopaa. Jota kyllä epäilen todella paljon.

2015 tuollaiset asiat olivat vielä suunnittelupöydällä.

Jos kyse olisi Intelin prosessorista, nuo muutokset olisivat mielestäsi pieniä viilauksia, mutta koska kyse on AMD:n prosessorista, niin muutokset ovat tietysti suuria ja mahtavia.

Milloin Intel viimeksi on tehnyt vastaavan tason muutoksia arkkitehtuuriin?

Aika kovasti heittelet taas jutta pöytään ilmaan ainuttakaan lähdettä. AMD Roadmap kelmejä ja lehdistötiedotteita ei ole vaikea löytää ja mitään muuta virallista materiaaliahan ei ole olemassakaan siitä mitä tulee aikatauluihin ja suunniteltuihin prosesseihin.

Mihin haluat lähteitä? Lähes joka väitteeseen löytyy lähde helposti ja lähes jokaiseen olen antanut lähteen useampaan kertaan tällä foorumilla.

Mitenkäs se ilmenee tuosta postauksesta että lähes jokaiselle väitteelle on olemassa lähde?

Lähteitä lisätty. Lisää?

[OFFTOPIC]

Suuresti en yllättynyt että vedit taas kerran mutkat suoriksi ja pasteilit taas kerran prosessien markkinointimateriaalit joilla on hyvin vähän tekemistä tosielämän piirisuunnittelun kanssa siltä osin että kuinka paljon itse prosessi vaikuttaa piirien suorituskykyyn. Vähän enemmän papereita lukemalla voi löytää tiedon siitä että millaisilla esimerkkirakenteilla tuollaiset lupaukset kuten "2X logic density than its 16nm predecessor, along with ~15% faster speed and ~35% less power consumption" on saatu aikaan. Tuo kun ei todellakaan missään todellisuudessa tarkoita sitä mikä tahansa tuon prosessin läpi syljetty tuote suorituisi noin mutta tästä on turha jänkätä tämän enempää.

[/OFFTOPIC]

Erittäin hyvin "ymmärretty". On prosessi A joka kellottuu paremmin kuin prosessi B. Prosessi A:sta tehdään versio joka kellottuu paremmin, olkoon se prosessi C. Kysymys: Kellottuuko prosessi C huonommin kuin prosessi B?

Joten pointtisi meni "vähän" ohi.

No mulla on muistissa, että vähättelit jossain viestiketjussa Sandy Bridgeä tai Nehalemia saman tason muutoksista, mutta en tietenkään jaksa kaivaa tuhansista kirjoittamistasi viesteistä juuri näitä viestejä.

Väärin.

On prosessi A joka kellottuu jollain esimerkkirakenteella paremmin kuin prosessi B. Prosessi A:sta tehdään versio joka kellottuu jollain esimerkkirakenteella paremmin, olkoon se prosessi C. Kysymys: Kellottuuko prosessi C jollain esimerkkirakenteella huonommin kuin prosessi jollain esimerkkirakenteella B?

Ja vastaus on näihin on kyllä. Kyllä kellottuu.

Mutta onko AMD ZEN/ZEN+/ZEN2 ydin sellainen esimerkkirakenne? Voin vakuuttaa että ei ole 😀 Tässä(kin) touhussa markkinamiehet ei valitse sitä kehnointa tapausta kun tuotettaan markkinoivat.

Tässä nyt oikeasti nahistelee keskenään prosessin myyjien lupaukset jollain tuntemattomahkolla esimerkkirakenteella ja tuote jonka loppukäyttäjä voi ostaa kaupasta.

Vähättelin Sandy Bridgeä "täysin uusi arkkitehtuuri" ilmaisusta koska se on hyvin pitkälti vastaava kuin Nehalem. Sama ja vastaava ovat eri asioita. Eli voidaanko edeltäjää pitkälti vastaavan arkkitehtuurin sanoa olevan "täysin uusi arkkitehtuuri" kun toisella puolella on esim. Pentium 3-Pentium 4, K10-Bulldozer, Bulldozer-Zen jne joita ei mitenkään voi sanoa vastaaviksi. "No tää on täysin uusi arkkitehtuuri, me katos suunniteltiin prosessori alusta alkaen uusiksi. Tää uus arkkitehtuuri on kyl paljolti vastaava kuin toi vanha mut on tää kuitenki täysin uus."

Tuosta oli kyse.

Tässä oli kyse veikkauksesta. Prosessi C:n luvataan kellottuvan 15% paremmin kuin prosessi A:n joka kellottuu paremmin kuin prosessi B. Lähtisitkö veikkaamaan sen puolesta että jokin esimerkirakenne kellottuu prosessi B:lla paremmin kuin prosessi C:lla?

Minä en ainakaan lähtisi ilman kunnollista kerrointa.

Vähemmän yllättäen prosessi C:sta kehitetty prosessi D kellottui paremmin kuin prosessi B. Yllätti ilmeisesti jopa Mike Clarkin :rolleyes:

Tosin ennenkuin on saatu tarpeeksi lopulliset teknologiakirjastot, ajettu synteesit ja sitten vielä ehkä tehty ensimmäiset sämppelit aikalailla saman tasoisen markkinointitiedon varassa se AMD on myös joutunut arvailemaan kuinka nopeasti ne tulevaisuuden prosessit kulkevat. Vähän epäilen, että ainakaan 2015 on päästy vielä kovinkaan pitkälle tuossa hommassa, late 2016 ehkä.

Juurikin, sitähän ei kukaan varsinaisesti tiedä koska se AMD tai kukaan muukana prosessin ekat samplet on saaneet ja miten AMD itse on prosessiaan testaillut.

On myös mielestäni aivan hyvin mahdollista että kaikessa hiljaisuudessa on suunniteltu ja protoiltu yhtä aikaa aikaisessa vaiheessa useampi variantti ZENistä, ml nämä IPC parannukset. Ei niitä mitenkään voi runnoa läpi sillä tavalla että 2018 huomataan että 2019 voisi olla tarvetta IPC parannukselle kaiken muun lisäksi.

Ei voikaan, siksi se perustelu, että ne parannukset tehtiin vain koska prosessi olikin odotettua parempi kuulostaa aika omituiselta ja jälkikäteen keksityltä. Kuulostaa vähän sellaiselta väritellyltä totuudelta missä perusasiat ovat oikein, mutta sekaan on lisätty vähän markkinointitarinaa ja jutunkerrontaa.

Noiden kalvojen perusteella AMD on halunnut nostaa tuon kellotaajuuden noston markkinointikohteeksi. Epäileväinen minä, saattaisi jopa miettiä tehdäänkö siitä numeroa, koska itseasiassa se kellotaajuus nousi selvästi vähemmän, mitä TSMC lupaili.

Ehkä se realistisin tämän sisältävä muotoilu voisi olla että kerta prosessi osoittautui odotettua paremmaksi niin otettiin käyttöön vaativampi? versio piiristä ja päätettiin samalla laajentaa tarjontaa? 🙂

Lue editoimani jälkimmäinen kappale 🙂

2015 joku TSMC 7nm prosessi oli niin alkuvaiheissaan jos edes siinä, ettei TSMC:n lupauksia kummempaa ollut saatavilla. Sitten taas, 14LPP oli niin umpisurkea prosessi kellottumaan että sen alittaminen on jopa vaikeaa.

Yksi variantti vahvistettiin GlobalFoundriesin puolelta, "AMD CPU".

IPC parannukset tehtiin hyvin todennäköisesti vuonna 2015. Zenin arkkitehtuuri valmistui 2015 alkuvuodesta ja Jim Keller lähti syyskuussa 2015. AMD:n olisi ollut tyhmää olla käyttämättä Kelleria Zen2 arkkitehtuurin suunnitteluun ja toisaalta Kellerhän on tunnettu henkilönä joka haluaa vain suunnitella arkkitehtuureita. Ja lähtee sen jälkeen seuraavan haasteen pariin jättäen muut viimeistelemään.

Ryzeneistä puhuttaessa prosessi oli odotettua huonompi. Tosin koska Ryzen=Epyc chiplettien osalta, ei asialla ole merkitystä.

Eikä AMD:lla ole varaa pitää arkkitehtuuria varastossa pitkään. Täysin järkeenkäypää että Zen2 arkkitehtuuri tähdättiin kahden vuoden päähän Zenistä resurssipulan takia. AMD on antanut ymmärtää Zen3:n olevan lähinnä die shrink. Zen4 joka tulee kahden vuoden päästä Zen2:sta ….

Tää kyllä suuresti kiinnostaa, mikä oli AMD:n odotus kellotaajuudeksi? Minä en ole nähnyt tietääkseni ainuttakaan kellotaajuuslukemaa kelmeiltä. Performance ja Power ja Density on pyörinyt vain hienoilla kertoimilla eikä kukaan ole määrittänyt niitä. Kyl dualcoressakin on single coreen verrattuna performanssia ja densityä vaikkei prosessille tekisi mitään. Kunhan vain jättää tarpeeksi yksityiskohtia kertomatta. Ja sillon kun niitä pyöriteltiin niin eipä ollut IPC parannuksetkaan tiedossa.

GF:n prosessin piti olla paremmin kellottuva kuin TSMC:n, syistä jotka ylempänä. Koska AMD:n piti WSA:n takia tehdä jotakin GF:lla paljon ja GF kertoi ensimmäisen tape outin olevan "AMD CPU", kyseinen "CPU" oli siten suurella todennäköisyydellä Ryzen. Joten Ryzenin odotettiin kellottuvan paremmin kuin TSMC chiplet Ryzen kellottuu.

Muutenkin sen 12-core Ryzenin all core turbo on sama kuin "5 GHz" i9-9900K:ssa eli kyllä AMD olisi helposti saanut sen 5 GHz single core turboksi jos olisi halunnut.

Teollisuudessa toimineena en usko hetkeäkään että GF:n 7nm prosessin hylkääminen tuli kulissien takia GF:lle yllätyksenä. Tai että kyse olisi mistään "drastic, strategic turn" tyylisestä suunnanmuutoksesta kuten itse sanoivat. Kunhan vain rahoittajia ja osakkaita miellyttävät.

Arvaisin että siellä törmättiin sen luokan aikataulu/budjetti/tekniset ongelmat tiiliseinään että amd:n oli pakko kääntyä TSMC:n puoleen. En yllättyisi jos virallisen lehdistötiedotteen ja todellisien syiden toteamisen välissä olisi yli vuosikin.

GFn 14LPP ei ollut todellakaan mikään "umpisurkea prosessi". Se oli todella paljon parempi kuin aiempi "28nm" tai kenenkään "20nm" prosessit. Ja vaikkei se päässyt samoihin kelloihin kuin esim, Intelin "14nm" prosessi, se pääsi matalilla kelloilla pienempään virrankulutukseen.

Kaikkein "20nm" prosessit oli ne umpisurkeat prosessit. GFllä se oli niin surkea, että kukaan (potentiaalisesti AMD) ei halunnut käyttää sitä jonka takia se peruttiin. Ja sen surkeuden takia AMD joutui esim. perumaan pari piiriä, ja tuomaan niiden sijasta markkinoille viilattuja versioita vanhoista "28nm" tekniikalla tehdyistä piireistä.

Keksit nyt päästäsi perusteettomia väitteitä tuon "14nm" valmistusprosessin laadusta, jotta voit syyttää että AMDn tuotteiden puutteet ei ole AMDn arkkitehtuurin vaan yhteistyökumppaneiden puutteita.

Tosin työnjako Zenin kanssa taisi olla se, että Mike Clark oli pääarkkitehti ja Jim Keller projektinjohtaja.

Tästä ei ole mitään faktatatietoja. Ei ole mitään varmaa tietoa, mitkä piirit piti valmistaa kummankin valmistajan tehtaissa, eikä sitä, tappoikin GFn prossessin suorituskyky, toimivuus ylipäätään vai yksinkertaisesti keskeneräisyys/aikataulujen pettäminen, ja jos se oli suorituskyky, niin mikä osa-alue siinä.

Spekuloit vaan ja väität omaa spekulaatiotasi faktaksi.

AMD on puhunut erittäin vähän siitä, mitä zen3 tulee olemaan.

Ihmiset ovat vaan spekuloineet, että koska se on tulossa heti 2020, siihen ei varmaan tule suuria arkkitehtuurillisia muutoksia. Se, mitä AMD sanoo ja antaa ymmärtää, ja mitä täysin AMDn ulkopuoliset ihmiset spekuloivat on kaksi täysin eri asiaa.

Tai ihan vaan kaupallinen kannattavuus.

Noin kaksi viikkoa sitten, mikäli muutoksen ajanhetkeksi lasketaan uuden tuotteen julkistaminen.

Voisitteko mennä jauhamaan tuota teidän intel vs amd tuonne

Virallinen: AMD vs Intel keskustelu- ja väittelyketju

Eikun tehdän jo jauhatte sitä siellä, voisitteko lopettaa tai edes vähentää sen muualla?

Millä perusteella? Ei se niin toimi, että niitä hertsejä niin vaan saadaan lisää pudottamalla käytössä olevaa ydinmäärää.

Voi hyvinkin olla, että tällä nimenomaisella ”7 nm” prosessilla* tuo yhden ytimen ja kaikkien ytimien maksimikellotaajuus on yksi ja sama luku. AMD sitten vaan yrittää kääntää markkinoinnissaan tämän vahvuudeksi…

* Tälle nimenomaiselle prosessoriarkkitehtuurille.

Joo eiköhän tämä trollaus taas tältä erää riitä.

Nimenomaan. Uutisessa tiedotetaan uudesta prosessorista, joka tulee myyntiin kuluvan vuoden syyskuussa.. .. Mitä helvetin väliä on sillä, mitä on spekuloitu vuonna 1990-2018?

Minulle suurimmat kysymysmerkit ovat:

1) Virrankulutus kunnon rasituksessa kaikilla ytimillä -> siellä on sisällä melkein 2x 8-ydin, joten jotain throttlausta siellä tapahtuu, jos TDP on sama kuin 8-ydinmallissa.

2) Muistien latenssit, jos eivät ole samalla chipletillä. Paljon sitä NUMA-latenssia tulee.. (ja vaikuttaako se mihinkään?)

3).. ja onko tässä joku Game Mode, jossa pistetään toinen chiplet pois päältä? (ettei tule noita muistiongelmia)

Ihan hatusta spekuloin, että puhtaaseen pelikäyttöön yhden chipletin ratkaisu on parempi.

Vastatekseni ainakin toiseen kysymykseen, niin AMD:n Robert Hallock sanoo, että muistiin viittamisen tapauksessa 2 chiplettiä käyttäytyy kuin yksi monoliittinen siru. Sama viive jokaiselta ytimeltä jokaiseen kohteeseen muistissa.

https://twitter.com/Thracks/status/1139602916245954560

Muistiohjain sijaitsee I/O-piirillä eikä chipleteissä. Siten kaikki muisti on yhtä nopeasti saatavilla jokaiselle ytimelle. NUMA/UMA menee myös roskiin koska muistiohjaimia on vain yksi. Samalla game mode on myös tarpeeton. Toisen chipletin varmasti saa pois käytöstä mutta erityistä etua siitä tuskin on, varsinkin jos tämä windows schedulerin päivitys toimii hyvin. Ehkä jopa haittaakin kun maksimiboostiin yltäviä ytimiä on vähemmän.

Tietääkö Sampsa mitä trollaus on?

Laitoitteko threadripperin oikeasti banniin tästä? Ei Jeesus..