Intelin uusi toimitusjohtaja Pat Gelsinger on pitänyt juuri Intel Unleashed: Engineering the Future -tapahtumassa keynote-esityksen. Livestream-lähetys on jo päättynyt, mutta nauhoituksen pitäisi tulla katsottavaksi yhtiön verkkosivuille lähitunteina.

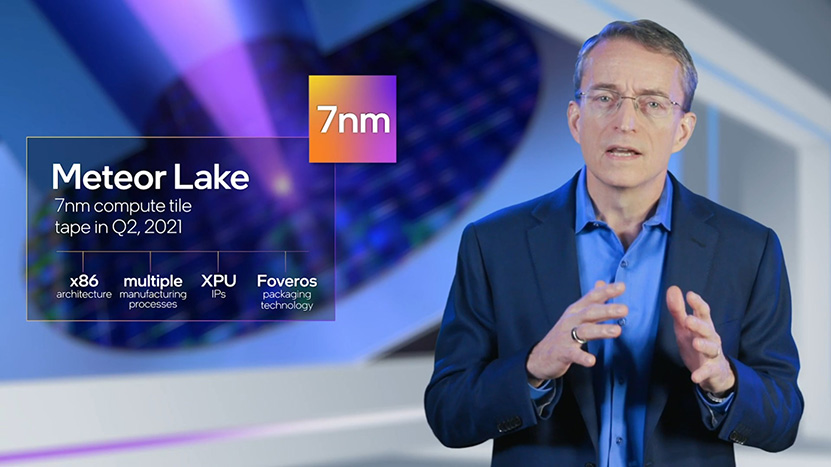

Gelsingerin mukaan Intelin 7 nanometrin EUV-prosessin kehitystyö edistyy hyvällä vauhdilla ja yhtiö on saamassa tulevan Meteor Lake -arkkitehtuurin laskentasirun tape out -vaiheeseen tulevalle prosessille vielä toisen vuosineljänneksen aikana. Meteor Lake -arkkitehtuuriin perustuvat yhtiön ensimmäiset 7 nanometrin prosessorit tullaan julkaisemaan vuonna 2023.

Meteor Lake tulee siirtymään monoliittisesta piiristä useampaan pieneen piiriin, mutta kiitos yhtiön Foveros-paketointiteknologian ne saadaan integroitua lähes yhdeksi piiriksi. Vaikka kyseessä on yhtiön ensimmäinen 7 nanometrin prosessori, todellisuudessa osa sen piireistä tullaan valmistamaan vanhemmilla valmistusprosesseilla. Intel on antanut prosessorille uuden XPU-lyhenteen, koska se tulee rakentumaan useammista erilaisista piireistä, joista helppoja oletuksia ovat erilliset prosessoriydin- ja grafiikkapiirit, sekä jonkinlainen I/O-liikenteeseen keskittyvä siru tai useampi. Intelin mainitsema laskentasiru (Compute Tile) on oletettavasti nimenomaan prosessoriytimiä sisältävä siru.

Lähde: Intel

Tuo vitsi alkaa käydä vanhaksi, puhumattakaan siitä että Intel on tehnyt useammasta sirusta rakentuvia prosessoreita jo 90-luvun puolivälissä ellei aiemminkin.

Joten uskotaan vasta kunhan tulee jotain näkyvää – eikä hyvältä näytä vieläkään

Kuluttajapuoli ei vaan enää ilmiselvästi kiinnosta koska huonot katteet.

Sama koskee ikuisia mainoksiaan/lupauksiaan edes etäisesti käyttökelpoisista näytönohjaimista, kilpailua näytönohjain-puolellekin todella tarvittaisiin.

Intelin 7nm vastaa tsmc:n 5 nm prosessia. Ja nämä nanometrit ovat pelkästään markkinointi nimiä.

Tuohon mennessä tsmc taitaa jo pukata täyttä häkää niitä oikeita 5nm siruja tosin, jos kaikki etenee suunnitelmien mukaan.

Samsungilta tulee silloin 3 nm prosessia.

Kellään ei ole tuohon mennessä mitään "oikeita 5nm" siruja, kaikkien todelliset mitat menee tuolloinkin jossain 10nm yläpuolella.

2023 TSMCllä lienee markkinoilla "3nm" prosessi joka tiheydeltään tulee olemaan hiukan (muttei todennäköisesti kovin paljoa) tiheämpi kuin Intelin "7nm" prosessi. Tiheys ei kuitenkaan suoraan korreloi suorituskyvyn kanssa.

ei vaan "3nm" prosessia joka on hyvin samaa luokkaa tuon Intelin "7nm" prosessin kanssa. Samsung on viime aikoina ottanut kärkipaikan siinä, kuinka törkeästi näitä valmistusprosessien kokoja niiden markkinointinimissä valhedellaan; Samsungin on "5nm" on joiltain oleellisilta mitoiltaan täysin sama kuin Samsungin "7nm" prosessi, joka oli samaa luokkaa Intelin "10nm" ja TSMCn "7nm+" prosessien kanssa.

Spekuloin vajaa pari vuotta sitten toisessa ketjussa täällä, että Foveros voisi taipua johonkin chiplettiratkaisun tapaiseen juttuun:

Hauskaa saada vastaus pitkän ajan jälkeen ja tarkempi vastaus sitten aikanaan.

Silti. Minun mielestä vasta tämä vaikuttaisi olevan Intelin varsinainen reagointi/vastaus Zenille (mikä sinänsä on ihan ok, hyvistä ideoista pitääkin inspiroitua). Joka tapauksessa ansaitsevat mielestäni tuosta taannoisesta kilpailijan vähättelystä pientä näpäyttelyä edelleen ja tämän tuotteen kohdalla jos koskaan.

Nyt kun TSMC on tukossa, niin Intelillä voi olla mahdollisuuksia selviytyä, koska eivät ole TSMCn kapasiteetista riippuvaisia.

3nm viivanleveyden kohdalla tulee varman pidempi jakso missä pysytään samalla tekniikalla tietysti tulee parannuksia siihen.

Tekniikkasivujen pitäisi alkaa käyttämään jotain tällaista estimaattia artikkeleissaan, jotta todelliset erot näkyisi lukijoille:

katso liitettä 572169

katso liitettä 572170

5 nm lithography process – WikiChip

en.wikichip.org

MTr/mm² – WikiChip

en.wikichip.org