TSMC isännöi alkukuusta nimeään kantavaa TSMC Technology Symposium -tapahtumaa, jossa esiteltiin muun muassa eilen uutisoitu ensimmäinen toimiva DDR5-muisti. TSMC esitteli tapahtumassa luonnollisesti myös omia uusia teknologioitaan ja tulevaisuuden suunnitelmiaan.

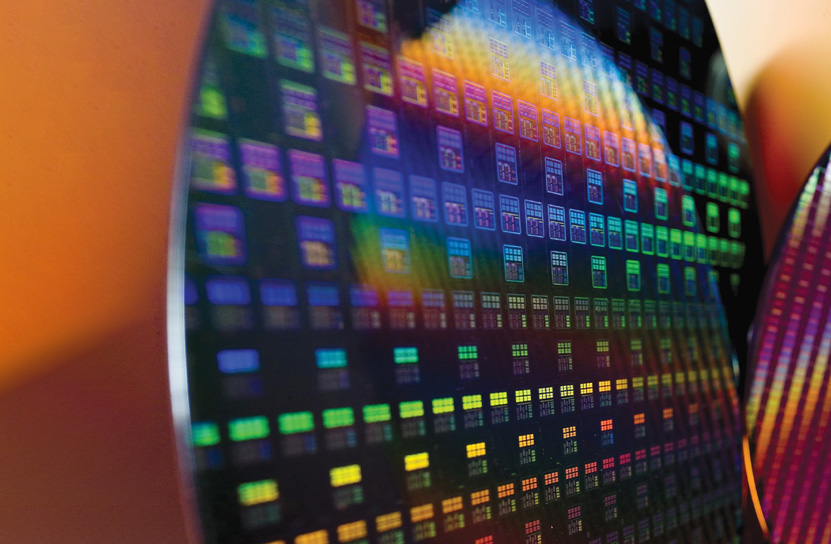

WoW- eli Wafer on Wafer -paketointiteknologia on TSMC:n uusi 3D-piirien valmistustekniikka, jossa kaksi piikiekkoa yhdistetään toisiinsa jo valmistusvaiheessa. Lopullisessa paketoinnissa alempana olevaan piisiruun tehdään TSV- eli Through-Silicon Via -läpiviennit, jotka mahdollistavat ylemmäksi jääneen sirun kommunikaation paketoinnin kanssa. WoW:n keskeisimmät ongelmat itse valmistusteknisten haasteiden lisäksi on se fakta, että valmistustekniikan myötä piikiekkopinoista tulee väkisin piirejä, joista vain toinen siruista on toimintakykyinen. Lisäksi kummankin kerroksen piirien on oltava saman kokoisia, tai pienempään piiriin on jätettävä tyhjää hukkatilaksi.

WoW-teknologian kerrotaan olevan yhteensopiva yhtiön muiden 3D-paketointiteknologioiden kanssa, jolloin sillä voitaisiin valmistuttaa esimerkiksi CoWoS-tekniikalla (Chip on Wafer on Substrate) MCM-piirejä, joissa on kaksi kaksikerroksista piisirua yhteisen interposerin päällä.

Cadence ja TSMC ilmoittivat lisäksi tapahtumassa tekevänsä yhteistyötä 7nm+- ja 5nm-valmistusprosessien korkean suorituskyvyn piireille tarkoitettujen HPC-versioiden parissa. TSMC:n mukaan yhtiö uskoo kykenevänsä aloittamaan 5 nanometrin valmistusprosessin riskituotannon vuoden 2019 ensimmäisellä neljänneksellä.

Lähde: Cadence Breakfast Bytes

Uuh 5nm, millonhan alkaa rajat oikeasti tulemaan vastaan, sillä kun pelotellaan kokoajan, mutta silti edistystä vain kokoajan tapahtuu. Toivotaan, että ei paljon vastoinkäymisiä tule ja kunnon massatuotantoon päästään nopeasti. Sitten voiskin taas olla ajankohtaista päivitellä SERriä.

5nm:ää pidettiin jossain välissä rajana mutta muistelisin nähneeni juttua 3nm:stä ja ehkä jopa 2nm:stä jossain

Tuntuu vaan siltä, että raja siirtyy aina kun ihme ja kumma paukuttavatkin sen hetken 'mahdottomuuden' ylitse. Noh, pelätään pahinta, mutta toivotaan parasta!

Rajahan siirtyy kivasti kun uudelleen nimetään 22nm -> 16nm, 14nm -> 12nm .. ja mitä näitä nyt on tehty. Tarpeeksi kun kikkailaan niin tulee uusi prosessi negatiivisilla markkinointi nanometreillä 😉

Tekniikka ei ole ongelma,vaan että tranistorit tarvitsee useamman atomin, joten niistä pitää tehdä surempia kuin käytettävä tekniikka.

Sekin vielä toki tuohon Kaotikan kommenttiin lisäykseksi, että köytetyistä markkinointinanometreistä huolimatta ei olla vielä kauhean lähellä oikeaa 5nm rajapyykkiäkään.

Tosiaan, tuo on syytä myös pitää mielessä että "5nm:n raja" saattoi tarkoittaa ihan oikeasti 5nm:ää eikä markkinointi nm:iä.

Sitten siirrytään pikometreihin ihan niin kuin aikoinaan siirryttiin mikrometreistä nanometreihin

Tai sitten tilalle tulee optiikka ja kvantit

Itsestä on kumma kun täällä ei tajuta valmistusprosessin ja tuotteen eroa.

Komponentit tehdään sen kokoiseksi kun ne toiminnan takia on pakko tehdä.

Tottakai valmistustekniikan täytyy kulkea edella trasistori kehityksestä.

Ei tulisi mitään että tehtäisiin piiri pienimmällä tekniikalla ja siteen alettaisin miettiä miten se tehdään.

Katsellaan aikaisintaan vuosikymmenten päästä.

Ongelma näissä scifi teknologioissa on, että vaikka sellainen saataisiin aikaiseksi kaikki tutkimus, ohjelmistot, algoritmit ja rakenteet ovat 50v jatkuvan piipohjaisten piirien kehityksen tulos. Mikäli aloitetaan uudella teknologialla pahimmillaan tuo kaikki pitää kehittää uusiksi. Se ei ole mikään vuoden, jos edes vuosikymmenen homma, ja se pitäisi myös rahoittaa jotenkin.

Nyt en kyllä ymmärrä mistä sait kuvan että täällä ei tajuttaisi valmistusprosessin ja tuotteen eroa :confused:

Aivan, meinasikin jo unohtua nuo valmistajien 'kirjavat' nimeämis käytännöt:lol:

Ei se kehitys välttämättä tarvitse kuin sen yhden tärkeän keksinnön oikeaan paikkaan ja se on siinä. Sen jälkeen homma alkaa rullaamaan suht nopeaan tahtiin. Muista, että käytät joka päivä teknologiaa jota olisi väitetty mahdottomaksi vielä 50 vuotta sitten.

Transistori keksittiin vuonna 1947. Mikropiirien valmistus alkoi ~10 vuotta myöhemmin. ~60v myöhemmin meillä on nykyisenlaiset tietokoneet.

Kyllä, se alkaa rullaamaan, ja kestää ei vuosia, vaan vuosikymmeniä saavuttaa kypsä tila.

Ei optista piiriä tulla tekemään niin, että otetaan nykyaikainen mikroprosessori ja jotenkin vain korvataan sen transistorit optisella transistorilla. Kun se optinen piiri tulee se tarvii uudet tehtaat, uudet suunnittelumenetelmät, uudet suunnitteluohjelmistot ja lopuksi vielä uudet softat, kun se joskus tulee ulos tehtaasta.

Tyhmä kysymys. Mitä tarkoittaa riskituotanto?

Riskituotanto puolijohdemaailmassa on käytännössä sitä kun uusi tuotantoprosessi ei ole vielä valmis kunnon massatuotantoa varten (yhdestä piikiekosta saatujen toimivien piirien määrä on vielä vähän huono). Riskituotanto on yleensä siis kallista ostajille, koska tomivia piirejä tuotetaan paljon vähemmän, mutta silti tärkeää potentiaalisille massatuotannon ostajille voidakseen esim testata tuotteiden tehoa yms kyseisellä tuotantoprosessilla.

Ok, kiitos 🙂

Sitten kun nanometrit menee negatiivisiksi, syntyy varmasti musta aukko joka syö koko maapallon

Toisaalta, 60-luvun piireillä mentiin kuuhun, nykyisillä kattellaan nippanappa kissavideota netistä! :vihellys:

Niin noh eipä näillä Intelin ja AMD:n prosessoreilla mitkä nyt on hot kyllä kuuhun mennä. Muistaakseni nää kilkkeet alkaa ottaa liikaa häiriöö kosmisesta säteilystä tai jostakin että eivät yksinkertaisesti toimi. Sen takia noissa avaruus härveleissä on huomattavan vanhalla tekniikalla tehdyt prosessorin.

Näin muistelisin jostain lukeneeni. Jopa jossain olikos se nyt perun tai jonkun vuoristossa taitavat suosia jotain muita kamppeita kuin näitä mitä me käytämme.

Transistoritietokoneet on luotu aika pitkälti tyhjästä. Oli paperia ja reikäkortteja, mutta siinä se.

Jos tuollainen uusi laite saataisiin "kuluttajamalliseksi" niin se todennäköisesti olisi ensin joku laajennuskortti/lisälaite nykyisiin tietokoneisiin. Kyllä niitä tutkimuskäytössäkin olevia aparaatteja yleensä jonkun toisen laitten kautta operoidaan. Ei siis todellakaan tarvita kokonaan uutta käyttöympäristöä luotuna nollasta.

Tarvittiin siinä avuksi myös tehokasta vesihöyrygeneraattoria…

![[IMG]](https://images.duckduckgo.com/iu/?u=http%3A%2F%2Fbestanimations.com%2FSci-Fi%2FSpaceships%2FRockets%2FRocket-03-june.gif&f=1)

Jotta tuollainen laite tulisi yhtään mihinkään siten, että joku siitä maksaisi sen pitäisi olla nykytietokoneiden tehoinen tai siis mielummin selvästi tehokkaampi. Mihin tätä "lisäkorttia" olisi oikein tarkoitus käyttää? Muutaman optisen transistorin saaminen toimimaan ei riitä mihinkään järkevään kaupalliseen sovellukseen kun vieressä on se halpa miljardien transistorien pii-ic.

Siinäpä se juuri on. Transistoritietokoneiden piti kilpailla ainoastaan radioputkitietokonetta vastaan. Se oli aika helppo ohittaa.

En minä tiedä mihin noista on. Eiköhän kuitenkin jonkun sortin kiihdytin ole se mihin noita alkuun käytettäisiin. Eli joku tietty spesifi tehtävä jossa ne on hyviä. Tietysti ensin tutkijoille, sitten jollekin ammattilaisille ja vuosien jälkeen ehkä kuluttajille.

Toisaalta, jos optiset ratkaisut saadaan toteutettua yllätävän nopeasti ja edullisesti, niin edessä voisi olla myös Transmeta-tyyppinen veto, jossa tulkattaisiin x86-käskykantaa, eli päästäisiin mukaan nykyisille markkinoille luomaan kassavirtaa, mutta olisi myös mahdollisuus luoda kokonaan uusia markkinoita uusilla tehoilla.

Melkoisesti jossia ja ehkiä.

Koin wow-efektin

Eli ei edes pienintäkään käsitystä mitä oltaisiin tekemässä ja millä, mutta kohta joka kodissa ihan muutaman vuoden päästä. Juuh tota, oisko pieni reality check nyt mitään?

Lähempänä "muutamaa vuotta" kuin sinun 60 vuotta. Tuskin 10v päästäkään mitään ihmeitä vielä on.

TSMC:n pian eläköityvä puheenjohtaja Morris Chang taisi jokin aika sitten todeta, että valmistusprosessien pieneminen jatkuu ensi vuosikymmenen puoliväliin saakka, mutta kohtaa sen jälkeen suuria hankaluuksia. Tuolloin varmaan ollaan juuri 2 nm prosessissa.

Ei pikometreihin koskaan päästä. Vierekkäisten piiatomien väliset etäisyydet kiekossa ovat nanometrin kymmenyksiä.

Markkinointiosasto pääsee, vaikka fyysisesti se olisikin mahdollista 😉

En sanonut 60 vuotta sanoin vuosikymmeniä ei vuosia.

No ei nyt sentään. Huomaa että pikometreihin siirryttäsiin vasta nanometrin kymmenysten jälkeen. Hypoteettisen 1 nm prosessin jälkeen olisi siis 0,7 nm tjms. Aivan kuten 90 nm oli muistaakseni ensimmäinen nanometriprosessi, sitä edelsi joku 0,1x um. 90 pm olisi kuitenkin jo vähemmän kuin yhden piiatomin halkaisija. Tuskin puolijohdevalmistajat kehtaavat käyttää markkinointinimeä, joka indikoisi että joku mitta heidän prosessissaan olisi yhtä atomia pienempi.

Yleensä myös kellojenkin kanssa lienee ongelmia.

Ja alkupään engineering samplethan monesti ovat aika alhaisilla kelloilla.

Kyllä siinä myös hiilidioksidiakin tuli, kun eka vaihe käytti kerosiinia polttoaineena.

Jonka polttoaine pumputhan käyttivät vaivaisella 100MW teholla energiaa pystyäkseen syöttämään polttoainetta varsinaisille moottoreille…

Miksi ihmeessä? Mikrometreistäkin siirryttiin suoraan satoihin nanometreihin.

Minä muistan wanhoista mikrobiteistä maininnan 0,9 mikronia kun prossujen viivanleveyksistä puhuttiin :think:

Eikä siirrytty. Ks. esim. TSMC:n tarjoamat valmistusprosessit:

http://www.tsmc.com/english/dedicatedFoundry/technology/logic.htm

Mitä tarkoitat?

TMSC siirtyi 1,0µm (1.0 mikrometrin prosessi = 1000nm ) suoraan satoihin nanometreihin (0.8µm -> 800nm).

A series of continuing successful developments followed, including 1.2µm, 1.0µm, 0.8µm, 0.6µm, 0.5µm, 0.3 µm, and 0.25µm processes.

Eihän tuosta 1.0 mikrometristä olekaan muuta reittiä tiheämpään kuin satojen nanometrien prosesseihin siityminen, joten ei tuo nyt kovin kummoista lisätietoa kenellekään tuo.

800 nm lithography process – WikiChip

Näemmä noita käytetään ihan kumpiakin tapoja.

Mediassa ulkomuistista 110nm oli ensimmäinen josta puhuttiin lähes aina nanometreissä, 0,13µm oli vielä 130nm:stä yleinen nimi

AMD Palomino, 0,18 mikronin prossu, sellainen mulla oli ekassa omilla rahoilla hankitussa koneessa. Kyllä noihin aikoihin puhuttiin mikrometreistä tai yleisemmin varmaan mikroneista, tai siis tarkemmin niiden osista.

Siis kyse oli siitä, käytetäänkö valmistusprosessien markkinointinimissä joskus pikometrejä. Ei käytetä, sillä ensimmäinen jossa niin voitaisiin järkevästi tehdä, olisi joku 90 pm jota ei koskaan saavuteta.

Vaikka 2000-luvun vaihteessa oltaisiin puhuttu (en muista) noista 0,x um prosesseista xxx nm prosessien sijaan, nykyään noihin edelleenkin viitataan usein ihan nanometreinä. En keksi miksi se muuttuisi.