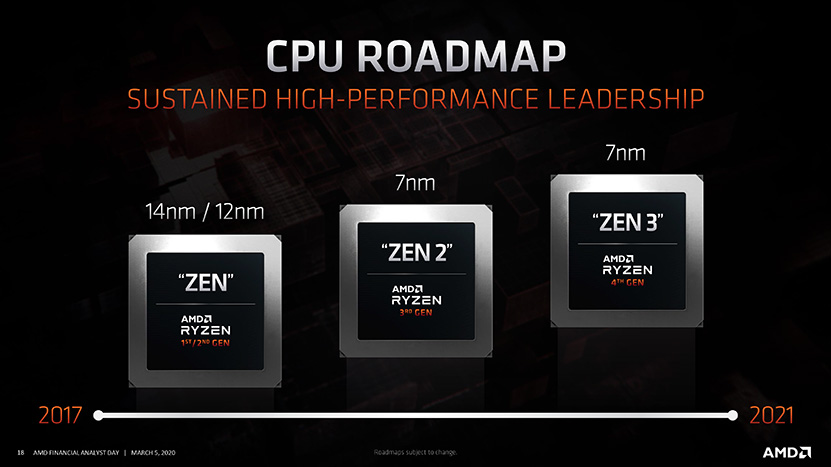

AMD:n odotetaan julkaisevan vielä kuluvan vuoden aikana uudet Zen 3 -arkkitehtuuriin perustuvat prosessorit. Ensimmäisenä linjalta ovat tulossa ulos Milan-koodinimelliset Epyc-palvelinprosessorit ja Vermeer-koodinimelliset Ryzen-prosessorit.

DRAM Calculator for Ryzen ja ClockTuner for Ryzen -sovelluksistaan tunnettu Yuri ”1usmus” Bubliy on nyt twiitannut uusia tietoja tulevista Ryzen-prosessoreista. 1usmusin mukaan yksi Zen 3:n uusista ominaisuuksista on nimeltään Curve Optimizer, mikä mahdollistaa prosessorin Boost-toiminnon konfiguroinnin käyttäjän toimesta. Lisäksi kaikki prosessoriytimet ovat nyt ylikellotettavissa toisistaan riippumatta.

AMD tulee 1usmusin mukaan myös laajentamaan tuotekirjoaan tuomalla markkinoille 10-ytimisen Vermeer-prosessorin, kun nykyisessä tarjonnassa 8-ytimisistä hypätään suoraan 12-ytimisiin. Kolmas paljastus koskee puolestaan Infinity Fabric -väylää, jolle ollaan tuomassa ilmeisesti lisää jakajia, mitkä tulevat puolestaan mahdollistamaan aiempaa hieman korkeammat muistikellotaajuudet.

1usmusin mukaan kaikki yllä mainittu tieto on luettavissa mistä tahansa AMD:n emolevyn BIOSista, mikä perustuu uuteen AGESA 1.0.8.1 -versioon.

Lähde: 1usmus @ Twitter

Se, että kaikillä ytimillä on oma kellonsa tarkoittaa käytännössä sitä, että siellä tarvitaan ylimääräisiä puskureita ytimien ja L3n välille kun pitää mennä kellotaajuusdomainista toiseen, ja L3 ei tule olemaan vain "vähän hitaampi koska se on suurempi ja jaettu useamman ytimen kesken" vaan selvästi hitaampi. Eli ytimiä ja L3-välimuistia yhdistävä väyläarkkitehtuuri on hyvin erilainen kuin zen/zen2ssa. Mutta eipä sellainen crossabar mikä zen/zen2ssa oli CCXn sisällä oikein skaalautuisikaan kahdeksalle ytimelle.

Oletettavasti nyt sitten zen3ssa on väylähierarkiassa samalla tasolla sekä kaikki 8 ydintä, L3-välimuisti, että portti ulos IO-piirille lähtevälle linkille. Ja näitä varmaan yhdistää joku rengasväylä tai mesh.

Mielenkiintoinen kysymys on, että onko L2n koko edelleen sama 512 kiB vai onko se tuplattu megaan kompensoimaan pidempää L3-viivettä?

Eikö esim. 8+2 onnistuisi?

Ei tuossa taida olla AMD:lle sellaista hyötyä. Eiköhänn nuo täydet CCX varata korkeempiin SKU:hin, eikä sit tähän käytetä. Varmaan yritetään vaan saada vielä parempi käyttöaste saanneista.

Tuolla samalla logiikalla myös 16 ytiminen olisi outo julkaisu. Jos lisäytimille on käyttöä, niin tässä huhutussa olisi 25% enemmän ytimiä kuin nykyisissä 8-ytimisissä. Aikamoiset viiveet saavat olla, jos suorituskyky ei kasva yli 20% kun softa rasittaa kaikkia ytimiä täysillä (varmasti kasva).

Lisäksi tämä mahdollistaa järkevämmät hypyt ydinmäärissä. Nykyään esim. 3800X on aika turha julkaisu omasta mielestäni, koska sen ja 3700X:n välinen ero suorituskyvyssä on n. 5% luokkaa. Jos vaikka seuraavan sukupolven 4700X on 8-ytiminen ja 4800X 10-ytiminen, niin 4800X:n hankinnalle voisi olla järkeviä perusteluja.

L3-kakkua olisi kokonaisuudessaan tuplasti (tosin eri piilastujen ytimet ei voisi jakaa sitä keskenään).

Ei, koska jokaiselta piilastulta pitänee olla yhtä monta ydintä aktivoituna.

Tuo ’yhtä monta ydintä’ -vaatimus voi aivan hyvin poistua Zen3:ssa.

Olisi teoriassa ehkä mahdollista hallita prosesseja/ytimiä siten, joku kriittinen prosessi (superpi tms.) saadaan pyörimään ensisijaisesti (jopa yksinomaisesti) siinä yksikössä, jossa on vain 2 ydintä käytössä ja 32MB L3:sta (vaikka vaatisi varmaan käyttöjärjestelmäänkin aika lailla muutoksia).

Saisi markkinoinnille hienoja IPC-parannuksia, ja voisi tuosta vanhemmilla ohjelmilla olla oikeaa hyötyäkin.

En kyllä usko, että tuollaiseen 2+8-konfiguraatioon mentäisiin, koska kyllä se käytännössä tarkoittaisi että käyttöjärjestelmätuki optimaalisen suorituskyvyn kannalta olisi täyttä helvettiä. Jos ei ole 5+5, niin sitten 6+4.

Maailmassa on korkeintaan ehkä yksi ihminen jolle superPI on jotenkn kriittinen prosessi, että aika huono esimerkki

Ja ei, optimaalinen käyttöjärjestelmätuki menisi niin hankalaksi (ja nimenomaan logiikka siitä, mitä skedulointilogiikkaa sovelletaan missäkin tilanteessa) että ei olisi tulossa. Päin vastoin, usein nimenomaan hidastaisi selvästi kuin käyttis skeduloisi säikeet miten sattuu ja tulisi ylimääräisiä kommunikaatioviivetä kun "kriittinen säie" jota ajettaisiin omalla piilastullaan kommunikoikin sittenkin paljon muiden säikeiden kanssa.

No suorituskyky ei ole ainoa asia miltä kannalta näitä mietitään. Kun kellotaajuudet on aikalailla samat niin ytimillä voi sitten segmentoida tuotteita eri hintakategorioihin. Eihän niiden kellotaajuuksienkaan rajoittamisessa mitään teknistä järkeä ollut, jos chippi muuten olisi kulkenut.

maailma on täynnä ARM kamaa jossa homma on jo hoidossa. Intel on myös sitä mieltä että on hyvä idea tehdä epäsymmetrisiä suorittimia. Mikä tässä olisi sellaista joka olisi erityisen vaikeata?

Varmaan lähinnä se, että harvempi nopeuskriittinen softa kulkee korkeintaan kahdella säikeellä ja se käyttöjärjestelmä ei osaa päättää että mitkä niistä tulisi laittaa sille ’nopealle chipletille’ ja mitkä hitaalle. Symmetrisillä CCX:llä on helppo vaan iskeä niitä ensin nopealle niin monta kun mahtuu ja sit loput hitaammalle. Toki tässäkin voidaan niin toimia, mutta silloin suorituskyky alkaa sakkaamaan jo kolmannen säikeen kohdalla (koska windows priorisoi aitoja ytimiä). Symmetrisellä 5+5 konfiguraatiolla vasta kuudes säie alkaa tiputtamaan suorituskykyä viiveiden kasvaessa.

Tämän lisäksi siellä prossuissa voi olla jotain rakenteellisia/loogisia rajotteita joiden takia symmetrisyydestä pitää pitää kiinni. Niistä voidaan tarvittaessa aivan varmasti hankkiutua eroon, mutta se voi tulla suorituskyvyn kustannuksella. Itse ainakin luottaisin siihen, että AMD:lla on tätä asiaa pohdittu ja todettu 2+8 konfiguraatio, ja muut epäsymmetriset, epäedullisiksi ratkaisuiksi.

Henkilökohtaisesti mielenkiintoisempana pidän mahdollisia 14 ytimisiä prosessoreja jotka voivat tulla yllättävän edulliseen hintaluokkaan, sillä niissäkin voidaan käyttää osittain rikkinäisiä chiplettejä. Valmistuskustannukset tulee tolla olemaan tuotepalettiin nähden vastaavat kuin 3900x:llä. Myös 7 ytiminen prossu tulee todennäköisesti ilmaantumaan nykyisten 6 ytimisten tilalle samaan hintaluokkaan samasta syystä. Miksiköhän muuten intel ei ole pistänyt 9, 7 tai 5 ytimisiä prosessoreja myyntiin?

Intelin single core turbo vaatii ydinkohtaisen kellojen hallinnan eikä se näy viipeissä. Eikö L1 cache ole ihan riittävä puskuri?

On edelleen CCX. Se vaan sattuu olemaan saman kokoinen kuin CCD. CCD on fyysinen elementti ja CCX looginen elementti.

Kyllä näkyy;

Zen2n viive 16 megan L3-välimuistiin ~37 kellojaksoa, 9900k:n L3-viive samankokoiseen L3-kakkuun ~55 kellojaksoa, tässä Intelillä on sekä kellodomainin ylitys että väylärakenne jossa selvästi enemmän kohteita (eli siis melko sama tilanne kuin mikä zen3lla tulee olemaan)

Zen1n viive 8 megan L3-välimuistiin ~32 kellojaksoa, 7700k:n L3-viive samankokoiseen L3-kakkuun ~43 kellojaksoa.

Tässä intelillä kellodomainin ylitys sekä väylärakenne jossa hiukan (muttei paljoa) enemmän kohteita.

L1-kakulla ei ole tämän kanssa MITÄÄN tekemistä kun siellä on (L1n kanssa inklusiivinen) L2 kuitenkin ytimen kanssa samassa kellodomainissa.

Mitään teknistä syytä tähän ei ole ainakaan useimmissa arkkitehtuureissa ollut, ainoastaan vaan segmentointikysymys.

Joku 3-ytiminen Sandy Bridge ois ollut liian hyvä ja 2500K ois monelta jäänyt ostamatta. Sen ois pitänyt kuitenkin olla tuota halvempi, ettei 6-ytimisten Phenom II prossujen ylivoima vie mielenkiintoa.

Ja nyt sitten varsinkin joku 10 vs 9 ytiminen kivi olisi aivan turhan lähellä

Ei. ARMin big.LITTLE on AIVAN ERI asia.

Ja jokaisessa luurissa voi olla sille customoitu kernel joka tasan tarkkaan tietää millaiset ytimet sieltä löytyy, ja voi valita sen skedulointistrategian joka sillä toimii hyvin.

x86ssa meillä on:

1) Ilman SMT:tä olevia prossuja

2) SMT:llä olevia prossuja (pitää jotenkin selvittää, mitkä virtuaaliytimet on samalla fyysisellä ytimellä ja ottaa tämä huomioon skeduloinnissa)

3) CMT:llä olevia prossuja (pitää jotenkin selvittää, mitkä "ytimet" on samassa moduulissa, ja ottaa tämä huomioon skeduloinnissa, välillä siten että vältetään näiden yhtäaikaista käyttöä, mutta ehkä välillä siten että jos nämä kommunikoivatkin paljon keskenään(mitä käyttis ei voi oikeasti tietää) , laitetaankin ne ehkä saman modulin "ytimille")

A) Prosessoreita joilla kaikilla ytimillä yhteinen L2-välimuisti

B) 4-ydin-prosessoreita joilla kahdella ytimellä yhteinen L2-välimuisti

C) Prosessoreita, joilla kaikilla ytimillä oma L2-välimuistinsa ja kaikilla ytimillä yhteinen L3-välimuisti

D) Prosessoreita, joilla kaikilla ytimillä oma L2-välimuisti ja M kpl L3-välimuisteja siten että N ydintä käyttä samaa L3-välimuistia.

ja täysin saman kernelin pitää toimia näillä kaikilla.

Tässä on jo ennestään ihan hirveä suo sille, että mitä strategiaa käyttiksen skedulerin kannattaa käyttää minkäkintyylisellä prosessorilla.

Se, että meillä olisi vielä ihan samanlaisia ytimiä siten että saman L3-välimuistin jakavan ydinryhmän koko muuttuisi

olisi jälleen kokonainen ulottuvuus lisää tähän suohon.

Ei tuo ole järkevää, koska 4+4-malli olisi kalliimpi valmistaa kuin 8+0-malli, ja siihen menisi kaksi chiplettiä, jotka voitaisiin myydä kahtena prosessorina. Tilanne voisi olla toinen, jos valmistusprosessin saannot olisivat surkeat ja olisi haasteita saada 8 toimivaa ydintä samalle chipletille. Tämä kuitenkin lienee varsin epätodennäköistä.

Ei ole kumpikaan järkevä tuplamäärällä piitä per suoritinytimien kokonaismäärä yhteen 8 ytimen CCD:hen nähden.

Ja se toisella chipletillä oleva L3:kin olisi pitemmän polun päässä, jos edes tavoitettavissakaan.

Juu. Ja jos siellä tulee merkittävä määrä piilastuja joissa on vain 4 toimivaa ydintä, ne voidaan kuitenkin myydä 4-ytimisinä malleina yhdellä piilastulla.

8-ytimisestä voidaan kuitenkin pyytää enemmän rahaa kuin 2x 4 ytimisestä prosessorista, vaikka valmistuskustannukset ovat pienemmät ensimäisessä, koska kaksi 4-ytimistä vaatii kaksi IO-piiriä ja kaksi paketointia, tuplasti pinnejä jne.

Tai no siis ainahan voi pyytää vaikka mitä, mutta tällä hetkellä 3700X hinta on n. 300€ ja 3300X hinta on n. 130€ ja 3100 n. 110€. Nämä siis Suomessa ja kuluttajamarkkinoille, mutta uskoisin noiden prosessoreiden hintojen olevan melkolailla samalla hintasuhteella myös valmiskokoonpanoja myyville yrityksille.

Toki en usko että saannot ovat niin huonot, että 8-ytimisiä prossuja joudutaan tekemään 4+4 mallina ollenkaan.

Olet varmaan oikeassa, että myyntikate ratkaisee mitä kannattaa valmistuttaa ja myydä. Tekniikka on renki ja myyntikate isäntä.

Me ei tiedetä miten he sisäisesti laskee valmistuttamisen kustannusta (alihankintaa) ja omia kiinteitä kustannuksia per valmistettu tuote, eikä kai oikein sitäkään millä

hinnalla valmistuttaja myy tavaran eteenpäin tukkureille.

kommentoin väitettä ettei ole mahdollista tehdä vuorontajaa. Myös x86 puolella on epäsymmetrisiä suorittimia.

Kuten ei ole mitään järkeä 3300X mallissa?

AMD tekee EPYCcejä 8×2 -toteutuksella (8 chiplettiä x 2 ydintä, yhteensä 16 ydintä, 256MB L3:sta).

AMD Epyc 7F52, 16C/32T, 3.50-3.90GHz, tray ab € 3169,00 (2020) | Preisvergleich geizhals.eu EU

geizhals.eu

Hinta (3169€) on jonkin verran korkeampi kun 16-ytimisen perusmallin (665€).

Ei tuollainen 4+4 kombinaatio mitenkään mahdoton ole, mutta tulkin sellaista julkaisevat.

3300X on ihan eri asia.

Se on yhden CCD:n prossu, eikä käytä mitään toista chiplettiä lisäämään kasauskuluja kuten 4+4 tekisi kahdeksalle ytimelle.

Ja itse asiassa 4+4 tekisi toimintatasollakin juuri päinvastoin jakamalla ytimet takaisin useampaan CCX:än sen yhden 8 ytimen Zen3 chipletin pitäessä ne yhdessä CCX:ssä.

3300X taas pitää ne neljä ydintä yhdessä CCX:ssä, sen sijaan että ne olisivat kahdesta eri Zen2 CCX:stä.

Testissä AMD Ryzen 3 3100 & 3300X – io-tech.fi

http://www.io-tech.fi

Näin minäkin muistelin, lähinnä vain sitä tuumin ettei CCX välistä liikennöintiä tarvita piirisen sisällä joten siinä on säästynyt yksi kerros.

Se on aivan samalla tavalla yhden CCX suoritin kuin hypoteettinen 8+0 Z3 suoritin. AMD on ennenkin käyttänyt tyhjiä piirisiä paketoinnessaan.

Siis mitä ihmettä nyt oikein sekoilet?

Jos halutaan neljä ydintä, sinne täytyy laittaa kokonainen kahdeksan ytimen piilastu, koska mitään neljän ytimen pienempää piilastua ei ole.

Sen sijaan jos halutaan kahdeksan ydintä, sen saa paljon halvemmalla laittamalla sinne yhden kahden ytimen piilastun.

Kun AMDllä oli järkevät syyt siihen.

Eli, kun AMDllä oli jo toimiva serverikanta ja haluttin minimalistisella R&D-aikataululla ja kustannuksilla kustannuksilla tehdä siitä halvempi versio. Ja todennäköisesti käytettiin rikkinäisiä piilastuja.

MIKÄÄN näist’ syistä/tilanteesta ei päde zen3-kuluttaja-Ryzenin kanssa.

Jatkuvasti vedät täysin epärelevantteja "vertailuita" asioihin, jotka on aivan erilaisia kuin mitä "ehdotat".

Markkinoilla on tietääseni tasan yksi "epäsymmetrinen" x86-suoritin(Lakefield), ja se on aivan eri tavalla epäsymmetrinen kuin tuo, mitä ehdotat.

Lakefieldille skedulointiin toimii hyvin yksinkertainen logiikka: Kun ajossa on (vain) yksi raskas säie, se laitetaan isolle ytimelle. Pikkuytimille voi sitten yhtä aikaa skeduloida satunnaisia muita kevyitä säikeitä. Jos sitten liikaa pikkuytimiä työllistyy yhtä aikaa että lämpörajat meinaa alkaa ylittymään, laitetaan iso ydin idlaamaan.

Sen sijaan sellaiselle että olisi muuten samanlaisia ytimiä mutta L3-kakun jako olisi vaan epäsymmetrinen ei ole mitään järkevää yksinkertaista logiikkaa miten sille kannattaisi skeduloida säikeitä

Voisitko nyt olkiukkoilla vähän vähemmän?

3300X:llä ei ole tämän kanssa mitään tekemistä.

Näille on omat erikoiskäyttötarkoituksensa:

1) Sellaiset palvelinsoftat, joissa itse CPU-tehoa tarvitaan hyvin vähän mutta IO-kaistaa paljon.

2) Sellaiset kalliit palvelinsoftat, joiden kalliit lisenssit on hinnoiteltu ydinmäärän mukaan, ja joissa raudan hinta on pientä lisenssin hintaan verrattuna. Tällöin pitää vaan maksimoida ydinkohtainen suorituskyky, jolloin kannattaa laittaa mahdollisimman vähän ytimiä/(IO-piiri + L3-kakku)

Niin nykyisessä mallissa yhden CCXn suoritin on neljä ydintä ja Z3 se on kahdeksan. Molemmissa yhden täyden CCXn suorittimen valmistamiseen tarvitaan yksi piirinen.

Minulla ei ole tietoa miten Z3 aiotaan paketoida, onko sinulla? Vahva oletus on että samaan tapaan kuin Z2 ja kun siinä on kaksi piiristä niin mikä tahansa yhdistelmä on mahdollinen vaikka ei välttämättä todennäköinen.

Minusta taas tuntuu että en ihan täysin ymmärrä miksi olet eri mieltä kun vastaat eri asioihin kuin mitä esitän.

Zen3n työpöytämalli tulee aivan samaan AM4-kantaan ja käyttää hyvin suurella todennäköisyydellä samanlaista (kohtalaisella todennäköisesti jopa täysin samaa) IO-piiriä kuin zen2n työpöytämallit

Koko hypoteesi on jostain Trumplandiasta tullut.

Ei se 8 ydintä mitään 8+0:aa tarvitse, vaan silloin jätetään toinen paikka tyhjäksi kuten nykyisin.

Se tyhjänpanttina oleva toinen CCD/chiplet lisäisi vain kasauskuluja.

Ja saisi olla aika reilusti viallinen chiplet, että siitä ei saisi mitään käyttökelpoista.

Varsinkin jos 10 ytiminen 5+5 konfiguraatio toteutuu.

Käyttökelvottoman chipletinkin tapauksessa roskiin dumppaus olisi se ylivoimaisesti halvin ja helpoin ratkaisu.

Ja jos samojen yhteisten chiplettien käyttö HEDT ja palvelinprossujen kanssa jatkuu Zen3:lla, niin siellä tosiaan löytyy erikoiskäyttöjä, joissa pienemmän ydinmäärän chipletitkin menevät…

Ja paljon desktoppia parempaan hintaan!

Sille vain ei ole mitään loogista, teknistä ja varsinkaan taloudellista syytä, miksi ruveta käyttämään ydinmäärälle tarpeettoman suurta chiplet määrää desktop-prossuissa.

Millos nämä tulee? Pitäisi saada prossua päivitettyä ja amdta nyt odotellaan.

Juu max. 8 ytimisissä prossuissa noin.

Mitäs jos uudesta linjasta tuleekin paljon 4,5,6 ytimellisiä ulos, ehkä jopa 3 ja 7? Eikö silloin ole aika logista, siis taloudellisesti, että tuupataan niistä yksi 10 sisältävä prosessori niin, että aina se ensimmäinen kakku sisältää sen suuremman määrän ytimiä kuin se jälkimmäinen. Schedulerille varmasti kökkö, mutta ne tilanteet missä sitä kakkosta käytetään on kuitenkin vähemmän yleisiä ja usein vähemmän latenssi riippuvaisia, joten lopputulos voisi olla markkinataloudellisesti kannattava. Ei jouduta disabloimaan toimivia ytimiä ja myymään pienempikatteisena prosessorina, vaan voidaan niputtaa noita yhteen isommaksi, mutta vähän halvemmaksi (silti kalliimmaksi kuin disabloituina myytävät) prossuksi.

Jos possu on 8C, niin tuskimpa tulee mitään alle 4C ulos järkeviä määriä, jos valmistus toimii edes semi luotettavasti.. Oikeastaan pitäisi pystyä välmistamaan kyllä min 6c prossuja ( 2:ssa coressa max vikaa).

Ei.

Vaan sitten julkaistaisiin 3- ja 7-ytimiset yhden piilastun mallit jossa käytettäisiin ne 3- ja 7-ytimiset piilastut.

No laskeppa tuosta jos tulee 4-6C niin sehän tekee tasan 10 (6+4). Samaten kuin jos vähän tulee niitä missä vaikka 7 tai 3, niin nekin yhdistämällä saa molemmat käyttöön. Toki 7 ja 3 alkaa varmasti olemaan jo aivan ääripäätä. Mehän emme vielä tiedä, että miten uudet linjastot toimii, alussa kuitenkin saannit lienee huonompia kuin sitten joskus myöhemmin.

En ihan ole kanssasi samaa mieltä kannattavuudesta, jokainen rypäs pitää kuitenkin testata ja sitten sieltä ne jollain systeemillä kuitenkin valitaan jatkoon. Eli ei se työmäärä kasva käytännössä ollenkaan vaikka niitä stackkaa alustalle missä tahansa comboissa, koska jo nyt ne pitää samalla tavalla sinne laittaa tekee sen sitten automaatio tai ihminen.

Jokaisessa CCX:ssä pitää olla sama määrä ytimiä aktiivisena, eikä tällä hetkellä ole mitään viitteitä siitä että se olisi muuttumassa vaikka "CCX" onkin jatkossa neljän sijasta kahdeksan ydintä.

7 ydin chipit voidaan myydä vallan hyvin esim 7 ydin prossuina tai 14 ydin prossuina. Ja 4 ydin chipit 4 ydin tai 8 ydin prossuina. Ei ole järkevää tehdä prossua, joka toimisi auttamatta huonosti ja pilaisi firman maineen.

Hyvin suureen osaan käyttöä riittää ihan 4C8T prossu, paremmin, kuin erinomaisesti.

Kyllä me kaikki tuon tiedämme, tässähän spekuloitiinkin sillä mahdollisuudella, että Zen3 tulisi muutos tuohon. Emme me asiaa tiedä, vaan spekuloitiin. Siksihän tuosta schedulerista puhuttiinkin.

Vaan yhtään 7 ydin prossua ei ole myynnissä vaan niistä koneella disabloidaan X määrä ytimiä ja myydään vasta sitten.

7-ytimisiä prossuja on ollut vaikka millä mitalla, tosin ei x86-prossuja normaaleihin PCihin.

7 ydintä ei onnistunut zen1/zen2lla koska jokaisessa CCXssä pitää olla sama määrä ytimiä.

Zen3lla 7 ydintä onnistuu.

Ymmärtääkseni Zen 3 tulee vain hieman viritetyllä valmistusprosessilla, joten vaikea uskoa että saantien kanssa olisi suurempaa ongelmaa.

Kun tässä spekuloidaan näistä kaiken maailman 3- ja 7-ytimisistä prosessoreista, niin mielestäni se on aika turhaa. Liian hienojakoisesta tuotesegmentoinnista tulee vain riesaa. Yleensä valmistajat parempaa kannattavuutta tavoitellessaan pyrkivät nimenomaan yksinkertaistamaan tuotevalikoimaa, ja prosessoreja on jo nykyään aika paljon per mallisarja.