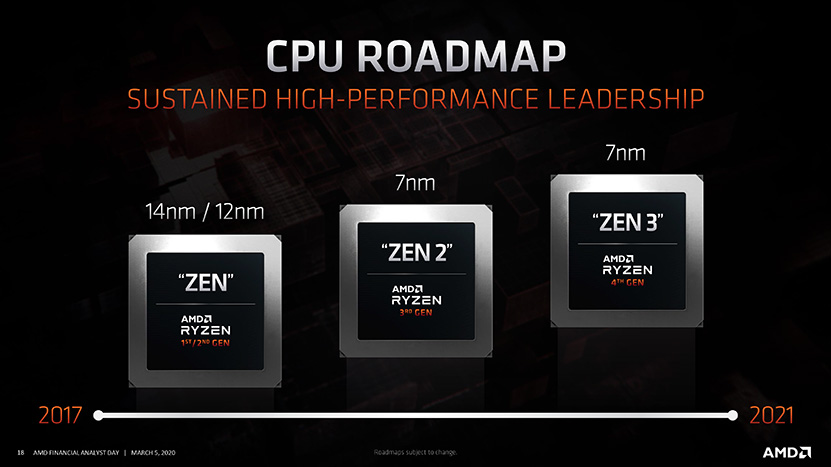

AMD:n odotetaan julkaisevan vielä kuluvan vuoden aikana uudet Zen 3 -arkkitehtuuriin perustuvat prosessorit. Ensimmäisenä linjalta ovat tulossa ulos Milan-koodinimelliset Epyc-palvelinprosessorit ja Vermeer-koodinimelliset Ryzen-prosessorit.

DRAM Calculator for Ryzen ja ClockTuner for Ryzen -sovelluksistaan tunnettu Yuri ”1usmus” Bubliy on nyt twiitannut uusia tietoja tulevista Ryzen-prosessoreista. 1usmusin mukaan yksi Zen 3:n uusista ominaisuuksista on nimeltään Curve Optimizer, mikä mahdollistaa prosessorin Boost-toiminnon konfiguroinnin käyttäjän toimesta. Lisäksi kaikki prosessoriytimet ovat nyt ylikellotettavissa toisistaan riippumatta.

AMD tulee 1usmusin mukaan myös laajentamaan tuotekirjoaan tuomalla markkinoille 10-ytimisen Vermeer-prosessorin, kun nykyisessä tarjonnassa 8-ytimisistä hypätään suoraan 12-ytimisiin. Kolmas paljastus koskee puolestaan Infinity Fabric -väylää, jolle ollaan tuomassa ilmeisesti lisää jakajia, mitkä tulevat puolestaan mahdollistamaan aiempaa hieman korkeammat muistikellotaajuudet.

1usmusin mukaan kaikki yllä mainittu tieto on luettavissa mistä tahansa AMD:n emolevyn BIOSista, mikä perustuu uuteen AGESA 1.0.8.1 -versioon.

Lähde: 1usmus @ Twitter

Koska tuollaisilla uutisilla saadaan klikkejä, eikä mikään sano että kyseinen väitetty vuoto olisi edes ikinä pitänyt paikkaansa, Bits’n’Chipsiltä on muitakin huuhaa"vuotoja" tilillään.

Noista kerrotaan tietyissä yhteyksissä ja tilaisuuksissa, se ei tarkoita että voit soitaa TSMC:lle ja kysyä mikä on sen ja sen asiakkaan sen ja sen piirin yieldit, mutta prosessin yieldeistä kerrotaan esimerkiksi alan tapahtumissa, firman lehdistötilaisuuksissa yms.

Mistä sinä nyt vielä N7+:n tähän soppaan revit?

Kuinka vaikea se on ymmärtää, että tässä on kyse aivan eri tilanteesta?

Edelleen jatkat täysin rikkinäisiä vertailuita aivan eri tilanteeseen ja sotket asiaan vaikka mitä siihen täysin liittymätöntä.

Se, mitä sinä olet "ehdottamassa" ei sisällä mitään erinopeuksia ytimiä vaan tasan yhtä nopeita ytimiä.

Vaan tässä on kyse siitä, mitkä ytimet jakavat mitäkin välimuisteja keskenään.

Se, että windows ehkä jollain tavalla tukee "erinopeuksisa" ytimiä ei auta YHTÄÄN tämän kanssa kun kyse on TÄYSIN ERI ASIASTA.

Intel kyllä tekee jonkun verran foundry-valmistusta kolmansien osapuolien custom-piireille, tosin usein kai siten että sinne piirille tulee sittne samalla myös aika paljon Intelin suunittelemaa logiikkaa mukaan, esim. Intelin prossuytimiä.

Mutta ilmeisesti neuvottelut näistä käydään sitten firmojen välillä tiukkojan NDA-sopimusten alaisina eikä näitä mainosteta samalla tavalla julkisesti kuin mitä TSMC ja Samsung mainostavat prosessejaan.

Eikös tuossa olisi hyvinkin useissa skenaarioissa "kahden nopeuksisia ytimiä" jos yksi CCX ois 8 ydintä 32 megan L3 välimuistilla ja toinen CCX olisi 2 ydintä 32 megan L3 välimuistilla?

Toki CCX:t osaa lukea ristiin välimuistejaan mutta tätä pyritään aina välttämään

tl,dr: jos AMD tuo 6 ytimiset mallit markkinoille 7 ytimisten sijaan tohon perus budjettiluokkaan, niin kyseessä on puhdas tuotesegmentointipäätös ja niistä noin 97% voisi avata 7 ytimen malleiksi. Lisäksi tossa 5+5 10core mallissa ei ole mitään järkeä kuin tuotesegmentointimielessä, vaikka saannot olisi ihan kauheat. Tuotantoteknisesti ainoat järkevät mallit on 7,8,14 ja 16 ytimiset mallit, joista jokaisesta pari eri kellontaajuuskategoriaa (esim. bottom 90% ja top 10%). Lisäksi joku 6 ytiminen jämämalli voidaan tuoda markkinoille joskus myöhemmin kun niitä on ensin kerätty järkevä määrä. Periaatteessa todella huonosti kellottuvia ytimiä voisi disabloida ja siten saada kasvatettua noita ’6 ytimisten’ prosessorien suhteellista määrää, mutta jos tämänkin uutisen huhut pitävät paikkaansa, niin niitäkin voitaisiin hyödyntää juuri niillä kellontaajuuksilla kuin mihin ne pystyvät.

Tänne ei saa exceleitä upotettua, mutta alla vielä screenshotti ihmeteltäväksi, voin privassa heittää sen itse excelin ihmeteltäväksi jos käytetty matematiikka ihmetyttää:

Ei.

Kun molemmilla on ajossa yksi säie, ne toimivat tasan yhtä nopeasti.

Kun molemmilla on ajossa kaksi säiettä, ne toimivat tasan yhtä nopeasti.

Toiselle ainoastaan voidaan skeduloida enemmän säikeitä ja tilanteessa kun siellä on ajossa enemmän säikeitä, voi suorituskyky sitten hidastua kun usemapi säie käyttää sama L3-kakkua.

Mutta mikään "skeduloidaan eniten suorituskykyä tarvitseva säie nopeimmalle ytimelle"-logiikka ei toimi järkevästi kun ei ole mitään "nopeinta ydintä".

Ja logiikka "skeduloidaan eniten suorituskykyä tarvitseva säie yksinäiselle ytimelle" toimii vaan pessimointina, hidastaen pelien kaltaisilla workloadeilla joilla on yksi raskas säie joka kommunikoi melko paljon muutaman kevyemmän säikeen kanssa.

Ei suoraan, ainoastaan oman CCXn välimuistin kautta. Jos data löytyy toisen CCXn välimuistista, se pitää kopioida sieltä oman CCXn välimuistiin ennen kuin sitä voi käyttää. Jos molemmat CCXt käyttää samaa dataa, sen pitää olla molempien CCXien välimuisteissa.

Ja jonkun CCXn ydin ei voi koskaan "ladata dataa toisen CCXn välimuistiin". Se toisen CCXn L3-välimuisti ei toimi "L4-välimuistina CCXn välimuistille".

Hyvä, voitko avata miten ne eroavat? Jokseenkin varmana kai pidetään että piirinen sisältää vain yhden kahdeksan ytimen CCXn, mutta loppu on kait vielä oletusta?

Voi olla että minulla on jotain mennyt ohi mutten nyt äkkiä löytänyt verkostakaan mitään varmistettua. Jos aikaisemmista viesteistäsi olen oikein poiminut niin ytimellä on oma L1, CCXn ytimien kesken jaettu L2 ja CCX ryhmien kesken jaettu L3. Mikä yksityiskohta tästä vielä puuttuu jotta ytimien näkemä kuva keskusmuistista olisi eri ytimien välillä joilla on eri määrä naapuriytimiä?

Juuri selitin eilen, näkyy täällä EDELLISENÄ VIESTINä tuohon postaukseesi

1usmus: Zen 3:sta 10-ytiminen versio, ydinkohtainen ylikellotus ja muita uudistuksia

bbs.io-tech.fi

Ei. Vaan joka ytimellä on oma L2-välimuistinsa.

Et vielä sekavammin osaisi tätä sanoa?

Jokaisella CCXllä on oma, CCX eri ytimien jakama L3.

L2 on zen-arkkitehtuurissa ydinkohtainen.

Tämä selviäisi ziljoonasta eri lähteestä todella nopeasti paikasta jos yhtään jaksaisi ottaa asiosta selvää sen sijaan että postaa cargo cult-speksejä ja mutua. Esim. googlen kuvahakuun "zen l2 cache" tuottaa ekana seuraavan osuman:

Pitää olla, muuten tulee ongelmia. Tuon osalta tilanne tulee pysymään samana. Oletan nyt siis että tarkoitat sitä että jos sama tavu yritetään lukea muistista kahdelle eri CCX:lle, niin se joka lukee sitä vuorossa toisena joutuu tarkistamaan sen mahdollisen tilan muista L3 välimuisteista.

Tarkemmin ottaen kun toinen muuttaa alkion sisältöä niin päivittyykö sama tieto vai merkitäänkö se vain likaiseksi. Jos ensimmäinen niin en näe että käyttöjärjestelmän puolelta katsottuna on mitään eroa millä piirisellä säie on ajossa. Jos jälkimmäinen niin sitten kyllä.

MOESI protokollaa käyttää ihan normaalisti mikäli olen oikein ymmärtänyt.