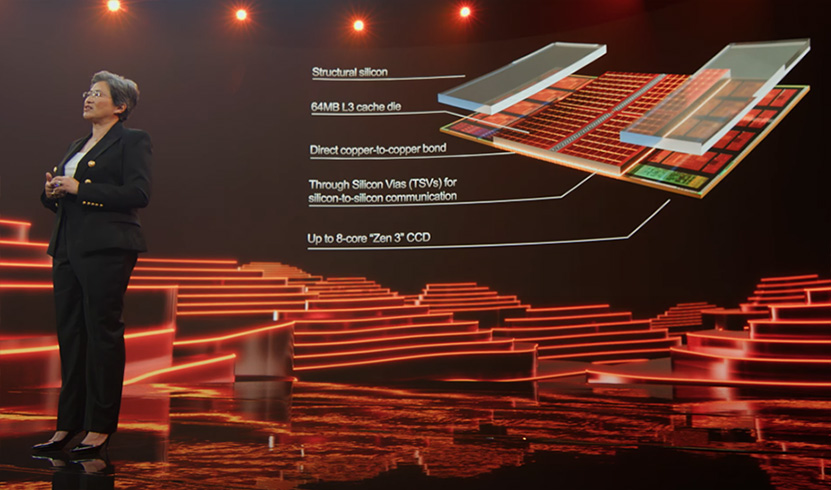

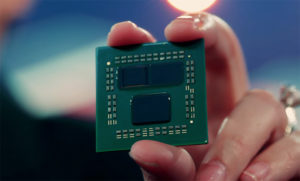

AMD:n toimitusjohtaja Lisa Su kertoi Computex-virtuaalimessujen keynote-esityksensä päätteeksi yhtiön edistysaskeleista piirivalmistuksen ja paketoinnin saralla. Su esitteli toimivaa prototyyppiä 12-ytimisestä Zen 3 -arkkitehtuurin Ryzen 9 5900X -prosessorista, jossa molempien TSMC:n 7 nanometrin prosessilla valmistettavien CCD- eli Core Chiplet Die -piirien päälle oli pinottu 64 megatavua ylimääräistä SRAM-muistia. 3D V-Cache -teknologian avulla prosessori L3-välimuistin koko on saatu kolminkertaistettua 192 megatavuun (32 + 64 Mt per CCD). SRAM-muistipiirin koko on 6 x 6 millimetriä (36 mm^2) eli noin puolet CCD-piirin pinta-alasta ja se oli liitetty piisiruun Through Silicon Vias -tekniikan avulla (TSVs). .

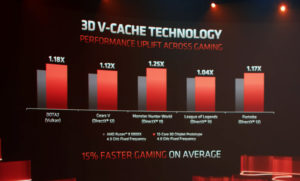

Käytännön demona AMD esitteli Ryzen 9 5900X -prosessoria toimimassa kiinteällä 4 GHz:n kellotaajuudella ja verrokkina oli vastaava 3D V-Cache -prosessorin prototyyppi. 3D V-Cachen mahdollistaman isomman L3-välimuistin avulla AMD kertoo ruudunpäivitysnopeuden paranevan peleissä Full HD -resoluutiolla keskimäärin 15 %.

- DOTA2 (Vulkan): +18%

- Gears 5 (DX12): +12%

- Monster Hunter World (DX11): +25%

- League of Legends (DX11): +4%

- Fortnite (DX12): +17%

AMD ilmoitti olevansa valmis ottamaan 3D V-Cache -teknologian käyttöön tämän vuoden lopulla. Samassa yhteydessä AMD varmisti olevansa 5 nanometrin valmistusprosessin kanssa aikataulussa ja tuovansa Zen 4 -prosessorit markkinoille ensi vuonna.

Lähde: AMD

Mahtaako AM4 saada näistä ison cachen prosuista jatkoaikaa?

Nimim. ”B450”

Jatkon lupaaminen AM4-alustalle palauttaisi puoliksi jo kuolleen alustan takaisin elävien kirjoihin. Eli jos sitä on niin se kannattaisi ehkä kertoa , ettei porukka lykkäisi ostoja ddr5-aikaan.

Ilmeisesti 5600x, 5800x yms tulevat saamaan kunnollisen XT päivityksen. Hienoa AMD! Toki on surullista seurata vierestä Intelin laskevia myyntejä ja sitäkin surkeampia tuotteita

Enemmän tuosta tosin olisi hyötyä paritettuna high-end APU:n kanssa……

Spekuloin että tuo voisi olla joissain peleissä jopa "nopeampi" kuin Zen 4 ilman vastaavaa cachea.

Se toteutuisi niin, että olisi vähemmän latenssipiikkejä, vaikka keskimääräinen fps jäisi huonommaksi.

Tietyn fps-tason jälkeen (VRR ja 80-100 fps?) silmä ei välttämättä havaitse kuin latenssipiikit ja keskimääräisen fps:n merkitys vähenee.

Mielenkiintoinen kysymys on, että missä tuo lisäkakun TAGit(kirjanpito) on. Onko se tuolla SRAM-lisäpiirillä, vai onko siellä zen3-CCD-piilastulla jo ennestään luokkaa kuutisen megaa ylimääräistä SRAMia näille tageille käyttämättömänä nykyisissä zen3ssa?

Tästä ei myöskään oikein selvinnyt, että onko tämä nyt demottu malli tulossa myyntiin vai ei.

Koska jos tulisi myyntiin, pitäisi kyllä hintaakin olla aika paljon koska tuo melkein tuplaa kehittyneellä prosessilla valmistetun piipinta-alan.

Tietyllä tavalla järkevintä olisi, että tämä zen3-malli olisi vaan protoilu ja sitten Zen4ssa varsinaisella CCD-piilastulla ei olisi L3-kakkua ollenkaan vaan kaikki L3-kakku olisi tällä sen päälle tulevalla piilastulla. Ja se zen4n L3-piilastu voisi ehkä olla aivan sama 64 MiB piilastu kuin tämä nyt demottu.

Mutta toisaalta, jos tämä toimii täysin jo zen3n kanssa, ja antaa mukavasti nopeutta lisää, niin miksi ei myydä sitä sitten kunnolla kalliiseen hintaan huippumalleina?

Tämä kyllä selittää niitä ristiriitaisia huhuja zen3+n suuntaan, kun zen3+ onkin paljon kalliimpi valmistaa kuin zen3, niin riippuu selvästi kilpailutilanteesta että tarvitaanko tätä ”kruunun pitämiseen” vai ei.

Tästä ei myöskään sanottu, että millä valmistustekniikalla tämä SRAM-piilastu oli tehty. Se, että tässä on saatu 64 megaa mahtumaan (melkein) samaan pinta-alaan kuin 32 megaa CCD-piirillä, vihjaisi siihen, että tämä saattaisi olla jo jollain uudemmalla tiheämmällä valmistustekniikalla valmistettu, mutta tämä ei ole varmaa.

SRAM-piiri on helpompi saada uudella valmistustekniikalla toimimaan ja kohtalaisille saannoille kuin logiikkaa sisältävä piiri, mutta toisaalta SRAM skaalautuu hiukan huonommin kuin logiikka pinta-alansa suhteen uusille valmistusprosesseille, eikä tässä pelkkää L3-kakkua sisältävässä piirissä virrankulutuksella ja maksiminopeudella ole niin paljoa väliä kuin ytimen logiikassa.

Eikun kyllä siellä näköjään sanottiin ”7-nanometer” tuosta SRAM-piiristä.

Omasta mielestä tästä tekee mielenkiintoisen se että jatkossa voidaan kakku valmistaa eri valmistusprosessilla kuin ytimet. Eli tulevaisuudessa jos mennään edelleen chipleteillä ja erillisellä IO-piirillä, niin voi olla vaikka kolme eri valmistusprosessia käytössä. Tuollaisia kaakkupaloja saadaan varmaan aika kovalla saannolla tehtyä, eli riippuen siitä miten helppo taikka hankala toi itse paketointi sitten on, niin ei välttämättä nosta hirveästi edes kustannuksia.

Kunpa näin kävisikin Mutta harva näillä markkinoilla alle yleisen tason luopuu vanhastakaan raudasta

Mutta harva näillä markkinoilla alle yleisen tason luopuu vanhastakaan raudasta

Ei siinä muuta mahdollisuutta ole ollut. Nythän nuo TSV:t on löydetty jo vanhemmistakin Zen3:n die-shoteista, ja Zen3-huhuissahan oli jo aikanaan L3 cachen määrä 32+……

Ilmeisesti Milan prossujen BIOS tukee vain neljää pinoa per chipletti:

Silti aika möhkäle tommonen 288 megaa nopeaa kakkua kahdeksaa ydintä kohden. Täysi EPYC prossu sisältäisi tällöin yhteensä vaatimattomat 2,3 gigatavua L3 kakkua.

Juu ja tuossa vielä kuva biossin valinnasta

Siinä voi kilpailijan tuote jäädä hieman jalkoihin kun cache intensiivinen case osuu kohdalle.

Ei sillä etteikö ne jäisi jalkoihin jo muutenkin.

Juu voisi kuvitella,että APU jossa LLC:tä joku 96-128MB ja RDNA2 arkkitehtuurin GPU ja tuosta infinity cachea antaisi jonkunlaista boostia, kun tuo 2x DDR4 on niin paha pullonkaula GPU:lle. Toki aika maltilliset tekstuurit ja graffa asetukset pitäisi valita.

Tosin onkohan liene liian kallista sekin, kun ei noihin APUihin ole vara pistää muutakaan GPU:lle dedikoitua rammia vaikka teknisesti olisi mahdollista.

Haastavampi lämmönhallinta varmaankin vaatii kellojen tiputtamista verrattuna vastaavaan suorittimeen ilman päälle ladottavia piipaloja.

Ainakin energiatehokkuus kasvaa hurjasti kun joutuu/pystyy käyttämään prossua pienemmällä kellotaajuudella ja jännitteellä ja silti saamaan saman suoritusnopeuden ulos.

Palvelimissahan tämä on erittäin hyvä myyntivaltti.

Juu, ja tosiaan itse pitäisin zen4n EPYCeille, threadrippereille ja pöytämalleille järkevänä, että ne myös olisi eri valmistustekniikkaa:

IO-piilastu edelleen "12nm" että saadaa mahdollisimman halpa hinta/pinta-ala piireille joissa on paljon suuria IO-transistoreita eli koko on joka tapauksessa iso, eikä tuotantorajoitteita, kakkuna tämä "7nm" koska SRAM-transistori tullee vielä toistaiseksi "7nm"llä halvemmaksi kuin "5nm"llä, ja itse ytimet "5nm"llä maksimaalisen suorituskyvyn ja pienen sähkönkulutuksen saavuttamiseksi.

TSMCn "5nm" tekniikalla SRAM-solun minimikoko on tuoreimpien tietojen mukaan 0.021um^2

TSMC’s 5nm 0.021um2 SRAM Cell Using EUV and High Mobility Channel with Write Assist at ISSCC2020 – Semiwiki

semiwiki.com

TSMCn "7nm" tekniikalla SRAM-solun minimikoko taas on 0.027 µm^2.

7 nm lithography process – WikiChip

en.wikichip.org

Eli TSMCn "5nm"llä SRAM on vain n. 1.285x tiheämpää kuin TSMCn "7nm"llä tehty SRAM, vaikka muuten TSMC mainostaa prosessin olevan n. 1.8x tiheämpi (todellinen tiheysparannus jollain CPU-ytimen kaltasella sekalaista kamaa sisältävällä IP-lohkolla on kyllä selvästi huonompi kuin tuo 1.8x).

Ei välttämättä – tuo pino on vain CCX:n L3-cachen päällä ja logiikkaosien päällä on eripalat jotka voidaan optimoida lämmönsiirtoon ja tämä yhdessä ohennetun CCX:n piin kanssa voi johtaa hyväänkin lämmönhallintaan.

katso liitettä 618451

Piitä se näyttäisi olevan, eli ei sitä nyt kauheasti paremmaksi voida optimoida kuin perus pii. Voisi kuvitella että tuon pitää olla hyvin tarkkaan samoilla lämpölaajenemislukemilla (eli samaa materiaa) kuin ympäristö. Muuten kuuluu vain poks ja koko setti palasina. Toki nuo varmasti tehdään mahdollisimman ohuiksi juuri siksi että se lämpö siirtyisi optimaalisesti.

Se kiinnostaa, tuleeka tästä zen3+ vai tuleeko tämä XT versioihin vai vasta zen4 malleihin oikeasti joku pinon yläpäähän tuleviin malleihin.

Loppuvuodesta johonkin Zen3 tuotteeseen tulossa:

Joidenkin huhujen mukaan IO-sirut siirtyisivät TSMC:n 6nm:lle seuraavaksi.

Thänks!

Kyllähän nuo varmaan arvokkaita ovat verrattuna perusmalleihin, mutta jos joku haluaa lisätehoja hinnasta välittämättä, niin saa ihan hyvän siivun!

Voi hyvinkin tulla mieleen päivittää johonkin noista nykyisestä 3000 sarjalaisesta.

Joojoo Steamin tilastojen mukaan taitaa olla edelleen käytetyin reso.

Miten paljo parannus on 1440p resolla?

15%, jos näyttis on 50% nopeampi

Juu. Katsotaan mitkä piirisarjat olisi bios-tuen piirissä.

Tämä alkaa olla jo hieman kulunutta trollausta. Muropaketti testasi prossuja 4K resolla ja sai tulokseksi sen että 100€ ja 1000€ prossulla ei ollut mitään eroa. Nyt ollaan sentään päästy jo eroon 720p testauksesta kun näyttiksille 1080p alkaa olla riittävän kevyttä.

Juu,ja onhan noita muutamia pelejä jossabmikään uusinkaan prosessori ei ole edes isommilla resoluutiolla tarpeeksi nopea. Esim uusin ms:n flight simulator.

Juu tietysti. Jos noilla samoilla peleillä haluaisi saman tuloksen, niin näyttiksen ollessa 100% nopeampi tulos olisi melko tarkasti sama.

Höh.

Eikös nuo Zen 4:t ole eri kannalla tosin ? En sitten tiedä onko noita päivityskiimasia enää tarpeeksi siihen, että ostavat taas uuden emolevyn (ja muistit?) jotta hinta painuisi alas muualla kuin huuto.neteissä.

Mistä sinä nyt Zen 4:n tähän vedit? Ja miksi nämä tarvitsisivat eri emolevyt tai muistit nykyisiin verrattuna?

Parannus on yhtä suuri, jos fps-targetti on molemmilla resoilla sama.

Itse ymmärsin että tämä tosiaan ajeltiin R9 5900x -suorittimen prototyypillä, jota siis ei käsittääkseni AMD ole lupaillut myyntiin vaan tarkoituksena oli demota tuota 3d V-Cache -teknologiaa.

"AMD ilmoitti olevansa valmis ottamaan 3D V-Cache -teknologian käyttöön tämän vuoden lopulla. Samassa yhteydessä AMD varmisti olevansa 5 nanometrin valmistusprosessin kanssa aikataulussa ja tuovansa Zen 4 -prosessorit markkinoille ensi vuonna. "

Tästä jotenkin jäi sellainen mielikuva että tuota teknologiaa lähinnä väläyteltiin etukäteen ennen Zen 4 -prosessoreita. Zen 4 ei ainakaan minun viimeisimmän käsityksen mukaan tule enää am4 -kannalla, joten ei kannata vetää ostohousuja vielä tässä vaiheessa jalkaan.

Ettei jää epäselvyyksiä: AMD on varmistanut, että se julkaisee Zen3-prosessoreita 3D V-Cachella tänä vuonna. Zen 4 saattaa hyödyntää tai olla hyödyntämättä samaa teknologiaa, se nähdään sitten ensi vuonna.

AMD Demonstrates Stacked 3D V-Cache Technology: 192 MB at 2 TB/sec

http://www.anandtech.com

In a call with AMD, we have confirmed the following:

Tuo "thermally efficient support silicon" saattaisi olla vaikka jotenkin lisäaineistettua piikidettä (seosta) jossa olisi vähän parempi lämmönjohtavuus kuin puhtaassa piissä.

Lisäksi piipalat voisi olla leikattu kiteestä semmoisessa suunnassa, johon lämpö johtuu parhaiten. Ei ole ainakaan heti selvää että lämmönjohtavuus yksittäiskiteessä olisi tasan sama kaikkiin suuntiin.

Puolen minuutin googlaamisella löysin jotain lämpötilakertoimia puhtaan piin yksittäiskiteelle. Jos näkisi vaivaa niin voisi etsiä vanhoista tiedelehdistä mittauksia eri kidesuuntiin.

Lämpötilakertoimista näkyy, että piin lämmönjohtavuus riippuu vahvasti lämpötilasta ja heikkenee lämmön noustessa 300…400 K välillä (27…127 C): 1,56 –> 1,05 W/(cm K).

Jotta lämpö johtuisi pois, piipala olisi hyvä pystyä pitämään viileänä. Tarkkaan ottaen CCD:n ei tarttisi pysyä viileänä mutta piipalat siis mielellään voisi pysyä.

katso liitettä 618716

Periaatteessa varmaan on mahdollista että AMD on onnistunut sijoittamaan sen V-Cache lastun kokonaan siihen normaali piilastun ns hukkatilaan joka flip-chip lastussa on se puoli mitä vasten jäähy tulee.

Että välttämättä hot spottien jäähdytyksestä ei tule mitenkään erityistä ongelmaa sen enempää kuin se on Zen 2 ja Zen 3 prosessoreissa kun kerran lastun korkeus ei muutu tässä ratkaisussa.

Z-korkeus pysyy ennallaan, v-cache ja itse ydinsiru tehdään matalammiksi.

Tämä tarjoaa kyllä myös mukavan päivityspolun. Itselläni on 5600X, mutta myöhemmin voisi kiinnostaa cachella varustettu versio 5900X:stä.

Hyvä näin. Mutta "thermally efficient structural silicon" voi periaatteessa olla semmoistakin mistä olisi kiva kuulla tarkemmin, mutta tuskin kovin paljon kerrotaan.

Joo, kunnes toisin todistetaan niin markkinointi buzzwordeja

Mutta periaatteessa tuo antaisi vapauden "liimata" siihen semmoinenkin piipalanen tai kuka ties jotain muutakin materiaalia mille puolijohteen valmistaminen ei onnistu mutta mikä johtaa lämpöä paremmin.

Zen 4 ei tule tänävuonna, vaan todennäköisimmin ensivuonna computexissä Q2 aikoihin tai ehkä jopa erillisenä tapahtumana maaliskuussa.

AMD:n tähän astinen julkaisusykli tukee tätä väitettä:

2022 maaliskuussa olisi kulunut 16 kk zen 3 julkaisusta(marraskuu 2020). zen 2(heinäkuu 2019) ja zen 3 välillä oli 16 kk ja zen+ (huhtikuu 2018) ja zen 2 välillä oli 15 kk.

Joten en jaksa uskoa että tiivistäisivät zen 3 ja zen 4 välin 13 kuukauteen, jotta ehtisi tämän vuoden joulumarkkinoille.

Niin ja tuossa ylempänä olevan mukaan nämä menee tuotantoon vuoden lopussa eli myyntiin luultavasti Q1 2022.

Itse en näe tämän olevan ongelma kun kynnys ostella emot ja muistit uuden prossun mukana on sen verran korkea että asiakkaita varmasti riittää molempiin haaroihin ilman kovinkaan suurta ristiriitaa.

Nimenomaan. Mietin tässä vain etukäteen että liekö kannattavampaa pelikäyttöön hankkia ennemmin tällaista v-cachella varustettua edellisen sukupolven suoritinta ennemmin (joissa emolevytkin on jo varmasti halvempia kuin laukaisussa uudelle Zen 4:lle) vaiko ei. Noiden julkaisusykleissähän ei ole kuin yksi vuosineljännes väliä, joten pidän hieman outona kuitenkin tätä.

Komppaan KVahlman:ia eli myyntiin tulee varmaan q1 tuo v-cache prossu. En siis tarkoittanut muuten että Zen 4 olisi tänä vuonna tulossa, vaan että nuo olisi tulossa myyntiin samana vuonna 2022.

Ei tällä esitellyllä teknologialla, eli TSMC:n tuotannossa on mahdollista pinota 7nm piiri 7nm piirin päälle ja joskus tulevaisuudessa 5nm piiri 5nm piirin päälle. Piirien liitäntöjen ollessa noin pieniä on niitä haastavaa saada tarkasti linjaan samalla valmistusprosessillakin, tämä tekniikka on vasta tulossa tuotantokelpoiseksi 7nm:n osalta. Eli tämä teknologia ei mahdolista eri prosessilla valmistettujen piirien pinoamista mutta mahdollistaa samalla prosessilla tehtyjen piirien pinoamisen aikaisempaa paljon tiheämmillä liitännöillä – joista seuraa parempi energiatehokkuus yms. etuja.