Tekniikan kehityksen kannalta avainasemassa olevien valmistusprosessien kehitys on viime vuosina hidastunut ja näillä näkymin on edelleen hidastumaan päin. Oman mausteensa soppaan tuovat myös eri tasoiset epäonnistumiset ja myöhästelyt, kuten Intelin surullisenkuuluisan 10 nanometrin prosessin tapauksessa.

WikiChip on ollut mukana IEEE:n jokavuotisessa International Electron Devices Meeting -tapahtumassa (IEDM), jossa on kuultu jälleen uutta eri puolijohdevalmistajilta. Mielenkiintoisinta ja toisaalta ikävintä antia tarjoili TSMC tulevilla 3 nanometrin luokan N3-perheen prosesseillaan: SRAMin skaalautuminen on pysähtymässä ainakin toistaiseksi.

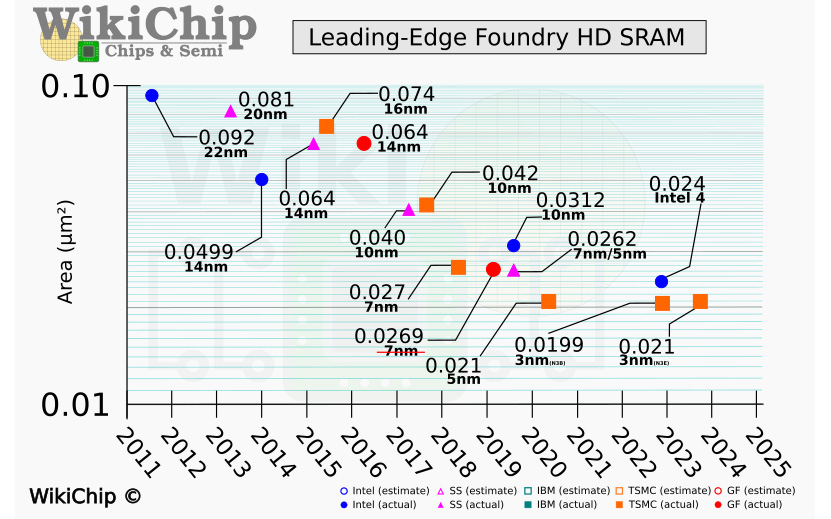

AMD toi esille RDNA3:n julkaisussa jälleen syitä, miksi se on siirtynyt useampaa sirua käyttävien piirien strategiaan. Yksi merkittävä tekijä näissä oli analogisten elementtien nollaa lähentelevä skaalaus, jonka lisäksi muistin skaalautuminen on yhtiön mukaan hidastunut selvästi, mikä on puolestaan ongelma koska juuri SRAMiin perustuvien välimuistien kasvatus on ollut viime sukupolvissa yksi merkittävistä tekijöistä lisäsuorituskyvyn takana. AMD:n ilmoittamaa muistin skaalautumisen hidastumista tukevat myös TSMC:n IEDM:ssä kertomat luvut.

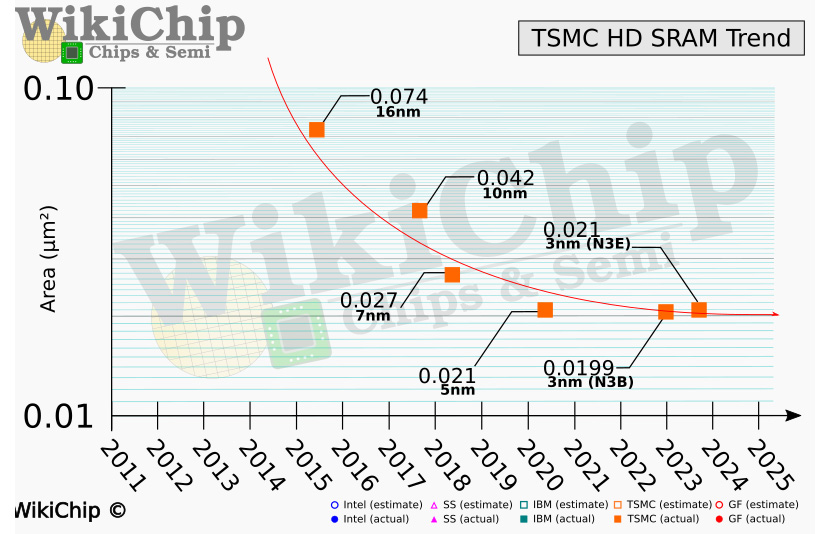

Nykyisen N5-prosessilla SRAM-solujen koko on 0,021 µm2. Tuleva N3-prosessi tulee edelleen kutistamaan sitä, mutta vain aavistuksen; SRAM-solujen kooksi kerrotaan olevan N3-prosessilla 0,0199 µm2. Vielä ikävämmäksi asia muuttuu siksi, että vain harvojen odotetaan käyttävän perusmuotoista N3-prosessia ja ottavan sen sijasta käyttöön N3E-prosessin, jota ei ole viritetty niin äärimmilleen. N3E:llä SRAM-solujen koko on samat 0,021 µm2 kuin N5:lläkin. N5:ttä edeltäneellä N7-prosessilla SRAM-solut olivat kooltaan 0,027 µm2, mutta jo silloin oli nähtävissä merkkejä skaalautumisen hidastumisesta. WikiChipin mukaan tilanne on vastaava myös muilla valmistajilla.

Tällä hetkellä todennäköisimmältä tieltä eteenpäin lähitulevaisuudessa näyttää AMD:n jo valitsema tie, jossa välimuistia sijoitetaan mahdollisesti vanhemmilla prosesseilla valmistettuina erillisille siruille itse pääsirulta. Tämä mahdollistaa välimuistien kasvamisen tiettyjen rajojen sisällä vielä tulevaisuudessakin, ilman että hinta räjähtäisi käsiin uunituoreen prosessin huonosti tai ei lainkaan skaalautuvien SRAM-solujen kanssa. Pidemmällä tähtäimellä esimerkiksi eurooppalainen puolijohdetutkimuslaitos IMEC on kuvaillut nykyiseen verrattuna noin kaksinkertaisen tiheyden SRAM-muisteja, mutta niiden kohdalla puhe on ollut kahden nanometrin luokan prosesseja kehittyneemmistä prosesseista. Myös tutkimusta muiden muistityyppien hyödyntämisen osalta tehdään luonnollisesti jatkuvasti, mutta niiden kanssa joudutaan ainakin tällä hetkellä tekemään jo kompromisseja muissa ominaisuuksissa tiheyden kasvattamiseksi.

Lähde: WikiChip

Ennemmin tai myöhemmin juu mutta ei piin rajat ole tulleet vielä vastaan. Eri asiat vain skaalautuvat eri tasolla, analoginen i/o esim vaatii sen tietyn tilan eikä auta vaikka miten valmistusprosessi pienenisi, samoin SRAMilla näyttäisi nyt tulevan ainakin jonkinmoista rajaa vastaan pikkuhiljaa.

Joudutaan vaihtamaan SRAM paremmin skaalautuvaan tai vähemmän piipinta-alaa vievään muistityyppiin. Tämä ei ole helppo tehtävä, sillä muistin on oltava hyvin nopeaa ja kestettävä valtava määrä kirjoitus- ja lukukertoja. MRAM kai eniten on ollut esillä korvaajaksi.

Saunan kiukaita odotellessa 🙂 Tosin eipä se näin talvella haittaa. Oi niitä aikoja kun r9 290 puhisi kämpässä. Silloin ei tarvinnut palella.

Vaikka nyt ei ihan sama asia olekkaan niin Intel puihui jo 10 vuotta sitten valmistusprosessien pienentymisen ja hintojen nousemisen aiheuttavan vaikeuksia valmistaa tuotteita kannattavasti.

Mitä meinaat.. Minusta tuo käyrä näyttää siirtyvän "pysyy vakiona" tasolle, eli raja tuli vastaan.

Joudutaan tekemään isompia muutoksia, jos halutaan lisäkehitystä.

Tosin pysähtymään tuo skaalautuminen tulee jokatapauksessa. Porukan pitää alkaa opettelemään tietokoneen ohjelmointia. Nykyiset ohjelmistot ovat ihan karmeaa bloattipaskaa, jotka hukkaavat kaiken suorituskyvyn ja muistin….

Ehkä AI:t oppivat ohjelmoimaan kunnolla. Senjälkeen ihmisillä ei ole saumaa siinä kilpailussa.. Sitten ohjelmat toimivat, mutta kukaan ei tiedä miten ne tomivat..

Mielenkiintoinen kysymys vähän kauempaa että onko kyseessä valmistusmateriaalien vai menetelmien rajoite.

Vai kukaties kumpikin tai ei kumpikaan vaan jokin kvanttimekaaninen ilmiö joka on kiusannut jo edellisiäkin nodeja

Tällä on rinnakkaisuuteen sellainen merkittävä vaikutus, että käytännössä kaikki tavat lisätä rinnakkaisuutta myös vaativat enemmän muistia; Jokainen säie tarvitsee vähintään oman pinonsa, ja eri säikeet kilpailevat välimuistitilasta keskenään.

Ja jos SIMDiä levennetään ja lasketaan useampaa itsenäistä work itemia rinnakkain, käytännössä pitää myös muistin leveyttä skaalata samassa suhteessa ja efektiivinen working set kasvaa samassa suhteessa.

Eli lähestymistapa ”lisää vaan rinnakkaisuutta” alkaa tulla tämän takia kalliimmaksi. Aletaan palata siihen vanhaan, että sarjallista nopeutta halutaan saada lisää, koska sen hyödyntämiseen ei tarvitse enempää muistia. (paitsi jos sitä sarjallista nopeutta yritetään saada lisää kasvattamalla välimuisteja ja haarautumisenennustustaulukoita).

Mutta CPUIssa sitä sarjallista nopeuttakin on vaikea saada lisää. Näyttiksissä varaa vielä on.