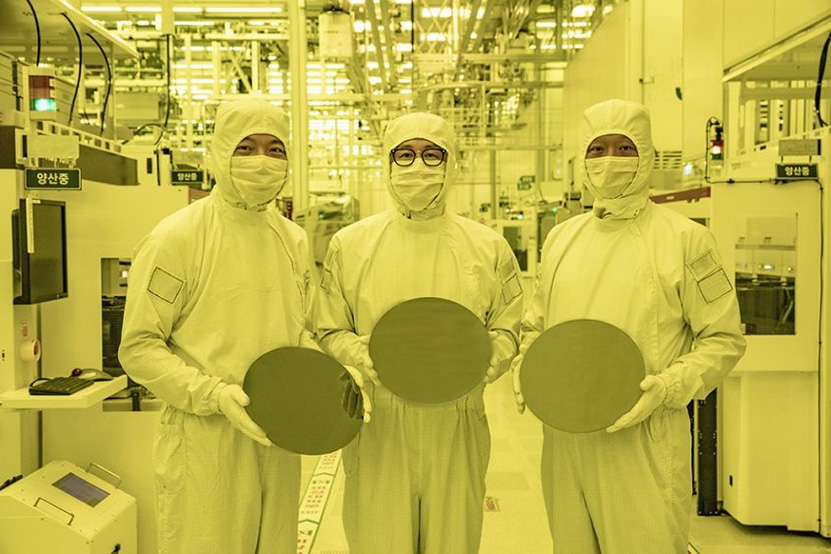

Maailman johtaviin puolijohdevalmistajiin lukeutuva Samsung on ilmoittanut merkittävästä uudesta edistysaskeleesta valmistusprosessiensa saralla. Yhtiö on aloittanut piirituotannon maailman ensimmäisellä GAA-transistoreja käyttävällä valmistusprosessilla.

Samsungin 3 nanometrin prosessi on maailman ensimmäinen GAA- eli Multi-Bridge-Channel FET (MBCFET) -tyyppisiä Gate All Around -transistoreja käyttävä valmistusprosessi. Siinä missä perinteisissä transistoreissa kanava kulkee hilan alitse, FinFET-transistorit nostivat kanavan pystyyn ikään kuin eväksi, joka läpäisee hilan. GAAFET-transistorit voivat perustua joko useaan päällekkäiseen nanokanavaan, tai kuten Samsungin uudessa prosessissa useaan päällekkäiseen, nanokanavia leveämpiin nanoliuskanaviin.

Virallisten lukujen mukaan uusi 3 nm:n prosessi lupaa tarjota 45 % pienempää tehonkulutusta, 23 % parempaa suorituskykyä ja 16 % pienempää pinta-alaa yhtiön 5 nanometrin prosessiin verrattuna. Lisäksi yhtiö kehaisee jo nyt toisen skupolven 3 nm:n prosessin parantavan lukuja vielä entisestään: 50 % pienempää tehonkulutusta, 30 % parempaa suorituskykyä ja 35 % pienempää pinta-alaa, edelleen 5 nm:iin verrattuna.

Lähde: Samsung

En itse ehkä käyttäisi planaarisista transistoreista nimeä "2D-transistori", koska sen voi sekoittaa transistoreihin, joissa kanava on grafeenin tyyppisestä 2D-materiaalista valmistettu. Niihin usein viitataan juuri "2D-transistori"-nimellä.

En ainakaan muista moisesta kuulleeni, mutra eivät siirry GAAFETteihin vielä 3nmssä, sen sijaan on kilpailuvalttina mahdollisuus tunkea samaan piiriin kolmenlaisia transistoreja, kun ennen koko piiri on pitänyt vetää samalla tyypillä

Samsungilla oli ainakin jossain vaiheessa tapana merkitä prosessinsa pykälää TSMC:tä pienemmällä numerolla vaikka tiheyttä oli vähemmän. Ja TSMC merkkaili sitten pykälää pienemmällä kuin Intel.

Parempi kuin TSMC N5P:n tiheys ainakin väitetystu

Jotain huhuja oli jossain vaiheessa alkuvuodesta, mutta kohta sen jälkeen on taas huhuiltu että N3 otetaan käyttöön aikataulusta edellä.

Lataa

semiwiki.com

Tuossa varmaan ajantasaisin ja paikkaansa pitävä tieto, eli N3 on aikataulussa.

Näkyy molemmissa

Usein uusi i5/Ryzen 5 tarjoaa samaa suorituskykyä kuin edellisen sukupolven i7/R7, mutta pienemmällä kulutuksella. Sitten se uusi i7/R7 tarjoaa reilusti enemmän suorituskykyä samalla kulutuksella

Samsungin ”5nm” prosessi on melko samaa luokkaa kuin TSMCn N6, sekä ominaisuuksiltaan että todellisilta spekseiltään.

ja tämä uusi on hurjat 16% pienempi pinta-alaltaan (tarkoittaa siis vain n. 8% pienennystä todellisisissa dimensioissa, samalla kun mainosnumero putoaa 40% omaan ja 50% kilpailijaan verrattuna)

Hienosti vaan tuntuu koko ajan kiihtyvän tämä deflaatio näissä mainosmiesnanometreissä (joilla siis ei ole yli kymmeneen vuoteen ollut MITÄÄN tekemistä minkään todellisen fysiikan nanometrien kanssa).

Uutisissa pitäisi olla melkein jotain konversiotaulukoita tai edes alustavia arvauksia, mihin kokoluokkaan tämä menee. Jos ei seuraa silmä kovana, niin ei tavallisella kuluttajalla ole mitään mahdollisuutta tietää, miten tämä vertautuu vaikka TSMC:n ja Intelin prosesseihin.

Tuossa sinun vastineesakin lukee, että korkeintaan N5:sta vastaa tämä "3nm" prosessi, mutta sitten onkin kaikki N5P:t ja 5LPE:t (ja 4LPE:t), niin suoraan sanottuna olisi parempaakin tekemistä kuin seurata markkinointimiesten liiottelua ja ylläpitää exceliä konversiokertoimista..

Sitten kannattaa varmaan alkaa seuraamaan alan julkaisuja