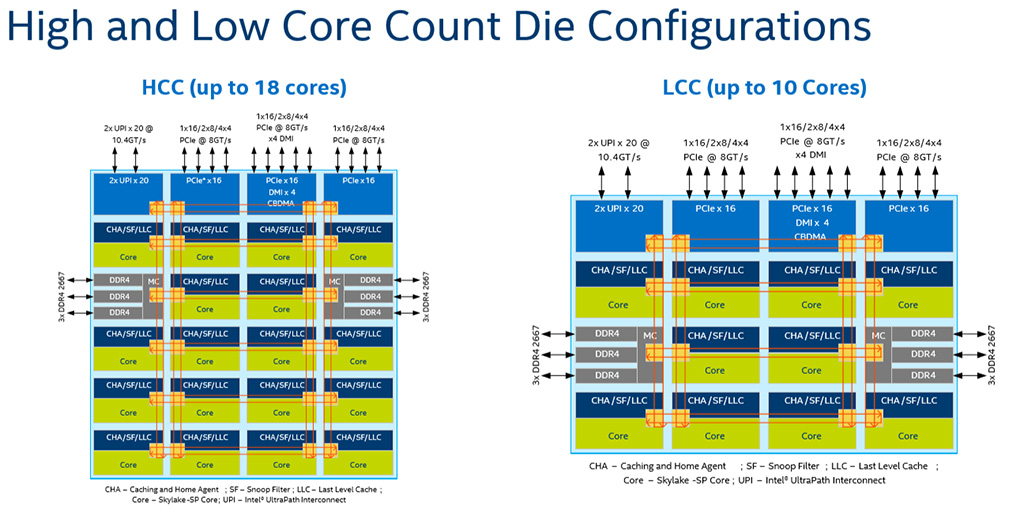

Intelin tänään julkaisema Xeon Scalable -perhe paljasti uusia yksityiskohtia Skylake-SP-arkkitehtuurista, joka tunnetaan HEDT-maailmassa nimellä Skylake-X. Skylake-X-prosessorit perustuvat Skylake-SP-arkkitehtuurin LCC- ja HCC-siruihin (Low Core Count, High Core Count).

Toisin kuin ennakkotiedoissa annettiin ymmärtää, 12-ytiminen Core i9-7920X ei perustu LCC- vaan HCC-siruun. LCC-sirussa on fyysisesti 10 ja HCC-sirussa 18 prosessoriydintä. HCC-sirun käyttö selittää samalla myös sen, miksei prosessoria julkaistu ensimmäisessä aallossa yhdessä LCC-siruun perustuvien 6 – 10-ytimisten mallien kanssa. Nykytiedon mukaan 12-ytimisen Core i9-7920X:n pitäisi tulla myyntiin elokuussa, kun muut HCC-siruun perustuvat saapuvat markkinoille vasta lokakuussa.

Skylake-X/-SP LCC- ja HCC-siruissa on todellisuudessa kuusi DDR4-muistiohjainta ja yhteensä 48 PCI Express -kaistaa. Vaikkei Intel ole vielä julkaissut HCC-ytimiin perustuvien mallien yksityiskohtia, tiedetään emolevyjen perusteella, että mallista riippumatta Intel on poistanut käytöstä kaksi DDR4-muistiohjainta ja vähintään neljä PCI Express -kaistaa. Osassa malleista PCI Express -kaistoja on käytössä vain 28.

Onkohan merkittäväkin muutos tuo HCC-siru vs. LCC?

Ei siinä muu muutu kuin piirin koko, toisessa on 10 ja toisessa 18 ydintä (ja sitä kautta tietenkin välimuistejakin on HCC:ssa enemmän, mutta saman verran per ydin), muuten ihan samat setit.

Ei ole. Ainoa merkittävä ero ytimien määrässä. Karsittuja ominaisuuksia en merkittäväksi muutokseksi laskisi.

MCC puuttuu välistä, kai sellainenkin tulee :think:

Edit: hidas.

Eivät nämäkään varmaan juotettuina tule ulos. :vihellys:

MCC:tä ei tietenkään ole tulossa, ei sellaisessa ole järkeä. HCC:ta voisi toki kutsua periaatteessa myös MCC:ksi, koska sen yläpuolelta löytyy vielä 28-ytiminen XCC eli se on pakan keskimmäinen.

14 ytimen MCC säästäisi mukavasti kun nyt joudutaan 18-ytimisestä laittamaan kolmannes ytimiä pois jotta saadaan 12-ytiminen. Hyvillä saannoilla MCC:ssa olisi järkeä.

Täysin uuden ytimen tekeminen kahden mallin vuoksi ei ole millään tasolla järkevää kun ne mallit voi tehdä siitä isommastakin ytimestä.

Onhan Intel aiemminkin tehnyt täysin eri tuotantolinjoilla työpöytäprosessoreita joiden ainoa ero on L2 välimuistin määrässä. Tuossa puhutaan hieman eri kokoluokasta kuitenkin.

En siis olisi ihan varma asiasta.

Nyt tarvitaan jo linkkiä sanojen taakse

Se oli sitä aikaa kun prosessoreista availtiin ominaisuuksia eikä nykytyyliin julkaistu tuhatta mallia vuodessa. Spekuloitiin ovatko sen ajan Celeronit vain karsittuja Pentiumeja (ainoa ero L2 välimuistissa). Intel sanoi että Celeronit tehdään täysin omalla linjallaan, joten L2 välimuistin avaamiset voi unohtaa. Mitä tuossa muutenkaan on ihmeellistä? 10 miljoonan prosessorin kohdalla tuollainen "pieni" ero tuntuu varmasti.

Takaisin nykypäivään. HCC- ja LCC- kokoero on googletuksien jälkeen luokkaa 200 mm2. Tuon luokan erolla MCC:ssa olisi paljonkin järkeä saantojen ollessa hyviä. Huonoilla saannoilla Intel saa helposti riittävästi 12-16 ytimisiä versioita ja silloin MCC:ta ei kannattaisikaan tehdä.

Edelleen sitä linkkiä kaivaten. Mendocino-Celeron oli sama kuin Dixon-Pentium2, Coppermine-Celeron sama kuin Coppermine P3 jne jne, ainut ero oli käytössä olevassa L2-cachen määrässä. Intel voi toki huudella että on eri piirejä että saa kalliimmalla myytyä niitä, mutta jos siru on fyysisesti identtinen ei se huutelu muuta mitään.

Vaikka saannot olisivat hyviä, siellä on aina viallisiakin piirejä, periaatteessahan nuo kaikki ovat jo valmiiksi "salvage partteja" koska 2 muistiohjainta ja osa PCIe-väylistä on disabloitu toisin kuin Xeoneissa. Kaikki googletukset HCC:n koosta ovat vain arvailuja, yhtä ainuttakaan ei ole korkattu vielä.

Näin isoilla piireillä saannot tuskin ovat aivan huippua ja 12c+ prossujen kysyntä lienee hintojen takia melko maltillista, joten tuskin joutuvat aivan hirveästi täysin toimivia piirejä pilkkomaan.

L2 muisti vaati aivan eritavalla pinta-alaa kuin ytimet joten eri L2 määriilä olevaa prosessoria oli järkevää tehdä mutta se että prosessori tehtäisinn 2 ydintä pienempänä ei muuta pinta-alaa niin paljon että se toisi merkittävän taloudellisen hyödyn varsinkin kun huomioidaan se että Intelillä ei ole pulaa valmistuskapasiteetista.

Eikä Intel tehnyt edes niitä eri L2-määrillä olevia piirejä, vaan disabloi esim Celeronien kohdalla osan L2:sta.

HCC- ja LCC-siruissa on ihan sama määrä L3-muistia per ydin.

http://en.wikipedia.org/wiki/List_of_Intel_Core_2_microprocessors

Jos tuohon on uskominen, niin Core 2 Duo-aikaan Intelillä oli pari erikokoista piiriä pienemmällä ja suuremmalla L2-välimuistilla. E4000-sarjan piirit 2 megan L2:lla 111 m^2 ja ja E6000-sarjan piirit 4 megan L2:lla 143 m^2. 4 megan L2:lla olleista piireistä oli ainakin olemassa myös leikattuja malleja.

Eiköhän liene ne "leikatut" olleet sellaisia, joissa osa cachesta on ollut rikki valmistuksen jäljiltä. Osa disabloitu ja myyntiin niin hävikki pienenee.

Pentium 4 Willametessa oli enemmän L2 välimuistia kuin vastaavassa Celeronissa, muuten täysin sama piiri. Northwoodissa ero oli 4-kertainen, muuten sama paitsi tietenkin joissakin Northwoodeissa oli HT. Myös Prescotteissa taisi olla sama homma. Eli sama ydin, eri L2 välimuisti, fyysisesti eri piiri. Nykyisin malleja on miljoona, joten tarvitsisi tutkia aika monta eri prosessoria jotta saisi selvän vastauksen.

Ei ole paljoa järkeä olla tekemättä MCC:ta mikäli saannot ovat hyvät. Hyvillä saanoilla (80% toimivista yksilöistä toimii kaikki 18 ydintä), huomioiden hintaeron ja kysynnän, arviolta 70-90% toimivista 18-ydin prosessoreista jouduttaisiin myymään 12- tai 14-ytimisinä. MCC:lle olisi kysyntää.

Huonoilla saannoilla vastavasti ei tarvitsisi yhtäkään 18 ytimellä toimivaa myydä muuten kuin 18-ytimisenä koska vähemmillä ytimillä toimivia tulisi sitä myöden riittävästi.

Totuus menee noiden vaihtoehtojen väliin. Erään lähteen mukaan AMD saa 80% Ryzeneistä toimimaan kaikki 8 ydintä. HCC on karkeasti 2,5 kertaa Ryzeniä suurempi, eli Intelin vastaava lukema 18 ytimelle voi olla aika pieni ja siksi MCC:ta ei tarvita. Karkeasti 150 mm2 haaskaus ei ole hirveästi mutta selvästi enemmän se maksaa kuin juotettu heatspreader.

Noihin erillisiin tuotantolinjoihin liittyen, tästä löytyy hyvä taulukko Intel® Xeon® Processor E7 v4 Family Product Specifications

Päästään hyvään kysymykseen, monellako tuotantolinjalla noita prosessoreita tehdään. Teoriassa niitä voisi tehdä vain yhdellä, jossa tehdään 24 ydintä 60 megan L3 versiota. Tarkoittaisi että joistakin prosessoreista heitetään pois 20 ydintä ja toisesta 40 megatavua L3 välimuistia. Tai 4-ytiminen tehdään 10-ytimisestä karsimalla jolloin otettaisiin pois 6 ydintä.

18 ytimestä kolmannes pois vastaa noin 150 mm2 pinta-alaa. Iso kulu verrattuna tahnalla saavutettuun säästöön.

Lisätään tämä Core 2 listaan Pentium 4:n kanssa.

No niin, linkkiä sentään tuli. Pienellä kaivelulla die shotteja löytyy vain yhdenlaisista Conroeista, Wolfdaleista jne. Myös delidatut prosessorikuvat viittaavat samaan, identtisiä vaikka L2-muistia eri määrät. Eli epäilisin Intelin ARK:in (josta Wikin luvut ovat peräisin) listaavan piisirun käytössä olevan pinta-alan koko piirin pinta-alan sijasta.

esim:

E4300, 2MB L2: https://i.ytimg.com/vi/1IYMtFA-MGQ/maxresdefault.jpg

E4600, 4MB L2:

Kovin samankokoisilta ainakin noin silmämääräisesti näyttävät?

Mainitsemasi piirit ovat jälleen täysin identtisiä, käytössä olevan L2-välimuistin määrässä on eroa, ei piirissä fyysisesti.

Intelin mukaan Broadwell-EP-sarjassa on kolme eri piiriä, aivan kuten Skylake-SP:ssä. Mutta jaottelu prosessorimallien kesken ei ole edes aina niin yksinkertainen kuin voisi kuvitella, sieltä löytyy esimerkiksi kaksi kellotaajuuksia ja TDP:tä lukuunottamatta identtistä prosessoria, jotka perustuvat Intelin mukaan eri piireihin.

Dieshottien löytäminen prosessoreista on todella vaikeaa, joten tämän offtopicin voi tosiaan jättää tähän.

atkaisen kuva-arvoituksen vielä lopuksi:

Intel® Core™2 Duo Processor E4300 (2M Cache, 1.80 GHz, 800 MHz FSB) Product Specifications

Intel® Core™2 Duo Processor E4600 (2M Cache, 2.40 GHz, 800 MHz FSB) Product Specifications

Toisaalta, vaikka näin olisikin, niin sen HCC-lastun valmistaminen ei noilla korkeilla saannoilla maksaisi "juuri mitään". Se säästö jäisi silti melko pieneksi, koska se kallein valmistusvaihe, siis suunnittelu, ei muuttuisi yhtään edullisemmaksi noilla pienillä valmistuskulusäästöillä.

Pahimmillaan tuo voisi jopa tulla kalliimmaksi, jos vaikka pitäisi nopeasti nostaa keskimääräistä myytyjen prosessorien tehoa. Niitä täysin toimivia, mutta tehdasrampautettuja prosessoreita voi vaan jättää rampauttamatta, jos markkinatilanne vaatii. Hypoteettisesta MCC-lastusta ei sen sijaan saa hyvää 18-ytimistä tekemälläkään.

Tämä voi kieltämättä olla totta, jos Intelin valmistusprosessi ei ole huomattavasti parempi.

Jos Ryzen on sen 200 mm² *, ja niistä 80 % on virheettömiä, niin tuosta voi suoraan arvioida mikä olisi tuolla prosessilla valmistettujen suurempien piirien saanto – karkeasti tosin.

LCC Skylake-X on noin 300 mm² **, jolloin saanto olisi noin 0.8^(300/200), eli reilut 70 %.

HCC ehkä noin 18/10 × 300 mm² = 540 mm², joita puolestaan saisi sen joku 55 %.

Hypoteettinen MCC piiri olisi joku 14/10 × 300 mm² = 420 mm², ja sen saanto olisi reilut 60 %. Ei mitenkään hirveästi enempää. Ja, siis tuo 55 % noista HCC piireistä olisi ns. täydellisiä 18-ytimisiä piirejä, noita 14 ytimisiä piirejä niistä olisi selvästi enemmän kuin 55 %… Kyllä noilla luvuilla joutuu myös niistä ihan toimivista piireistä tekemään niitä 12–16 ytimisiä.

Ei ehkä kannata siis tehdä enempää eri kokoisia piirejä, minkä Intel varmaan myös itse on laskenut – hieman paremmilla lähtöarvoilla. Nämä luvut siis erittäin karkeita, ja tekevät aika isoja oletuksia valmistusprosessien laaduista.

* Ryzen 7 1800X – AMD – WikiChip

** http://www.gamersnexus.net/news-pc/2943-intel-i9-7900x-die-size-cpu-size

Pikaisella laskemisella, tuo 150mm2 säästö toisi rahallista säästöä karkeasti 6 dollaria per prosessori. Paljon vai vähän, riippuu saannoista. Noilla lasketuilla saannoilla saadaan riittävästi >18 ytimisiä eikä läheskään kaikkia täysin toimivia tarvitse rampauttaa. Mikäli saannot olisivat selvästi korkeammat, miljoonan prosessorin tapauksessa tulisi säästöä 6 miljoonaa. Sillä pitäisi peittää helposti suunnittelukulut.

Kovimmat mallit ovat poikkeuksetta niin kalliita ettei tarvitse miettiä rampauttamatta jättämistä vaan sitä paljonko tarvitsee rampauttaa.

Intel on tietyllä tavalla paljon vähemmän ketterä (ja toisaalta selvästi rikkaampi) firma kuin AMD, joten voivat päättää rampautuksen olevan ratkaisu jota käytetään aina, kustannuksista riippumatta.

6 miljoonaa ei riitä edes etäisesti uuden piirin suunniteluun ja validointiin vaikka arkkitehtuuri itsessään olisi jo valmis. Lainaten luotettavana pitämääni lähdettä koko prosessissa pyöritään 100 miljoonan kieppeillä.

Juu prosessorien "tinttaaminen" sille piikiekolle on järjettömän halpaa verrattuna niiden kehityskuluihin, minkään muun tuotten valmistuksessa suunnittelu/kehitys kulujen ja valmistuskulujen välillä ei ole niin valtavaa eroa.

Myös prosessorien juottamisessa käytetyt materiaalit verratuna prosessorin pinta-alan aiheuttamiin valmistuskustanuksiin on aivan eri suhteessa kuin porukat näyttää kuvittelevan joten Intelille on halvempaa kasvatta prosessorin pinta-alaa kuin siirtyä heatspreaderin purkasta juottamiseen.

Joo, itse prosessorien valottaminen on kyllä halpaa, mutta piirin suunnittelu ja valottamiseen käytetyt välineet/tilat maksaakin sitten maltaita. Siinä saa aika monta prosessoria myydä että joku 10Mrd USD FAB on kuoletettu. Valotusmaskitkaan ei taida olla ihan halpoja.

Ei, myös E4600:ssa on vain 2 MB L2: Intel® Core™2 Duo Processor E4600 (2M Cache, 2.40 GHz, 800 MHz FSB) Product Specifications

Eli molemmat kuvat esittävät samaa fyysisesti 2 MB:n L2-välimuistilla olevaa ydintä (stepping L2 & M0*, epävirallisesti Allendale). Varsinainen Conroe (stepping B1, B2 & G0*) jonkin verran pitkulaisempi:

Intel IHS Lapping and Removal For LGA775 CPU's – Page 2 of 2 – Legit Reviews

Hyllyssä sattuu olemaan E6300 SL9SA (B2) ja E2160 SLA3H (L2), joten tarvittaessa voisin näyttää niille vielä kuumailmapuhallinta ja ruuvipenkkiä.

*) http://download.intel.com/design/processor/specupdt/313279.pdf

Olet oikeassa, luin väärältä riviltä näemmä tuon L2:n, sehän löytyy 6600:sta, ei 4600:sta.

Tuo Allendale-coren käyttö selittää myös miksei piirin ulkonäkö vastannut dieshotteja :beye:

Ja näköjään Conroe ja 45 nm Wolfdale melko saman mallisia, niin menin itsekin vähän sekaisin: http://www.chip-architect.com/news/Brisbane_Conroe_Penryn_compare_2007_01_27.jpg

Eikö me voitaisi pitää nämä muinaismuistoprosessoreista jauhamiset jossain historia-triideissä ja keskittyä siihen uutisen prosessoriin?

Lähtökohtaisesti voimme myös olettaa, että valmistaja on AINA ennen julkaisua miettinyt sitä, että montako eri kokoista ydintä kannatta suunnitella ja miten SKU:t kannattaa jakaa. Markkinoiden segmentointi on paljon tutkittu asia ja isojen firmojen markkinointiosastot tuottavat dataa siitä, että mitä kannattaa tarjota ja mihin hintaan…

Joo mulla taas oli piste pilkun kohdalla. Tarkoitin siis, että niistä joissa cache ollut viallista, on valmistusteknisesti jotenkin leikattu (ts. configuroitu) blokkeja pois cachesta jossa on vikaa ja myyty "vajailla" spekseillä kun piiri ei toimi kokonaan, mutta osittain toimivana voidaan myydä.

Tämä. Tällä kertaa tämä myös näkyy mielestäni hyvin konkreettisella tavalla, siis ihan noita ydinmääriä katsomalla. 10, 18 tai 28, yksikään näistä ei ole ns. klassinen kaunis ydinmäärä (lue: kakkosen potenssi). Ei liene ihan sattumaa, että tuo suurin on juuri 28, eikä vaikka 26, 30 tai 32. Tai, miksi ei tehty 8- ja 16-ytimisiä vaan 10 ja 18.

Ei tuo välttämättä poikkea mitenkään klassisesta 8:lla jaollisesta sarjasta 8, 16, noissa pienemmissä kun jos Intel on suunnitelut että 8 +2 varalla rikkinäisten ytimien vuoksi ja 16 +2 varalla rikkinäisten ytimien vuoksi ja tuo 28 voi olla aivanhyvin suunniteltu tyyliin 24 + 4 varalla rikkinäisten ytimien vuoksi eli ainut mitä Intel ei olisi suunnitellut on se että heidän tuotantonsa tuottaa parempilaatuisia prosessoreja kuin olettivat ja siten on paljon prosessoreja joissa ne kaikki ytimet toimivat vaikka pääosan/kaikkien prosessorien oletettiin olevan osittain rikki 😀

Intel Xeon Scalable Processors sarjaan on julkistettu tai tullaan julkaisemaan prosessoreita seuraavilla ydinmäärillä: 4, 6, 8, 10, 12, 14, 16, 18, 20, 22, 24, 26 ja 28 :smoke:

Lähde Intel® Xeon® Scalable Processors Product Specifications

Eli tämä vain korostaa sitä että siinä tehtaassa ei kannata olla tuotantokatkoja kun jos tehdään useita rinnakkaisia prossesorimalleja joissa on vain pieniä eroja ydin määrässä ja välimuistin koossa niin aina kun tuotannossa vaihdetaan prosessorista toiseen tulee tuotantokatko kun systeemejä pitää säätää että linjanpäästä alkaa tulla toimivia prosssoreja, eli optimitilanne on se että tehdaspaahtaa 100% teholla 24/7 yhtä ja samaa perustuotetta.

Tämä muuten selitää sen miksi on näitä saatavuus ongelmia näytönohjaimissa kun ei ole tehdasta joka tekisi jatkuvasti jotain tiettyä näytönohjainpiiriä vaan sekä Nvidia että AMD tilaa GPU:idensa tuotantoeriä fabeilta ja sitten myy niitä valmiita näytönohjainpiirejä varastosta ja kun menekki on arvioitu väärin pitää fabilta tilata uusi tuotantoerä jonka se fab valmistaa sitten kun vapautuuu jo jonossa olevista tilauksista eli pahastiväärinarvioitu kysyntä aiheutaa kuukausien katkon ennen kuin saadaan uusi erä myyntikuntoon.

Eli johonkin tällaiseen mainauspiikkiin näytönohjainpiiirien valmistajat ei voi mitenkään reagoida ja ne mainauskortit joita tulee myyntii on suoraan pois normaalinäyttisten GPU varastosta.

Just joo.. <sarkasmidetektori takasin päälle, hölmö aikakatkaisu>

Mikäköhän edes lienee tuossa 28-ytimisessä se asettelu, 4 × 7, mutta mitä ydinyhdistelmiä voi kytkeä pois päältä. Intel ei taida hirveämmin olla huudellut, että miten nuo isommat lastut edes tuossa suhteessa toimii.

En tainnut ehkä tarkoittaa, että mitkä on ne tuotteet mitä niistä kolmesta lastusta saa aikaan. Samoin niistä on myös "hieman" eri kellotaajuuksia, ja muitakin ominaisuuksia taitaa saada hienosäädettyä tuotesegmentoinnin nimissä.

Intel on valinnut kolme lastun kokoa, joka ratkaisee esim. saannot, ja sen kuinka paljon niistä enintään saa sitä laskentatehoa irti. Pienempiä malleja saa "saksilla", mutta

Siis, toki kaikkia noita pienempiä ydinmääriä saa isommista kunhan vaan "saksii" hieman, mutta tuon lastun koko on se, mikä ratkaisee esimerkiksi saannot.

Kyllä. Yksi tuote lisää valikoimaan, ja sitten sinulla on yksi tuote lisää varastosaldoissa. Se ei esim. varmaan yhtään Intelillä haittaisi, vaikka kaikki HCC-lastut toimisi kaikilla 18-ytimellä ja nätisti noilla nopeimman mallin maksimikelloilla. Eipähän tarvitsisi montaa eri varastotuotetta pitää, kunhan vaan juuri ennen paketointia ajaa kuhunkin prossuista ne lopulliset kertoimet ja käytössä olevat ytimet siihen mikrokoodiin ja polttaa sen uudelleenohjelmointisulakkeen..

Itseasiassa on kertonut hyvin tarkkaan. XCC:ssä eli 28-ytimisessä asettelu on 6×6. Ylin rivi on "uncorea" eli PCIe-väylät sun muut sellaiset, sitten tulee yksi kuuden rivi ytimiä välimuisteineen, seuraavalla rivillä muistiohjaimia (3 yhdessä ryppäässä), 4 ydintä välimuisteineen ja lisää muistiohjaimia (taas 3 yhdessä ryppäässä) ja sitten kolme kuuden riviä ytimiä välimuisteineen.

Tai sama kuvana:

![[IMG]](http://images.anandtech.com/doci/11544/xcc28cores.png)

Näkee, että ei enää seuraa liian aktiivisesti, kun tämä oli kokonaan mennyt ohitse itseltä. Tuo saattaa myös osaltaan selittää noita ns. outoja ydinmääriä.

Onko noista ydin–ydin-latenseista tietoa, että onko tuossa verkossa eri latenssi, jos joutuu käyttämään sekä noita "riveillä" että "sarakkeilla" olevia yhteyksiä. (Tai siis, onko esim. tuossa 12 ydintä, joilla on muita aavistuksen nopeampi reitti keskusmuistiin – siis ainakin latenssin osalta. Ja sitten sama toki ydin–ydin-viestinnän suhteen. (Koska jos tällaisia eroja on, niin ne voisivat osaltaan selittää niitä ei-Skylake-X-optimoitujen ohjelmien omituisia hidastumisia verrattuna edellisen sukupolven prossuihin. Toki, myös sen välimuistin määrä, ja siten myös sen sisäiset latenssit varmaan näyttelevät omaa osaansa.)

Ainakin pienemmillä ytimillä ajettujen testien perusteella siellä on jonkinsortin latenssintasaukset käytössä

Tuota tuo kaaviokuva on hyvinsiisti jossa kaikki ytimet, uncore, ym on mukavassa ruutukaavassa mutta kun niitä prosessoreja nykyään suunnitellaan tekoälysysteemeillä jotka optimoi sen prosessorin fyysistä rakenneta hyvinkin "luovasti" niin ne todelliset fyysiset prosessorit ei ole enää toteutukseltaan kaunista ruutukaavaa niin kuin ihmisten suunnittelemat prosessorit oli vanhoina hyvinä aikoina.

Eli en usko että se Intelin todellinen fyysinen prosessori näyttäisi tuollaiselta kauniilta ruutukaavalta.

Teoriassa mesh:ssä latenssi on suoraan verrannollinen sen suhteen montako hoppia reitillä tarvii mennä, eli suunnalla ei ole väliä mennäänkö ylös vai alas tai niiden yhdistelmänä, vain reitittimien määrä.

Teoria voi olla ihan toista. Mitä jos coret 1 ja 3 haluavat dataa coren 2:n viereisestä L3:sta?

-Saako molemmat datan samaan aikaan?

-Tuleeko jono ja esim randomilla toista palvellaan ekana?

-Tuleeko collision ja molemmat saa virheen ja tehdäänkö retry jollain logiikalla vai randomilla? (randomikin hyvin luultavasti osuu eri ajastukseen)

Muistiohjainten kanssa sitten homma on jo hankalampi, jos välissä on useita hoppeja, kulkeeko data hopilta hopille, vai säilötäänkö ensin L3:seen siltä varalta että tulee taas collision, koska jos retry tulee kovin kaukaa se maksaa lisää aikaa. =)

Erittäin vaikea testata, jostain Intelin dokumentaatiosta melkein pitäisi osata lukea se. Ehkä nuo hkultala / the stilt joskus avaa. En itse viitsi ruveta perehtymään kun ei välttämättä ymmärrys riitä, en ihan noin matalan tason juttuja ole opiskellut/ymmärrä, toisin kuin nuo herrat. 🙂

Siinä sitten dieshottia HCC-versiosta, kelpaako nyt? Kyllä se on siisti ruutukaava. (kuva 90 astetta eri kulmassa kuin nuo kaaviot mutta se ei muuta mitään)

katso liitettä 29535

edit: se mitä näet "fraktaalisena rakenteena" näyttää siltä vain koska et hahmota sitä kokonaisuutta.

edit2: ja se myönnettäköön että onhan tuossakin dieshotissa ylä- ja alareunoissa juttuja mitä ei "pitäisi olla" sen kaavion mukaan siellä, mutta muutoin hyvin 1:1 kaavion kanssa

edit3: oisko ne DDR4-muistiohjaimen linkit siinä ylhäällä ja alhaalla, itse MC siellä missä pitääkin ja selvästi erottuu ne kolme kanavaa, myös reunalla toistuu kolme rakennetta

Symmetria on paitsi kaunista, myös toimivaa piirisuunnittelussa. Näin oli ennen muinoin ja todennäköisesti on jatkossakin.

Alla 28 ytiminen Skylake

katso liitettä 29538