NVIDIA on julkaissut Turing-arkkitehtuuristaan grafiikkapiirejä sekä RT- ja tensoriytimillä varustettuna että ilman niitä. Keskusteluissa onkin spekuloitu paljon sitä, kuinka paljon RT- (Ray tracing) ja tensoriytimet todellisuudessa vaikuttavat grafiikkapiirin kokoon.

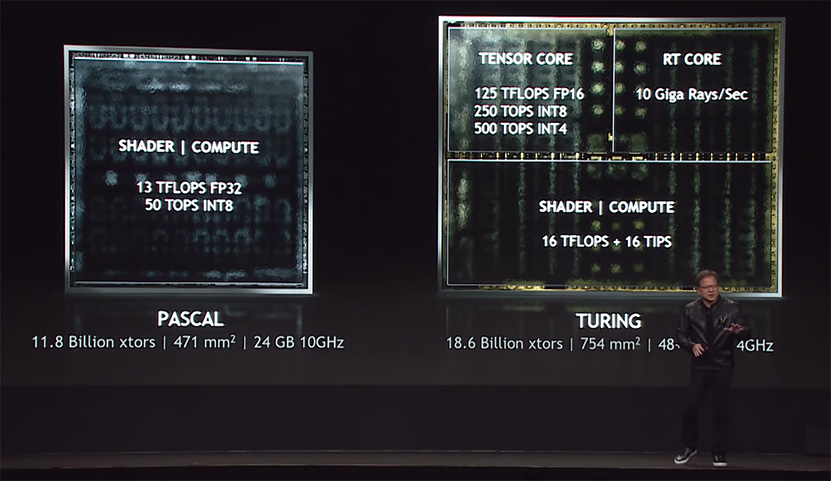

NVIDIA esitteli Turing-arkkitehtuurin julkaisun yhteydessä kuvaa, jossa huippupiiri TU102 oli jaoteltu tensoriytimiin, RT-ytimiin ja CUDA-ytimiin. Kuvan mukaan RT- ja tensoriytimet veisivät kumpikin neljänneksen alasta, kun CUDA-ytimet veisivät puolet piirin alasta. Sanomattakin on selvää, että kyseessä oli fiktiivinen jaottelu, eikä piiriä ole jaettu kuvan kaltaisiin osiin millään tasolla, vaan RT- ja tensoriytimet ovat integroitu tiiviisti CUDA-ytimet sisältäviin TPC- (Thread Processing Cluster) ja SM-yksiköihin (Streaming Multiprocessor).

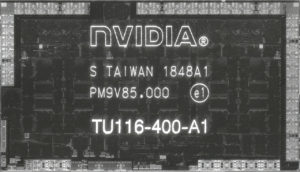

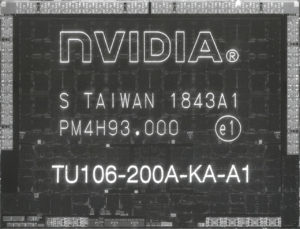

Kun Turing-arkkitehtuurista julkaistiin ensimmäiset versiot ilman edellä mainittuja ytimiä, heräsi keskustelu uudelleen niiden vaatimasta pinta-alasta. Jonkinmoista selvyyttä tilanteeseen saatiin lopulta piirien valokuvauksesta tutun Fritzchens Fritzin julkaisemien TU106- ja TU116-grafiikkapiirien infrapunakuvien myötä.

Redditissä nimimerkillä Qesa tunnettu käyttäjä otti asiakseen selvittää, kuinka paljon RT- ja tensoriytimet todella vievät tilaa kyseisten kuvien pohjalta. Qesan laskelmien mukaan yksi TPC-yksikkö, joka sisältää kaksi SM-yksikköä ja RT-ydintä sekä joukon tensoriytimiä vie TU106-grafiikkapiirillä tilaa 10,89 mm2. Vastaava TPC-yksikkö TU116-grafiikkapiirillä, jossa ei ole lainkaan RT-ytimiä ja tensoriytimet on korvattu FP16-CUDA-ytimillä, vie puolestaan tilaa 8,94 mm2, mikä tarkoittaisi 1,95 mm2 eroa. Qesan arvion mukaan tensoriytimet vievät piiriltä tilaa noin 1,25 mm2 enemmän kuin FP16-ytimet, kun RT-ytimet vaatisivat tilaa noin 0,7 mm2. Koska tensoriytimet on integroitu niin tiukasti CUDA-ydinten rinnalle SM-yksikössä, sisältää niiden vaikutus TPC:n kokomuutokseen myös mahdolliset vaaditut muutokset muihin TPC:n osiin kuten välimuisteihin ja tehtävien vuorottajaan (scheduler).

Lyhyemmin ilmaistuna FP16-ydinten vaihtaminen RT- ja tensoriytimiin kasvattaisi kunkin TPC-yksikön kokoa hieman alle 22 prosenttia. Karkean laskukaavan mukaan TU116:n tapaan FP16-ytimillä varustetun TU102:n pinta-ala kutistuisi 754 mm2:sta 684 mm2:een, TU104:n 545 mm2:sta 498 mm2:een ja TU106:n 445 mm2:sta 410 mm2:een. Kuten luvuista näkee, olisivat kyseiset grafiikkapiirit erittäin kookkaita myös ilman tensori- ja RT-ytimiä. Uutisessa käytetyt lukemat ovat valistuneita arvioita saatavilla olevasta materiaalista, eikä tarkkoja lukuja saada luultavasti ikinä tietää, ellei NVIDIA niitä erikseen lähde paljastamaan.

Lähde: Reddit, Fritzchens Fritz @ Flickr

TPC yksiköstä noin 20%, mutta koko piiristä vain 10%. Eli ei mitenkään merkittävästi. Olisivat voineet laittaa niitä tuplamäärän, mutta rahastavat mieluummin.

Eli kun katsoo mitenkä RT tai Tensori ytimistä on hyötyä peleissä ja kun ottaa huomioon sen että RT ytimet vaatii tilaa aika vähän mutta Tensori ytimet paljon niin jos minä saisi valita niin ottaisin sellaisen Nvidia GPU:n pelikäyttöön jossa olisi ne RT ytimet mutta Tensori ytimiiä ei olisi vaan se tila olisi käytetty normaaleille Cuda ytimille.

Aika hyvin menee yksiin sen kanssa, mitä tänne aiemmin laskeskelin Voltan ja Turingin tietoihin perustuen.

Onko noi tensoriytimet vain DLSSn takia?

Must ne voisi jättää silloin kyllä pois tykkänään.

Niillä tehdään myös AI/ML-laskentaa. Kaikki ei käytä noita kortteja pelaamiseen..

Minä taas en tee RT-yksiköillä mitään, mutta Tensor-yksiköt tulisivat tarpeeseen.

Eikös niitä käytetty myös säteenseurannan kanssa kohinan poistoon?

Teoriassa, mutta käytännössä ainakin Battlefield ja Metro käyttävät TAA:ta tohinanpoistoon. Unreal Enginestä ja Tomb Raiderista en tiedä.

Olen vähän samoilla linjoilla, tosin painottaisin näitä vähän eri tavalla. Oma toivomukseni Nvidian suuntaan olisi, että 7nm piirisukupolvessa tensorit heitettäisiin mäkeen, ja RT-suorituskyky nostettaisiin vähintään kolmin- tai nelinkertaiseksi. Sen jälkeen niin paljon "perinteistä" cuda-tehoa, kuin jäljelle jäävään pinta-alaan mahtuu.

Olin alkuvaiheessa hyvinkin innostunut noista tensoriytimistä, mutta nyt näyttää siltä ettei niille ole tulossa mitään käyttöä sen paremmin hyötyohjelmissa kuin peleissäkään.

TAA on antialiasing tekniikka ei sillä ole mitään tekemistä kohinan poistossa.

Tensorcoret eivät ole aktiivisia rendauksessa kun DXR:ää käytetään. Kohina poistetaan tn. ihan mixed precision laskuilla, missä Turing on myös hyvä. DXR:n kuitenkin pitäisi toimia kaikilla näytönohjain valmistajilla, joten jos tuo kohinan poisto onnistuisi vain tensoreilla ei sillä juuri olisi tulevaisuutta.

No peleistä en tiedä mutta kyllä sille hyötyohjelmissa käyttöä löytyy.

Nvidian teknologiademot ja tutkimusprojektit eivät nyt ole ihan sitä, mitä hyötyohjelmalla tarkoitin. Kaipaisin jotakin vähän konkreettisempaa, vaikkapa videotoistimen, joka nostaa AI-superresoluutiotekniikkaa hyödyntämällä videon resoluutiota reaaliajassa 1080p -> 4k. Mikään DLSS-tasoinen blurrifiltteri ei kelpaa, vaan kuvanlaadun pitäisi oikeasti olla niin hyvä, että sitä olisi lähes mahdotonta erottaa aidosta 4k:sta.

Yksittäisiä (valo)kuvia editoitaessa tensoreita ei käsittääkseni tarvita, ja laskenta (esim. tuo AI InPainting) voidaan tehdä tarpeeksi nopeasti myös tavallisilla cuda-ytimillä tai jopa CPU:lla.

Tuossa artikkelissa mainitaan TAA denoising useamman kerran:

Tech Interview: Metro Exodus, ray tracing and the 4A Engine's open world upgrades • Eurogamer.net

Battlefield:

Ainakin Frostbitessä (BF5), SEEDissä (Pica Pica demo) ja Metrossa häiriönpoistossa hyödynnetään nimenomaan TAA:ta

Tensoreita voidaan käyttää kohinanpoistoon (NVIDIA OptiX AI), mutta mitenkään välttämätöntä se ei ole.

Samoin tuo resoluutio upskaalaus videoissa(madVR). Tarkoitin tuolla nyt lähinnä että tarjoavat SDK:ta halukkaille.

Jotenkin mennyt tuo TAAn käyttö kohinan poistossa täysin ohi. Mutta jooh ei se ainoa kohinan poistaja kuitenkaan ole(Eurogamer haastattelusta poimittuna):