AMD piti aiemmin tällä viikolla Financial Analyst Day 2020 -tapahtuman, jossa se kertoi yhtiön lähitulevaisuuden suunnitelmista. Jo uutisoitujen näytönohjainrintaman kuulumisten lisäksi AMD kertoi tapahtumassa muun muassa prosessoreiden lähitulevaisuudesta ja paketointiteknologioista.

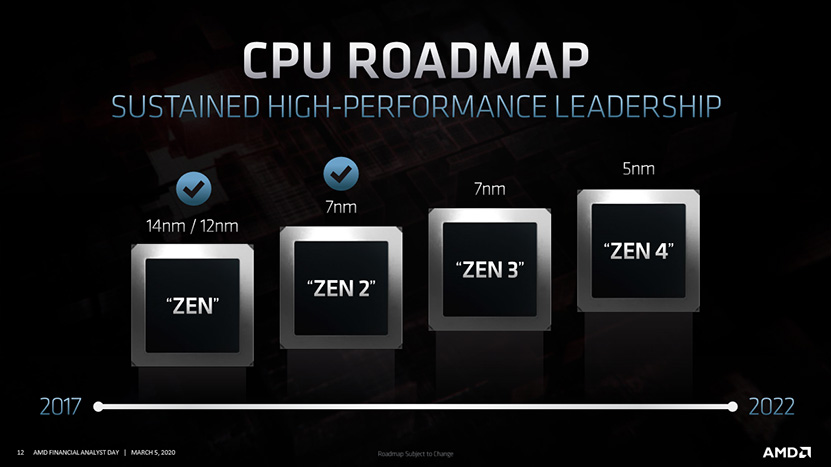

Prosessoripuolella AMD julkaisi uuden suurpiirteisen arkkitehtuuri-roadmapin, joka sisältää nyt neljä Zen-sukupolvea ja aikajanan vuodesta 2017 vuoteen 2020, mutta tarkkoja tulkintoja arkkitehtuurien julkaisuajankohdista siitä ei voi vetää. Joukon tuorein tulokas, Zen 4, tullaan valmistamaan 5 nanometrin valmistusprosessilla. Roadmapin Epyc-versiossa ei ollut varsinaisesti uutta tietoa, sillä AMD on jo aiemmin varmistanut Zen 3 Epycin olevan Milan ja Zen 4 Epycin Genoa.

Näytönohjaindiojen tapaan AMD on poistanut ”7nm+” merkinnän ja korvannut sen pelkällä ”7nm”:llä. AnandTechin saaman vastauksen mukaan merkintä poistettiin, koska se yhdistettiin liian yleisesti TSMC:n N7+ EUV -prosessiin, vaikka sen oli tarkoitus esittää vain parempaa 7 nanometrin prosessia. AMD ei tässä vaiheessa paljasta, millä prosessilla esimerkiksi Zen 3 -prosessorit tullaan valmistamaan. Yhtiön nykyisistä tuotteista ainakin Navi 10 -grafiikkapiirit on valmistettu 2. sukupolven 7 nanometrin eli N7P-prosessilla.

Kuluttajapuolella prosessori-roadmap ei ole päivittynyt vielä yhtä pitkälle, kuin Epyc-puolella. Prosessori-roadmapin aikajana yltää vuoteen 2021 asti, jolloin julkaistaan Zen 3 -arkkitehtuuriin perustuvat Vermeer-koodinimelliset 4. sukupolven Ryzen-prosessorit. Vermeer-koodinimelliset Zen 3 -prosessorit tullaan valmistamaan tarkemmin määrittelemättömällä 7 nanometrin valmistusprosessilla.

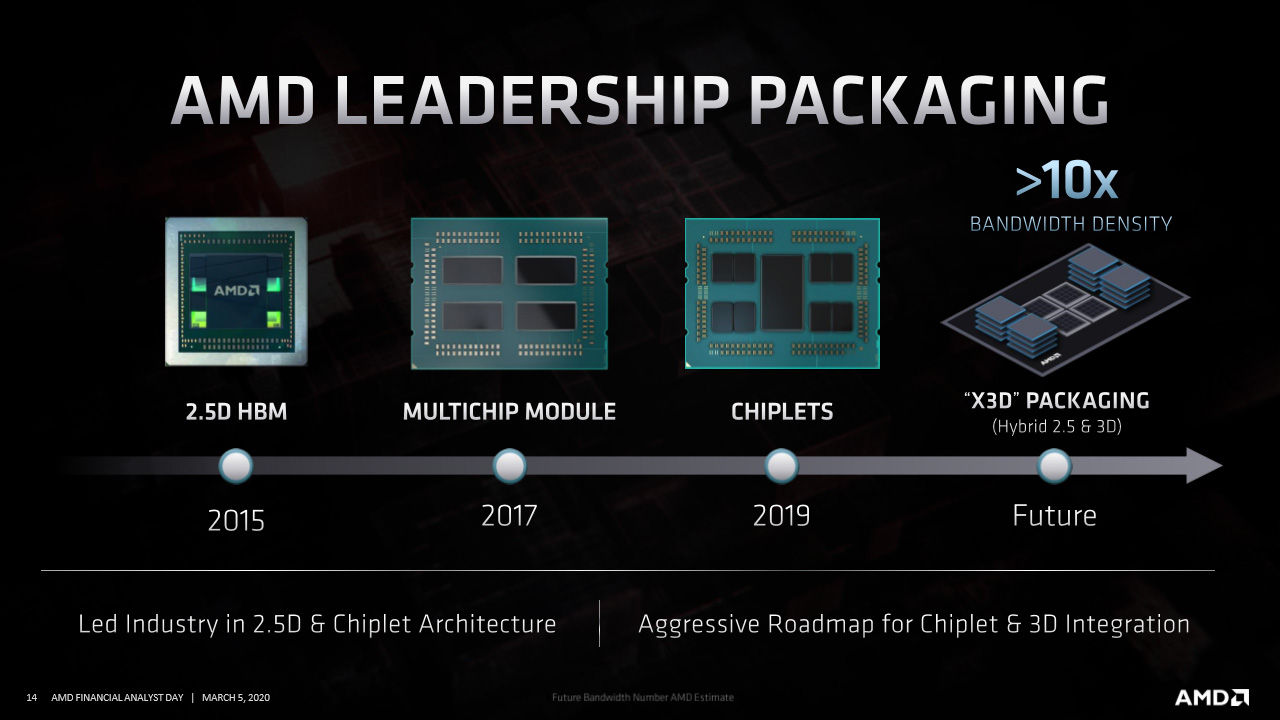

Paketointipuolella AMD:n tulevaisuudensuunnitelmiin kuuluu ainakin X3D:ksi toistaiseksi ristitty teknologia, joka yhdistää 2,5D- ja 3D-teknologiat yhteen paketointiin. Esimerkkikuvassa yhden interposerin päällä on neljä sirua sekä neljä muistipinoa ja sen luvataan mahdollistavan yli kymmenkertaisen kaistan perinteiseen paketointiin nähden samassa tilassa. AMD ei vielä paljastanut edes summittaista aikataulua X3D-paketoinnin käyttöönotolle, vaan totesi sen yksinkertaisesti olevan tulossa käyttöön tulevaisuudessa.

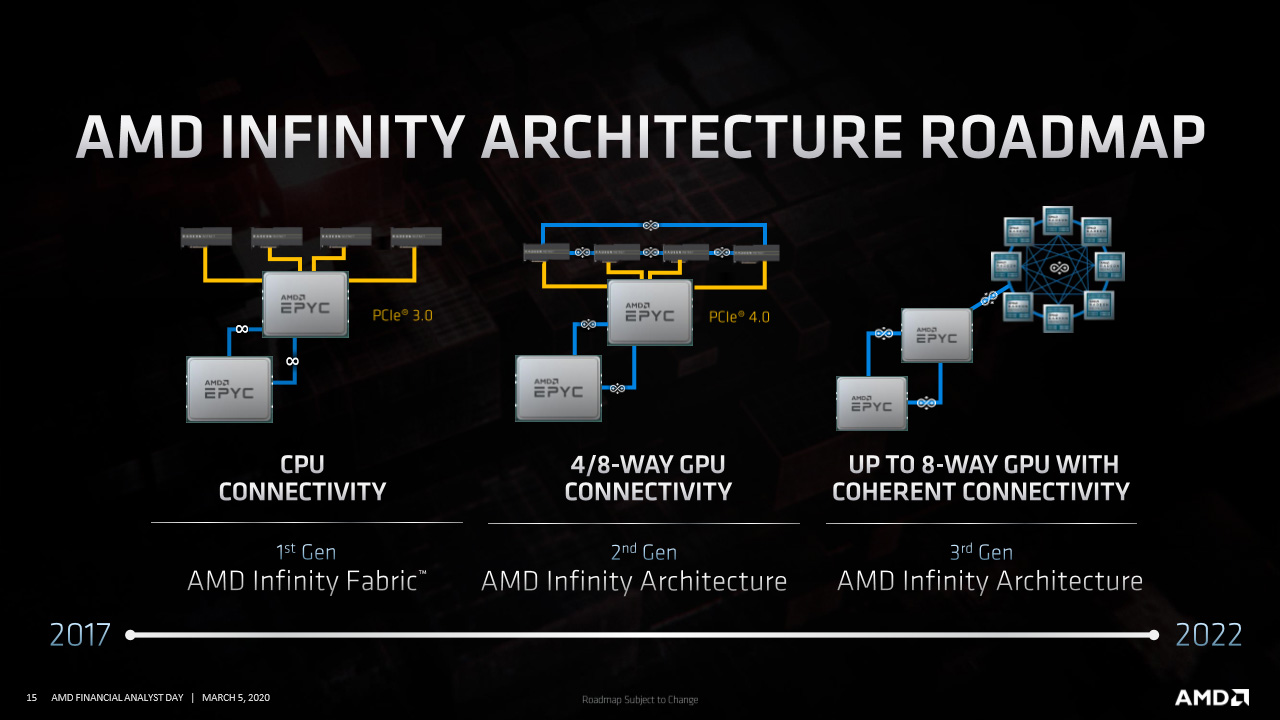

Väyläteknologioissa AMD on ristinnyt Infinity Fabric -väylän yleisesti Infinity-arkkitehtuuriksi. Nykyisellään Infinity-arkkitehtuurin ensimmäisessä sukupolvessa prosessoreiden välillä on IF-linkki, mutta laskentakorteille kommunikoidaan PCIe 3.0 -väyliä pitkin. Toisen sukupolven Infinity-arkkitehtuurilla prosessori ja laskentakortit keskustelevat PCIe 4.0 -väylää pitkin ja laskentakortit keskenään IF-linkkejä pitkin. Kolmannen sukupolven Infinity-arkkitehtuurissa myös prosessoreiden ja laskentakorttien välinen linkki päivittyy IF-aikaan, mikä nostaa väylän nopeuden yli kaksinkertaiseksi ja mahdollistaa koherentin muistiavaruuden prosessoreiden ja laskentakorttien välille. 3. sukupolven Infinity-arkkitehtuuria tullaan käyttämään ainakin El Capitan -supertietokoneessa siten, että kukin Epyc-prosessori on kytköksissä neljään laskentakorttiin, vaikka väylä mahdollistaisi useammankin.

Toivotaan että pystyvät parantamaan hieman suorituskkykyä koko ajan ja samalla kehittää sen ohella seuravan sukupolven ratkaisua ettei jäädä odottamaan niin kuin intelin tapauksessa.

Uutta zeniähän pitäisi roadmapin mukaan pukata jo tämän vuoden aikana 😛 Nyt olisi hyvä sauma päästä intelistä ohi pelikäytössäkin, kun työpöydällä Ryzen 9 moppaa Intelin hintatasossa ja suorituskyvyssä mennen tullen.

Tuli vuoden vaihteessa päivitettyä sandy bridgestä (i7 2600 quadi) lähemmäs nykyaikaa Ryzen 1700X + RX 580 setupilla ja hintaa tuli sen 600+ € kuitenkaan kriittisten osien laadusta ja päivitysvarasta tinkimättä.

Edellämainittua kahta osaa lukuunottamatta kaikki tuli uutena ja mun mieliksi edellämainittujen hinnat oli valmiiksi poljettu maihin, koska AMD:n jatkuvat alennukset vanhempiin prossuihin ja porukan into päivittää uutta rautaa jo omistamalleen alustalle.

Saa nähdä pääseekö jo seuraavana black fridaylla laittaa R5 4600(x) tai R7 4700(x) prossua kehiin, ens vuonna sit varmaan käytettynä nopeempaa näyttistä. On se hienoo kun on valinnanvaraa, eikä tarvii kerralla lyödä tonneittain rahaa tiskiin, tai laittaa aina koko kone kerralla vaihtoon, jos haluu hypätä sen 3 prossusukupolvea eteenpäin päästäkseen rajumman suorituskyvyn makuun, vink vink vaan sinne Intelin suuntaan.

En halua missään nimessä sinänsä puolustella taaksepäin yhteensopivuuden puuttumista, mutta henkilökohtainen suunnitelma eteenpäin pelikoneen on ~350€ emo/cpu paketti yhdeksättä sukupolvea jossa emossa on päivitysvaraa i9-9900:ään asti. Sitten kun seuraavaa päivitystä siitä eteenpäin tarvitsee niin luultavasti DDR5 on jo sopivissa hinnoissa ja uutta emoa kaipaa taas joka tapauksessa.

Eli omalla kohdalla AM4 alustalle siirtymisestä olisi tod.näk. nolla euroa etua ja ainut hyöty olisi suurempi teoreettinen moniydinperformanssi jolla ei tässä kohtaa ole merkitystä kun kyse on pelikoneesta jolla ei juuri muuta tehdä.

Pointtina lähinnä siis se että vaikka taaksepäin yhteensopivuus on hieno juttu, ei se todellakaan ole mikään jumalan lahja jolla säästää joka vuosi tuhansia euroja. Parhaimmillaan sillä säästää (keskimäärin) 200€ joka kolmas vuosi niin kauan kuin tuki jatkuu. Eli AM4:n kohdalla (julkaisu 2016) tämä on realisioitunut kerran ja luultavasti realisoituu toisen kerran ennenkuin DDR5 pakottaa hankkimaan uuden (jos ei halua jättäytyä kehityksen kelkasta liian kauas siis).

Pikkusen meni minä minä jutuksi nyt kyllä tämä hommasi. Ihan faktuaalisesti sillä on hurja ero jos tarvitsee vaihtaa emolevyä vain kun muistit vaihtuu ja oikeastaan ei edes vielä silloin. Jos nyt olet ollut sinä aikana koneiden parissa kun on siirrytty DDR:ään, saati DDR2, DDR3 ja DDR4 ei uusilla alustoilla ole muistista saanut alussa käytännössä mitään eroa. Varsinkin uudet kammat tulee yleensä aina törkeillä hinnoilla varustettuna ja todella löysillä latensseilla. Vasta myöhemmin tulee nopeampia muisteja kohtuullisilla hinnoilla ja kireämmillä asetuksilla. Vanhat teknologiat on joka kerta olleet jopa nopeampia kiitos suht korkeiden kellojen ja tiukkojen latenssien. Se, että juurikin sinä olet jo ostanut jonkun just määrätyn Intel emolevyn ei vastaa todellista tilannetta. Todellinen tilanne on se, että noita vanhoja 1150 emoja myydään tällä hetkellä pilvin pimein kun Intel päätti haistattaa kakat kuluttajille. Sitten kun päästään keskustelemaan siitä paskasta mitä tekivät 1151 kanssa niin ollaan jo syvissä vesissä.

Niinpä niin. Itsellä oli alunperin suunnitteilla 2 upgradea tähän X370 alustaan, mutta nyt sitten paskan osuessa tuulettimeen (kassastusmiehen vasara meni kakkosauton pohjasta läpi) jääkin yhteen. Eli odotellaan Zen3:n tuloa. Siltikään en pidä kiirettä Zen4:n tai mitä nyt Intel sitten tarjoaa DDR5 aikaan, juurikin mainitsemistasi syistä. Menee liene ~2v kunnes DDR5 hinnat laskee ja nopeudet/lantessit kirivät järkeville tasoille.

Pidän erittäin positiivisena AMD:n tapaa pitää alustaa pitkään hengissä. Edellinen pata oli 3770k ja sen kanssa toki jäin S1155 jumiin kunnes vaihdoin koko paketin pois.. jos olisin ostanut 47xx niin sama homma mutta S1150 kanssa.. Ja sitä uudemmilla sitten keinotekoinen piirisarjayhteensopimattomuus..

Ihan vähässä kummassa en Inteliin koske lähiaikoina!

Hankala olla menemättä jos nimenomaan peilaa oman kokemuksensa kautta geneerisiä väitteitä

Kuten melko selkästi tuossa sanoin ei ollut tarkoitus implikoida että yhteensopivuuden rikkomisessa olisi jotain hyvää tms. vain tuoda esiin että usein sillä vaan ei ole mitään väliä kun uusi lankku on muutenkin tarpeen hankkia ja normaali päivitystahti on aika hidas teknologian kehitykseen verrattuna.

Ja vaikka olisitkin ostanut 2016 erittäin hyvän AM4 lankun joka pystyy ajamaan 3950X:ää tuosta vaan ja kestää sen 10 vuotta käyttöä, niin kun vuonna 2026 DDR5 on sopivissa hinnoissa, olet säästänyt 60 euroa per vuosi (aiemmin mainittu 200€ lankku joka kolmas vuosi, minkä luulisin olevan keskiverto päivitystahti). Kutsukaa porvariksi mutta omaan korvaan kuulostaa melko laimealta säästöltä vuositasolla kun taas joidenkin puheista saa välillä vähän erilaisen käsityksen.

On toki tilanteita joissa samaa lankkua pystyy käyttämään pitkäänkin usean päivityssyklin läpi, ja silloin yhteensopivuus on loistohomma. Onkin mielenkiintoista nähdä miten jatkossa näiden käy kun AM4 alkaa siirtyä historiaan, esim kuinka kauan vielä valmistetaan AM4 emoja saati sitten millä ominaisuusvalikoimalla.

Jotenkin tuntuu siltä että ainakin jonkun aikaa tullaan näkemään noita rinnakkain uuden kannan kanssa, AMD:n tämänhetkinen raketoiminen markkinoilla takaa varmaan uusienkin AM4 lankkujen kysyntää hyväksi aikaa.

Ennen Zen-aikaa esim. Intel 2700k -> 7700k ei kovin merkittävää kehitystä tapahtunut 6 vuodessa. Niin minimaalinen ero, varsinkin stock-kelloihin, jos vanhan oli jo kellottanut ja vanhaa sai ihan tuhnujäähylläkin tuosta vaan 5-10% korkeampiin kelloihin. Näen ainakin itse niin, että AM4-kannan säilyvyydessä on se hyvä, että ihan jo 1-2 generaatiota uudempi CPU tuottaa sen 100-300% lisää tehoa sopivasti skaalautuvaan käyttöön ja peleissä voi mennä jonkin aikaa, että saavat enginet optimoitua niinkin monelle säikeelle eli speeduppia odotettavissa myöhemminkin. Lisäksi muistikammat voi jossain kohtaa tuplata, jos on palojen koot valinnut sopivasti aluksi. Eli päivityspolulla ehkä häviää vähän (peli)tehoissa ihan uuteen nähden, mutta lisätehoja saa aika merkittävästi CPU-vaihdolla ja muita osia täydentämällä. Tekee jo monelle houkuttavaksi ja kannattavaksi. Vaikea perustella, miksi kuluttajalle edullinen asia olisi huono.

Tämä on tietysti aina hieman vaikea ennustaa etukäteen mutta omalta kokemuspohjalta voin sanoa että 2600K oli kohtuu pitkäikäinen sijoitus. Siitä hyppäsin 1700X ja nyt 3900X alla.

Eli teoriassa jos olisi ollut järkevä ja miettinyt vaan ns. parasta mahdollista sijoitusta olisi pyörinyt tuolla 2600K kokoonpanolla ja ostanut tarjouksesta Jimm’s:tä nykyisen emon silloin kuin sen nytkin ostin eli Asus Crosshair VI Hero X370 + 2x 16Gb muistikampaa jääden odottelemaan tulevaa toivottavasti "halpaa" 4950X tms 16-ydin/32-säie prosessoria ja luottaen siihen että se riittää seuraavat ~10 vuotta…

Enkä kokisi että siinä jäisi "liian kauas" kehityksen kelkasta. Oikeastaan vieläkin pystyisi pelaamaan 16Gb muistia ja 2600K prosessorilla. Kunhan näytönohjainta on päivittänyt (useammankin kerran) ja ehkä näyttöä ellei tyydy 22-24" 1080p TN monitoriin 2600K julkaisiajoilta…