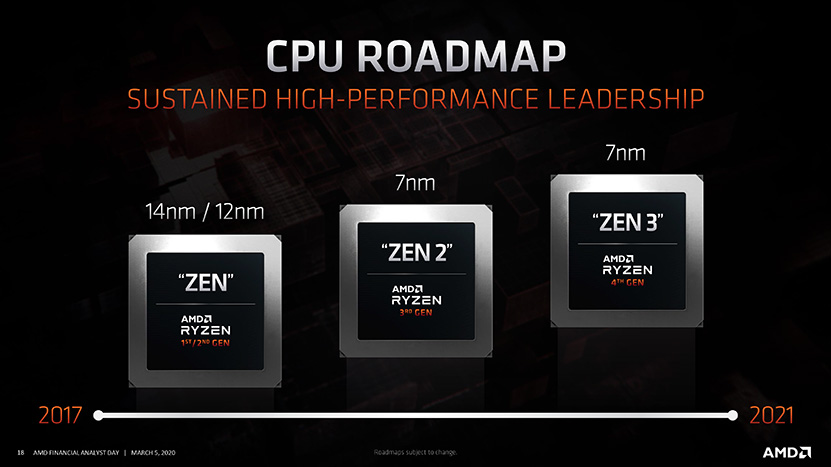

AMD:n odotetaan julkaisevan vielä kuluvan vuoden aikana uudet Zen 3 -arkkitehtuuriin perustuvat prosessorit. Ensimmäisenä linjalta ovat tulossa ulos Milan-koodinimelliset Epyc-palvelinprosessorit ja Vermeer-koodinimelliset Ryzen-prosessorit.

DRAM Calculator for Ryzen ja ClockTuner for Ryzen -sovelluksistaan tunnettu Yuri ”1usmus” Bubliy on nyt twiitannut uusia tietoja tulevista Ryzen-prosessoreista. 1usmusin mukaan yksi Zen 3:n uusista ominaisuuksista on nimeltään Curve Optimizer, mikä mahdollistaa prosessorin Boost-toiminnon konfiguroinnin käyttäjän toimesta. Lisäksi kaikki prosessoriytimet ovat nyt ylikellotettavissa toisistaan riippumatta.

AMD tulee 1usmusin mukaan myös laajentamaan tuotekirjoaan tuomalla markkinoille 10-ytimisen Vermeer-prosessorin, kun nykyisessä tarjonnassa 8-ytimisistä hypätään suoraan 12-ytimisiin. Kolmas paljastus koskee puolestaan Infinity Fabric -väylää, jolle ollaan tuomassa ilmeisesti lisää jakajia, mitkä tulevat puolestaan mahdollistamaan aiempaa hieman korkeammat muistikellotaajuudet.

1usmusin mukaan kaikki yllä mainittu tieto on luettavissa mistä tahansa AMD:n emolevyn BIOSista, mikä perustuu uuteen AGESA 1.0.8.1 -versioon.

Lähde: 1usmus @ Twitter

Mistä tämä rajoite tulee? 3300Xn 4+0 on toki erikoistapaus koska toinen CCX on kokonaan pois käytöstä, mutta viilaten pilkkua siinä ei ole saman piirisen sisällä CCX lohkoissa sama määrä ytimiä.

Ihan yhtä turhaa olkiukkoilua ja viilaamista kuin aiempikin viittauksesi 3300X:ään. Mutta alleviivataan nyt että siis jokaisessa aktiivisessa CCX:ssä pitää olla sama määrä ytimiä aktiivisena.

7-ytimisestä tulee mulle mielleyhtymä, että se on B-tuote. Tottunut itse parillisiin lukuihin ja samoin kait pelien kehittäjät. Jos semmoista taka-ajatusta ei olisi, koittaisin myyjän housuissa myydä sen pois mieluummin 7-ytimisenä kuin 6-ytimisenä.

"Liian" hienojakoinen segmentointi voi olla suhteellinen käsite. Olin TPU:n gpu tietokannasta katsovinaan, että Asusilla on ollut myynnissä 16 kpl erilaista rtx 2060-korttia jo pelkästään.

IMHO täysin päin vastoin. Se maksimikelloinen 8-ytiminen on se linjaston paras peliprossu, sille on hyvin selkeä käyttötarkoitus.

10-ytiminen sen sijaan on enemmän vaan käytännössä cripplattu versio 16-ytimisestä jota myydään että on halvempi tuote laittaa siihen väliin, pelisuorituskyky yleensä huonompi kuin 8-ytimisellä

Jos halutaan oikeasti suorituskykyä niihin hyvin rinnakkaistuviin hyötysoftiin, sitten halutaan se 16-ytiminen. Ja 10-ytiminen on optio vain jos tähdätään tähän ja ollaan köyhiä

Joo tämä näytönohjainvalmistajien touhu on kyllä ihan käsittämätöntä. Oletan että tässä on se ajatus, että noiden erilaisten jäähyviritelmien toteutus ei paljoa maksa, ja että suurimmalle osalle ostajista on merkitystä vain sillä, että mikä näytönohjainpiiri siellä on. Sen takia kaikki käyvät joka tapauksessa kaupaksi. Osa tietysti valitsee tarkemmin.

Ne chipletit testataan ja valikoidaan ennen kuin niitä juotetaan io piirien kaveriksi piirilevylle. Kolmen ytimen prossuja tulee linjastolta ulos n. 0%. Suurin osa virheellisistä prossuista joita voidaan vielä käyttää on sellaisia joissa vain yksi ydin on rikki, siksi olisi järkevää 6 ytimisten sijaan alkaa myymään nyt 7 ytimisiä kun tällä kertaa se on mahdollista. Se pieni määrä aidosti 6:lla toimivalla ytimellä olevia chiplettejä voidaan myydä premiumilla 12 ytimisinä prossuina.

Henkilökohtaisesti veikkaan että ulos tulee 7, 8, 10, 12, 14 ja 16 ytimiset mallit alkuun ja 6 ytimen jämämallit sit joskus myöhemmin 3100:n tapaan. Näin saadaan ydinsotaa nostettua taas pykälällä ylöspäin ilman kuluja AMD:lle.

Ongelma vaan että tähän mennessä niillä maksimikelloilla ei oo juurikaan eroo ollu halvimman ja kalleimman 8-ytimisen välillä. Eli käytännössä erot 8-ytimisten prossujen välillä on lähinnä ollu placebo-vaikutusta. Ja koska käytännön erot 8-ytimisten välillä on ollu melko lailla olemattomat, edelleen sen 800X:n siirtäminen 10-ytimiseks antais edes jonkunnäkösen oikeutuksen kyseisten SKU’itten olemassaololle. Olkoonkin erot pelaamisessa sitten mitä luokkaa tahansa yhden ja kahden CCD:n prossujen välillä, 10-ytiminen tulis oleen joka tapauksessa tietyissä käyttökohteissa se tehokkaampi valinta. Se että jäiskö ko. SKU edelleen ns väliinputoojaks on sitten toinen juttu, mutta tosiasia on se että jos 4800X tulee edelleen oleen 8-ytiminen prossu jolla mahdollista saavuttaa sen 25Mhz enemmän IF-kelloja ja 50Mhz enemmän huippukelloja linjaston halvimpaan 8-ytimiseen verrattuna, ei noilla prossuilla edelleen tuu oleen minkäänlaista järkevää käyttötarkotusta. Esim. 3700X:n ja 3800X:n julkasuhinnoilla oli sen 70 taalaa eroo, tuo hintaero olis ollu _hieman_ paremmin käytetty esim. pykälää tehokkaampaan näytönohjaimeen.

Joten sille 10-ytimiselle "köyhien 4950X:lle" tod näk löytyis enemmän yleisöö ja jos ei muuta niin ihan käytännön eroja 8-ytimisiin verrattuna, että tuon SKU’n julkasu voitais perustella.

No mistä rajoitus tulee? Heikki esitti että kyse olisi käyttöjärjestelmän vuorontajan toteuttamisesta. Kuulostaa järkevältä mutta ainakin minua kiinnostaa mikä siinä on se varsinainen ongelma. Alkaen vanhoista opteroneista joissa NUMA ja linkkimatriisin aiheuttamien viipeiden kompensointiin tarvittiin yksi softaosasto Dresdenissä on AMDllä ollut käyttöjärjestelmän suunnasta katsottuna haasteellisia rauta-arkkitehtuureita. Niitäkin on käytetty ja tuettu niin Linux kuin Windows puolella. Kaipasin siis vastausta siihen miksi teknisesti ottaen olisi vaikeaa tukea piirisiä joissa on eri määrä ytimiä.

Päätellen solvauksen määrästä vastausta ei kannattane odottaa.

Kiva, että sinä tiedät AMD:n saanneista noin paljon, oliko ihan mutu vai oliko tälläiselle väittelle jokin lähdekkin olemassa?

Ei niitä varmaan ole vaikea tukea siitä näkökulmasta että niillä saisi softaa ajettua. Ongelmat tulee siitä että softat ei tiedä tuosta mitään ja esim. eri kakkumääriä ei osata optimoida eri sovelluksille. Eli siis suorituskyky voi olla melko sattumanvaraista jos verrataan vaikka 5+5 ja 2+8 prossuja keskenään ja todennäköisesti scheduler ongelmien takia toi 5+5 vie ja 2+8 vikisee. Tämän lisäksi toki noita 2 ytimisiä piirejä tulee tehtaalta n. 0% ja jo toi 5 ytiminen kuulostaa todella oudolta.

Tämähän se on tällä hetkellä heikompi inteliin verraten…ja vähän ghz myös.

Saannit on TSMC:n mukaan hyvät ja virheet tulee kiekoille satunnaisiin kohtiin. Ei tässä sen kummempia tietoja vaadita. On melko epätodennäköistä että kiekon 20 virheestä vaikka 7 osuu samalle chipletille.

Eli siis mutuilet ja väität kuitenkin mutuasi faktaksi, ei jatkoon.

Johan selitin tämän jo moneen kertaan

Kyse ei ole vain toteutuksen ongelmasta vaan ihan periaatteellisesta ongelmasta siinä, että mitään järkevää logiikkaa sille, miten sen pitäisi toimia ei ole

Ihan turha puhua "toteutuksesta" ilman hajuakaan sepeksistä siitä, mitä sen toteutuksen pitäisi tehdä.

En mutuile. Noilla netistä löytyvillä saantosimulaattoreilla voi helposti laskea, että jotta tollaisia kolmen ytimen siruja tulisi ulos edes yksi per kiekko, niin ehjiä piirejä ei tulisi ulos käytännössä ollenkaan. Tämä on fakta. Lisäksi tiedämme että AMD jo nyt myy täysiä piirejä melko edullisesti ja verrattaen isoja määriä, niin ei ole realistista olettaa että ne saannot olisi niin paskat että noita kolmen ytimen piirejä tulisi ulos edes yhden käden sormilla laskettavaa määrää koko kuukausitilauksesta.

Sinä väitit, että 0% ja, että suurin osa siruista jotka rikki 7 ytimisiä. Laita nyt faktaa tiskiin. Ei mitään mutua. Jään odottelemaan, hengitystäni en sinun paskanpuhumisen kanssa ala pidättämään.

Sanoin että noin 0%.

7 ytimisiä rikkinäisistä on todennäköisyyksien mukaan ehdottomasti suurin osa, sillä virheet tulee satunnaisesti sinne kiekolle ja virheitä on kiekolla tälläisillä hyväsaantoisilla prosesseilla huomattavasti vähemmän kuin sinne mahtuu chiplettejä. Näiden seikkojen takia on huomattavan paljon todennäköisempää että rikkinäisissä piireissä on vain yksi toimimaton ydin. Voin illasta vielä kirjoittaa auki todennäköisyysyhtälöt aiheesta jos sua oikeasti aihe kiinnostaa.

Edelleen odotellaan faktoja, yhtään linkkiä ei ole näkynyt, onko sulla nyt niitä laittaa vai edelleen vedät mutua ja väität faktaksi? Saannot on joka firmalla todella kovia yrityssalaisuuksia niin pistä nyt meille kaikille sun luvut tiskiin, kun kerran väität tietäväsi. Minä kyllä olen lukenut TSMC:n osakeyhtiön viralliset tiedotteet omistajille niistä saannoista. Ne ei todellakaan ole mitään mitä väität, mutta kun kerran tiedät paremmin niin lukuja ja linkkejä tiskiin ja sitä simulaattoria kanssa, sen varsinkin haluan nähdä.

Matematiikka ei ole mutua.

Eli sulla ei ole mitään faktoja ja puhut paskaa, muta et kykene edes myöntämään sitä. Upea keskustelija.

TSMC on ihan julkaissut eri prosessiensa saannot jossain pressitilausuudessaan. Ei tarvitse arvailla: TSMC 5-Nanometer Update

Käytännössä luvut näyttäisivät siltä että täysien zen2 chiplettien saannot on noin 94%. Lasken illemmalla auki että kuinka paskat niiden saantojen pitäisi olla, jotta 7 ytiminen prossu ei olisi todennäköisin rikkinäinen piiri. Zen3 chiplettien tarkkaa kokoa ei ole vielä saatavilla, mutta tolla zen2 koolla päästään varmaan tässä väittelyssä tarvittavan tarkalle tasolle.

Mitä tekemistä zen 2 on zen 3 kanssa? Luonnnollisesti saannit paranee ajan kanssa. Joko saisin sen simulaattorin? Väitit sellaisen olevan olemassa.

Tuossa yksi monesta: Die Yield Calculator

Oikein malliesimerkki siitä, että kun itse on pihalla kuin lumiukko ja tykkää postata paskaa, niin olettaa automaattisesti että muut toimii samoin, ja syyttää muita tasan siitä mihin itse syyllistyy.

Pomk oikeasti tietää mistä puhuu, toisin kuin sinä.

[/QUOTE]

Eihän toi TSMC:n prosessiin liity mitenkään.

Ne on suunnilleen saman kokoiset ja ja käyttävät TSMC:n mukaan käytännössä yhtä hyvillä saannoilla olevaa prosessia. Kyseiset parametrit on täysin riittävät tämän typerän väittelyn osalta.

Tuolta löytyy se simulaattori:

Die Per Wafer Calculator –

caly-technologies.com

Ne on suunnilleen saman kokoiset ja ja käyttävät TSMC:n mukaan käytännössä yhtä hyvillä saannoilla olevaa prosessia. Kyseiset parametrit on täysin riittävät tämän typerän väittelyn osalta.

Tuolta löytyy se simulaattori:

Die Per Wafer Calculator –

caly-technologies.com

Mitä featureita tosta sinun mielestäsi puuttuu?

Nuo käy ihan minkä tahansa prosessin saantojen simulointiin

Miten ne käy jos TSMC itse viime joulukuussa sanoi, että 5nm saannit on 50% nykyään ne on jossain 75+% Ehkä 90% ei tolla laskurilla voi laskea kuin teoreettisen maksimisaannin. Mitään tekemistä ei noilla ole oikeiden saantien kanssa.

Voi hyvä ihme nyt sentään. Lopeta tahallinen väärinymmärtäminen, kyse on tilastomatematiikasta kuten sinulle on jo erikseen alleviivattu aikaisemminkin.

Ei edes tilastomatematiikkaa, vaan klassista todennäköisyysmatematiikkaa.

Mitä tarkoitat sillä että saannit on jollain prosessilla vaikka 50%? Minkä kokoisella piirillä se on mitattu?

Minä kerron vain sen minkä TSMC on itse julkistanut. Minä, toisin kuin täällä aika moni, en tiedä mitkä on heidän oikeat saannit, koska se on yrityssalaisuus. Yield eli saanti kun viittaa todellisiin lukuihin, mihin lasketaan ne oikeat sirut mitkä toimivina tulee toisesta päästä linjaa testattuina ulos. Niitä sitten verrataan matemaattisiin malleihin ja katsotaan kuinka helvetin kaukana ollaan. Tarkasti ottaen ne tehdään vielä prosessikohtaisesti kerros kerrokselta, että löydetään ne viat. Mutta koska kyse on tilastomatematiikasta ja kaikki mitä saanneista opuksissa ja tuotantotaloudessa kerrotaan ei pidä paikkaansa, niin mennään matemattisilla malleilla sitten. Täällä on kuitenkin asiantuntijat liikkeellä.

Laittaisitko linkkiä tuohon viittaamaasi dokumenttiin? Siis jossa TSMC kertoo saanneistaan että ne on vaikka 50%.

Oleppa hyvä.

Report: TSMC's 5nm Process to Power Zen 4, Reportedly Already at 50 Percent Yield

http://www.tomshardware.com

Huhua esität faktana? Missä on TSMC:n dokumentti?

Ei minulla ole mitänä syytä epäillä isojen uutistalojen toimituksia.

Ihan wikipediasta löytyy joulukuulta sitten virallista tietoa, että:

Today at the IEEE IEDM Conference, TSMC is presenting a paper giving an overview of the initial results it has achieved on its 5nm process.

For the combined chip, TSMC is stating that the chip consists of 30% SRAM, 60% Logic (CPU/GPU), and 10% IO. In that chip are 256 mega-bits of SRAM, which means we can calculate a size. A 256 Mbit SRAM cell, at 21000 nm2, gives a die area of 5.376 mm2. TSMC states that this chip does not include self-repair circuitry, which means we don’t need to add extra transistors to enable that. If the SRAM is 30% of the chip, then the whole chip should be around 17.92 mm2.

For this chip, TSMC has published an average yield of ~80%, with a peak yield per wafer of >90%.

myönnetään ettei tuotantoteknisesti ole tolkkua toteuttaa kahden eri ydinmäärän piirisillä toteutettua suoritinta kun tasajaollakin voidaan mennä. Minusta on vain outoa että jos Windows osaa hyödyntää sekä AMD, että Intel prosessorilla nopeinta ydintä tai ytimiä jo nyt, mitä ongelmia se aiheuttaisi että ytimet ovat fyysisesti eri piirisissä. Olen tähän asti kuvitellut että suorittimen sisäinen rakenne on käyttöjärjestelmälle läpinäkyvä, mutta ilmeisesti olen sitten väärässä.

OK. Väitit että saannot on ollu jouluna 50%, mutta nyt ne on ollu äskeisen viestisi mukaan (joka ihan oikeasti on TSMC:n antamiin tietoihin perustuvaa) ollut jouluna 80 – 90%. Päätä jo. Lisäksi haluaisin tietää että miksi tykkäät vängätä tosta 5nm prosessista tässä ketjussa?

Koska se on lähinnä vastaavaa prosessia kuin mahdollinen Zen 3 7nm+ jossa EUV mukana, eli täysin uusi erillinen prosessi. Tosta 7nm+ missä EUV jos AMD sitä käyttää prosessista kun on nihkeästi informaatiota tarjolla. Eikä edes siitä, että millä prosessilla Zen 3 tullaan tekemään AMDhän veti sen + merkinkin pois materiaaleistaan.

Mutta 7nm+ EUV:lla on jo massatuotannossa, siinä missä 5nm oli ainakin vielä äsken riskituotannossa. Eikö olisi järkevämpää joko verrata muihin massatuotantokelpoisiin prosesseihin, tai sitten siihen mitä TSMC sanoo? "TSMC’s N7+ is their first process technology to adopt EUV for a few critical layers. N7+ entered mass production last quarter (Q2). TSMC says they have demonstrated similar yield to N7."

N7 prosessin saannot taas on julkista tietoa, 0,09 defects per cm^2:

Tuolla 0,09 luvulla saadaan noin kuusi virhettä per sata zen2 chipletin kokoista chiplettiä.

Niin ja huhuissa oli uuden iPhonen kohdalla, että siksi ei tehty 7nm+ koska saannit putosi. Edelleen ne on yrityssalaisuuksia ne oikeat luvut.

Huhut < TSMC:n esittämät tiedot joilla se myy prosessiaan potentiaalisille asiakkailleen. Uusi iphone tulee 5nm prosessilla.

Tuohon päälle:

Sen yieldit ovat paremmat kuin ne olivat N7:lla samassa kohtaa kehityskaarta. Alle 0,5 virhettä / cm^2 on kuulemma jo hyvällä tasolla, TSMC:n 5nm on tällä hetkellä selvästi alle sen, 0,1-0,11 virhettä / cm^2

‘Better Yield on 5nm than 7nm’: TSMC Update on Defect Rates for N5

http://www.anandtech.com

Ne eivät ole mitään tarkkaan varjeltuja yrityssalaisuuksia, yhtiöt kertoo varsin tarkasti saannoistaan jopa ihan julkisesti.

Jep. Ainoa poikkeus on intel, jolla ei ole tarvetta markkinoida prosessiaan, sillä se ei ole kyseisen firman tuote.

ainakaan vielä…..

Kyllä ne todellakin on tarkkaan varjeltuja salaisuksia, esim. tuossa 7nm+ vs 7nm ei kerrottu, että missä vaiheessa kehityskaarta eikä, että verrattuna miten. Esim. AMD:ltä on vuotanut, että yieldit olisi ollut 70% alussa. Kyllähän tuolla varmasti tuote markkinoille saadaan ja tuotantoon, mutta ei noi luvut ole mitään kummosia jos nyt vertaa matemaattisiin malleihin. Miksi näitä vuotaa sitten joku salainen tietolähde jos kerran täysin on julkisia?

AMD Zen 2: Production yields for Ryzen 3000 Dies at 70 percent

http://www.guru3d.com