Aiemmin uutisoimassamme RansomEXX:n kyberhyökkäyksessä Gigabyteltä varastettiin jopa 112 gigatavua dokumentteja, joista osa sisälsi AMD:n, Intelin ja AmericanMegatrendsin salassapitovelvollisuuden alaisia dokumentteja. Nyt dokumentteja on myös julkaistu ja niiden mukana pääsi julki AMD:n tukidokumentteja tuleville Zen 4 -arkkitehtuurin Genoa-prosessoreille. Genoa-prosessorit sopivat uuteen LGA-tyyppiseen SP5-prosessorikantaan.

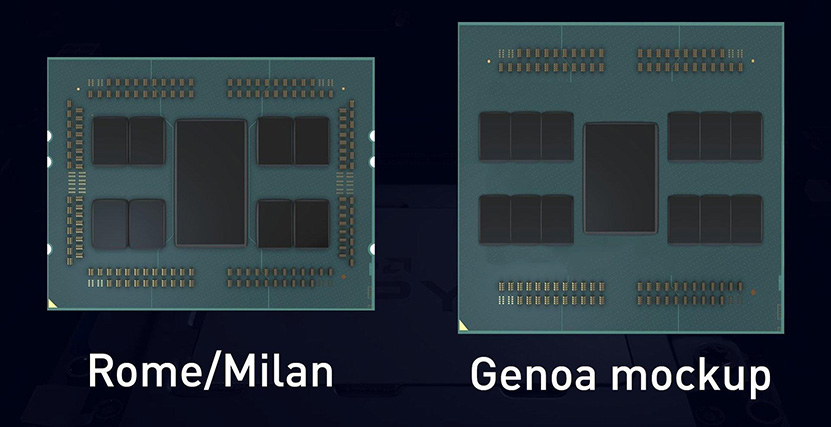

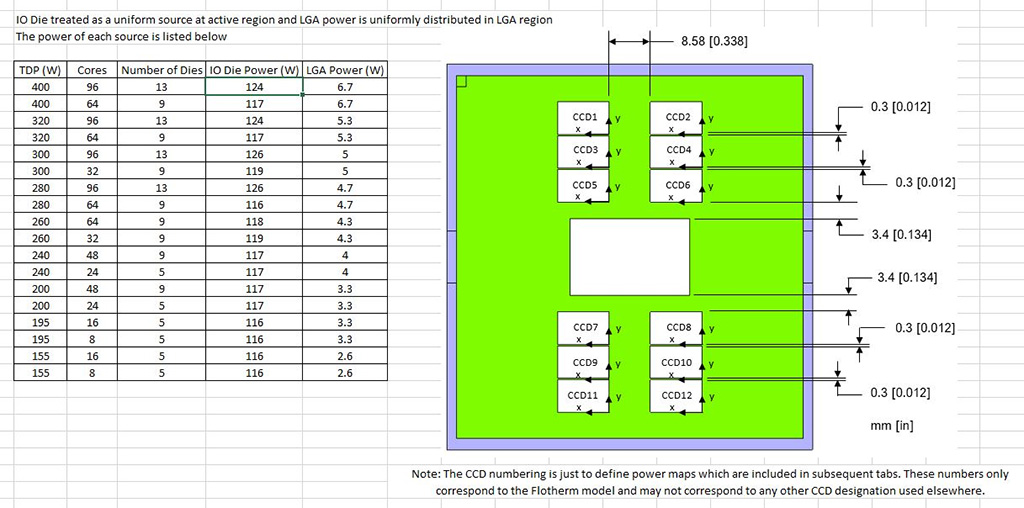

Vuotaneen 0.71-version tukidokumentit on päivätty kuluvan vuoden heinäkuulle. Ne vahvistavat samalla lukuisia huhuja, kuten maksimissaan 12 prosessorisirua. Prosessorisirujen perusrakenne pysyy tuttuna, vaikka arkkitehtuuri muuttuukin; kahdeksan Zen 4 -ydintä, jotka jakavat yhteisen L3-tason välimuistin. Yhdessä Genoa-prosessorissa voi olla siis nyt yhteensä 96 Zen 4 -ydintä, jotka tukevat vuotaneiden dokumenttien mukaan nyt myös AVX-512-laajennoksia. Vaikka Zen 4 -prosessorisirut valmistetaan TSMC:n 5 nanometrin valmistusprosessilla, niiden fyysinen koko on lähellä nykyisiä Zen 3 -ytimiä.

Uusi IO-siru sisältää nyt 12/24-kanavaisen DDR5-muistiohjaimen ja se kuluttaa pahimmillaan jopa 75 % prosessorin TDP:stä. 12/24 selittyy sillä, että DDR5-muisteissa kulkee yhden 64-bittisen (72-bit ECC:llä) sijasta kaksi 32-bittistä (40-bit ECC:llä) kanavaa samaan kampaan. Kanavista puhutaan kuitenkin vanhasta tottumuksesta kuin ne olisivat yhtä. Kunkin kanavan tai kanavaparin jatkeena voi olla tuttuun tapaan kaksi muistipaikkaa. IO-sirun valmistusprosessi ei ole tällä hetkellä tiedossa, mutta se tuskin on sama TSMC:n N5, kuin prosessorisiruissa.

Genoan maksimi TDP-arvo kasvaa aiempiin sukupolviin nähden selvästi. Siinä missä Zen 3 -sukupolven Milan-prosessoreiden TDP oli korkeimmillaan 280 wattia, yltää Genoa peräti 400 wattiin asti. Pienimmillään TDP-arvo on 155 wattia ja IO-siru kuluttaa prosessorin konfiguraatiosta riippuen 116-124 wattia. Prosessorin piikkikulutus voi nousta kokonaisuudessaan jopa 700 wattiin maksimissaan yhdeksi millisekunniksi ja 440 wattiin 10 millisekunniksi.

Vuodossa on lisäksi varmistunut roadmapeissakin näkynyt Chagall-koodinimi tuleville Zen 3 Threadripper-prosessoreille.

Lähde: ComputerBase

Se, että muutkin ovat tehneet niin, ei mielestäni ole aivan riittävä peruste.

Siinä vaiheessa kun se on levinnyt ni turha säästellä.

Ainakin noiden kolmella jaollisten kanavamäärien jatkoksi saisi myös tri-channelin, mutta ei kai sitten. Mietin vaan, kun semmoiset on tehty, niin niille saisi paremmin kolmen kanavan konfiguraatioita..

Tuo IO-sirun korkea virrankulutus on kyllä ikävä lieveilmiö chiplet rakenteesta. Toivottavasti siihen saadaan joku muutos tulevaisuudessa, muutoin Intel jyrää yli virrankulutuksessa huonommallakin 7 nm nodellaan (aka 10+++), ellei puhuta core intensiivisemmistä / jatkuvista työkuormista.

Onkohan niissä paljonkin isompi IPC jos kerran fyysinen koko ei pienene vaikka prosessi pienenee? AVX-512 ainakin nostaa kompleksisuutta. Toisaalta tuo fyysinen koko taitaa olla edelleen sellainen "sweet spot" sen osalta että tuoreesta prosessista huonoilla saannoilla saadaan järkevä määrä toimivaa rautaa pihalle. Liian pieni silppu aiheuttaisi omat haasteet ja liian isot palaset mahdottomia valmistaa. Mitä sitä toimivaa muuttamaan.

Onko Intel tämän ongelman ratkaissut vai miksi se on niin paljon parempi heillä?

Tuon IO-sivunhan voisi siis valmistaa myös tuoreella paremmalla prosessilla, mutta sen hyöty jäisi aika mitättömäksi. IO-sirulla on hyvin paljon sellaista joka ei vain skaalaudu vaikka se tehtäisiin millä prosessilla. Siksi se tehtiinkin erilliseksi siruksi.

Intel voi hyvinkin valmistaa sen omansa hieman paremmalla nodella, koska heillä on tuotantokapasiteettia reilusti, varsinkin vanhemmilla prosesseilla. AMD taas haluaa todennäköisemmin käyttää hieman vanhempaa nodea ja siten saada sen sirun/prosessorin halvemmaksi. Pieni idle-tehokulutuksen kasvu vs. paras mahdollinen prosessi ei ole serveriraudassa niinkään ongelma. Ongelma se olisi jos laskenta/prosessointi alkaisikin kuluttaa enemmän energiaa. Ei noita ole tarkoitus idlessä pitää.

I/O sirun tehonkulutus tulee aika suurelta osin sellaisesta asiasta johon valmistustekniikka ei valitettavasti vaikuta.

Nimittäin I/O sirun täytyy "ajaa" ulkoisia väyliä suurella nopeudella. Ja se ei valitettaasti onnistu ilman verrattain suurta sähkötehoa. Kuparijohtimilla on kapasitanssi jota täytyy varata ja purkaa jokaisella reunalla.

Osa siitä on prosessoriytimien ja I/O lastun välisen väylän ajamista mutta siihen syssyyn mahtuu sitten PCIe ja DDR5 jne.

Tarkoitin, että käsittääkseni myös Intel on siirtymässä chiplet prossuihin (vai joko se on?), niin miten heidän ratkaisunsa on päässyt eroon tuosta suuresta IO-piirin kulutuksesta kuten tuossa ylempänä kerrottiin?

Mitäpä luulet miksi sapphire rapidsin tdp on siellä 4-500W maastossa huhujen mukaan…

Edes Intel ei mahda fysiikan laille mitään

Onkohan tuo pcie 5?

Odottelen pienellä kiinnostuksella paljonko ekan sukupolven Pcie 5 toteutukset syö sähköä vs. pcie 4.

Nelosenkin mukana tuli jo piirisarjalle tuuletin ja spekuloin että viitonen tuskin vie ainakaan sen vähempää.

Se tuuletin on ollut koko ajan suht turha ja nyky AGESAlla vielä turhempi (sama piiri edelleen, mutta uudet lankut passiivisia)

Näinhän se varmaan on. Testaan omalta osalta jos x570-P:n tuuletin joskus hajoaa ja palaan sitten asiaan

Hetken googlaamisella en saanut tolkkua onko Zen 4 pcie:n versiota vielä vahvistettu tai vuodettu "luotettavasti", työpöytä- ja palvelinprosut.

Itseasiassa nyt kun AMD lisäsi cachen määrää valtavasti IO-sirulle tulee todennäköisesti reippaasti suuremmat koherenssitaulukot jotka skaalautuvat valmistusprosessin mukana. Lisäksi tulee +50% muistiohjaimia ja IF-linkkejä jne. eli IO-sirun pysyminen kuitenkin samankokoisena kuin ennen meinannee että se tullaan valmistamaan reilusti aikaisempaa pienemmällä prosessilla.

Mutta ei siltikään sillä pienimmällä mahdollisella nodella. Tuo on toisaalta ihan hyvä että sekin tila käytetään järkevästi.

Oltaisiinkohan Gigabyteä saatamassa myyntikuntoiseen hintaan?

Meinaa vuotoja ja poweriongelmia niinpä kurssi painuu ostettavampaan hintaan.

IO sirun kulutuksessa näkee että PHY vie virtaa. DDR5 vie 64*12 PHY astetta. Jokainen IF linkki lisää asteiden tarvetta. Sinällään ihan saman kulutuksen asteet aiheuttaisivat vaikka käytettäisiin vanhaa AMD NUMA mallia.

Missä on sanottu että io-siru olisi saman kokoinen kuin ennen?

Ei missään, mutta se on varmaa että ei siitä juuri pienempääkään voi tulla tuolla IO-PHY määrällä. Nuo kun on tapana asettaa piirin ulkokehälle.

Ei, lähinnä meinasin siis sitä että sen koosta ei voi päätellä valmistusprosessia ainakaan tällä hetkellä (jos noissa jossain vuodoissa mitat olivatkin, en muista nähneeni mutta voi olla että jossain oli)

Piiirien mitat on myös vuodettu.

Juu valmistusprosessi on vähän mysteeri vielä, piirin fyysinen koko taas määräytyy lähinnä noiden PHY:iden mukaan.

Oliko missä noista vuotodokkareista (jos viitsit säästää vaivaa sen verran)?